11-Bloques Estandarizados.pdf

11-Bloques Estandarizados.pdf

11-Bloques Estandarizados.pdf

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

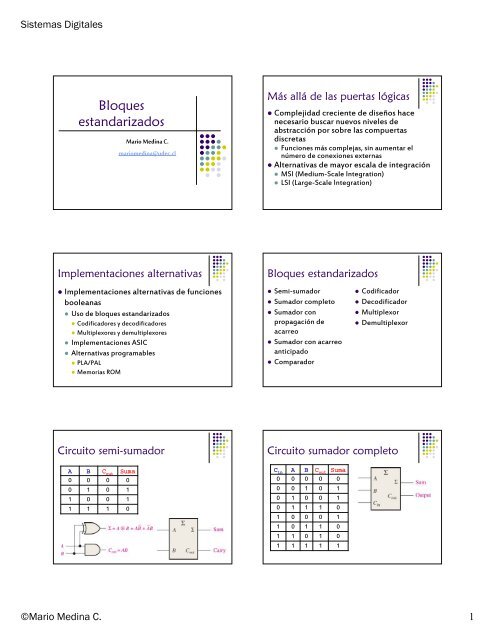

Sistemas Digitales<strong>Bloques</strong>estandarizadosMario Medina C.mariomedina@udec.clMás allá de las puertas lógicas• Complejidad creciente de diseños hacenecesario buscar nuevos niveles deabstracción por sobre las compuertasdiscretas• Funciones más complejas, sin aumentar elnúmero de conexiones externas• Alternativas de mayor escala de integración• MSI (Medium-Scale Integration)• LSI (Large-Scale Integration)Implementaciones alternativas• Implementaciones alternativas de funcionesbooleanas• Uso de bloques estandarizados• Codificadores y decodificadores• Multiplexores y demultiplexores• Implementaciones ASIC• Alternativas programables• PLA/PAL• Memorias ROM<strong>Bloques</strong> estandarizados• Semi-sumador• Sumador completo• Sumador conpropagación deacarreo• Sumador con acarreoanticipado• Comparador• Codificador• Decodificador• Multiplexor• DemultiplexorCircuito semi-sumadorCircuito sumador completoA00<strong>11</strong>B0101C outSuma0 00 10 <strong>11</strong> 0C inA B C outSuma0 0 0 0 00 0 1 0 10 1 0 0 10 1 1 1 01 0 0 0 <strong>11</strong> 0 1 1 01 1 0 1 01 1 1 1 1©Mario Medina C. 1

Sistemas DigitalesCircuito sumador completoCircuito sumador completo• Construido con dos semi-sumadoresSumadores en paralelo• Sumador de 2 bitsSumador paralelo de 4 bitsSumador paralelo de 4 bits(74LS283)Retardos de propagación,74LS283©Mario Medina C. 2

Sistemas DigitalesSumador paralelo de 8 bitsSumador paralelo de 16 bits• 4 sumadores paralelos de 4 bits en cascada• Retardo de propagación aumenta linealmenteRetardo de propagación,sumador de 4 bitsSumador de anticipación deacarreo• Llamado también carry-lookahead adder• Acarreo puede ser• Generado: si entradas A y B a un sumador son 1C g = AB• Propagado: si el acarreo de entrada C in se reflejaen un acarreo de salida, lo que ocurre si almenos una de las entradas es 1 y C in es 1Cp = A + BC out = C g + C p C inAcarreos generados ypropagadosgenerado propagado propagado propagadoSumador de anticipación deacarreo©Mario Medina C. 3

Sistemas DigitalesCircuito de anticipación deacarreoCircuito comparador de 4 bits7485Circuitos comparadores encascadaCodificadores• Bloque de 2 n entradas y nsalidas• Se llama codificador 2 n -a-no de n bits• Transforma la únicaentrada activa a algúncódigo (Binario, Gray,BCD, etc.)⎧isi xi= 1y E = 1y (xk= 0∀k≠ i)z = ⎨⎩ 0 enotro casoCodificadores• Sólo una entrada puede estar activa a la vez• EntradaE esunaseñalde control, no dedatos• Habilita o deshabilita el bloque• Deshabilitación deja todas las salidas en alto obajo, dependiendo de la lógica definida para elbloqueCodificador de prioridades• Codifica la entrada de mayor prioridad queestá activa• Puede haber más de una entrada activa a la vez• Necesario establecer prioridad entre lasentradas• Salida adicional indica si no existen entradasactivadas©Mario Medina C. 4

Sistemas DigitalesCodificador de prioridades• Salida abc codifica entrada activa de mayorprioridad• Entrada y 7 tiene mayor prioridad que y 0• Salida d indica que hay una entrada activay0 y1 y2 y3 y4 y5 y6 y7 a b c d0 0 0 0 0 0 0 0 0 0 0 01 0 0 0 0 0 0 0 0 0 0 1X 1 0 0 0 0 0 0 0 0 1 1X X 1 0 0 0 0 0 0 1 0 1X X X 1 0 0 0 0 0 1 1 1X X X X 1 0 0 0 1 0 0 1X X X X X 1 0 0 1 0 1 1X X X X X X 1 0 1 1 0 1X X X X X X X 1 1 1 1 1Codificador de prioridades74LS148• 8 entradas activas bajas• 3 salidas activas bajas• HPRI: entrada de másalto valor tieneprioridad• EI: activación activa baja• EO y GS: salidas activasbajas para conexión encascadaCodificador de prioridades 16-a-4 en cascada Decodificadores• Bloque de n entradas y 2 nsalidas• Se llama decodificador n-a-2 n• Función inversa a codificador• Activa una de las salidas enfunción del valor de las entradas• Demás salidas inactivas ocomplementadas• Señales de salida mutuamenteexcluyentesz i⎧ 1 si x = i y E = 1= ⎨⎩0enotrocasoImplementación decodificador2-a-4Decodificador 3-a-8• Implementación usa 8 ANDs de 3 entradas©Mario Medina C. 5

Sistemas DigitalesEjemplo: decodificador 4-a-10para BCD 8421Ejemplo: decodificador 4-a-10•Decodificador para dígitosBCD 8421•Salidas activas bajasDecodificador 4-a-16 74LS154Decodificador 5-a-32 usandodecodificadores 4-a-16•Salidas y activación activas bajaImplementaciones alternativascon decodificadores• Implementar funciones f 1 y f 2 condecodificador 4-a-10, salida activa bajaf 1 = m 1 + m 2 + m 4f 2 = m 4 + m 7 + m 9• Reescribiendof 1 = (m 1 ’m 2 ’m 4 ’)’f 2 = (m 4 ’m 7 ’m 9 ’)’Multiplexores o selectores• Bloque de 2 n entradas de datos,n entradas de control y 1 señalde salida• También se debe añadir la señalde habilitación E• Si el bloque está habilitado, laseñal de control s seleccionauna de las entradas para ser Si E = 1dirigida hacia la salida Y = xc, c = s0s1s2©Mario Medina C. 6

Sistemas DigitalesOperación de un multiplexor2-a-1• Multiplexor 2-a-1• Escoge la entrada basada en señal de control• Z = A’*I 0 + A*I 1Multiplexores 2 n -a-1•2 n entradas•n señales de controlMultiplexor 8-a-1Multiplexor de 8 entradas74LS151• Entradas I 0 a I 7• Señales de control abcMultiplexor 16-a-1 usandomultiplexores 8-a-1Multiplexor de datosMultiplexor cuádruple conentradas y salidas de bus de4 bits©Mario Medina C. 7

A B C F0 0 0 10 0 1 00 1 0 1C0 1 1 01 0 0 01 0 1 0 01 1 0 <strong>11</strong> 1 1 <strong>11</strong>Sistemas DigitalesImplementaciones alternativascon multiplexores• Multiplexor puede implementar unatabla de verdad en forma directa• EjemploEjemplo de implementaciónF(A +2, A1,A0) = m1+ m3+ m5m6F(A, B,C) = m +0+ m2+ m6m7Implementaciones alternativascon multiplexores• Cualquier función de n variables puedeimplementarse en forma directa con un MUXde 2 n -a-1• El número de entradas a un MUX suele serlimitado• Comercialmente no se fabrican con muchasentradasImplementaciones alternativascon multiplexores• Ejemplo: implementar la siguiente funcióncon un MUX de 4-a-1F(A, B, C) = A’B’C’ + A’BC’ + ABF(A, B, C) = A’B’(C’) + A’B(C’) + AB’(0) + AB(1)Implementaciones alternativascon multiplexores• Metodología general (particionar la función)• Seleccionar n-1 variables como entradas decontrol• Variable restante se usará como entrada• Cada combinación de las n-1 variables define 2celdas de la tabla de verdad• Si la variable de entrada es constante en 0 o 1, laentradaasociadaal MUX será0 o 1• Si la variable de entrada cambia su valor, laentrada al MUX será la variable de entrada o sucomplementoImplementaciones alternativascon multiplexores• Implementar con un MUX de 8:1 la funciónF(A, B, C, D) = ∑m(0, 1, 3, 6, 7, 8, <strong>11</strong>, 12, 14)• El método es general para másvariables, pero las entradasserían función de las variablesque no se definen como decontrol• Requiere uso de bloques lógicos enlas entradas©Mario Medina C. 9

Sistemas DigitalesOtro ejemploF(A, B,C,D)=∑m(1,2,5,6,7,8,10,12,13,15)Implementaciones alternativascon multiplexores• Implementar un MUX de 8:1 con• 2 MUX de 4:1 y un MUX de 2:1• 4 MUX de 2:1 y un MUX de 4:1Implementaciones alternativas:demultiplexor• Cualquier función de n variables puedeimplementarse con un demultiplexor de nentradas de control y puertas OR• Cada combinación de entradas selectorascorresponde a un minitérmino de una función• Todas las salidas que corresponden a unminitérmino se usan como entradas a un OR quecalcula la función finalImplementaciones alternativascon demultiplexor• Implementar las siguientesfunciones con undemultiplexor de 8 salidasF(A, B, C) = ∑m(0, 2, 3, 7)G(A, B, C) = A’BC + AB’C+ ABC’Implementaciones alternativas• Circuitos integrados comerciales imponenlimitantes a número de entradas disponibles• Inclusión de entradas de control, como la dehabilitación E, permite interconectarjerárquicamente distintos bloques paraformar bloques más grandes• Un MUX de 32-a-1 puede implementarse con 4MUX de 8:1 y un decodificador de 2-a-4• Decodificador 5:32 puede implementarse con 1decodificador de 2:4 y 4 decodificadores de 3:8Fan-Out y buffers• Unasalidade compuertalógicasólosepuede conectar a un número limitado deotras entradas• Limitación de implementación• Buffer• No modifica el valor lógico de la entrada• Mejora las características eléctricas de la salida• Permite aumentar el fan-out©Mario Medina C. 10

Sistemas DigitalesFan-Out y buffers• Función buffer• F = C• Permiteconectar másentradas a lasalidaConectando salidas• No se pueden conectar directamente dossalidasBuffers de 3 estados• Buffer que aísla la entrada de la salida• Si B es 1, C = A• Si B es 0, A y C no están conectados• 3er estado es alta impedancia (Z)Buffer de 3 estados• Tipos de buffers de 3 estados• Salidas activa alta/baja• Control activo alto/bajoCircuitos con buffers de 3estados• Construyendo un multiplexor de 2-a-1 conbuffers de 3 estados• Nótese que salidas de buffers están conectadasdirectamente!• Si B = 0, D = A• Si B = 1, D = CD = AB’ + BCConstruyendo circuitos conbuffers de 3 estados• Si BD = 00, F = Z (alta impedancia)• Si BD = 01, F = C• Si BD = 10, F = A• Si BD = <strong>11</strong>, Error!• Conflicto entre las salidas• Debe garantizarse queBD nunca será <strong>11</strong>©Mario Medina C. <strong>11</strong>

Sistemas DigitalesBuffers de 3 estados comoalternativas a MUXes• Sumador de 4 bitsSum = (EnA*A + EnB*B + EnC*C + EnD*D) + E• Sólo una entrada de habilitación activa a la vezLíneas bidireccionalesutilizando buffers de 3 estados• Terminal bidireccionalconstruido con buffer deSalida3 estados• Si buffer está activo,terminal corresponde aEntradasalida del circuito• Si buffer está inactivo,terminal corresponde aentrada al circuitoEnableTerminalBus de datos bidireccional©Mario Medina C. 12