Master IST - Université Paris-Sud 11

Master IST - Université Paris-Sud 11

Master IST - Université Paris-Sud 11

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Spécialité "Electronique pour les télécommunications et les microcapteurs"<br />

<strong>Master</strong> <strong>IST</strong> – Université <strong>Paris</strong>-<strong>Sud</strong> <strong>11</strong> – Habilitation 2010-2013<br />

Parcours SECI (R&P) : l'objectif de ce parcours est de former les étudiants aux méthodes de<br />

conception et d'optimisation globale de systèmes à base de capteurs intégrés (MEMS, magnétiques,<br />

rétines optiques artificielles) où le concepteur peut intervenir à tous les niveaux de la chaine<br />

(dimensionnement du capteur, de l'électronique de conditionnement et du traitement du signal de<br />

manière à optimiser les performances globales en termes de précision, de coût et de consommation).<br />

Le fil conducteur sera la conception, la réalisation et la caractérisation d'un système de mesure<br />

intégré au cours de la formation, en s'appuyant sur la Centrale Technologique Universitaire (CTU)<br />

Minerve, le CMP (Circuits Multi projets – service de fonderie mutualisé entre différents<br />

laboratoires français) et sur les outils fournis par le CNFM (Coordination Nationale pour la<br />

Formation en Micro et nanoélectronique).<br />

Le tableau et les fiches descriptives pour ce parcours sont donnés dans les pages suivantes.

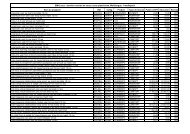

Tableau du parcours 2.3 Sytèmes Électroniques pour les Capteurs Intégrés<br />

(Finalité Professionnelle)<br />

Responsable : Hervé MATHIAS<br />

Sigle Intitulé de l’UE Sem. ECTS<br />

PhysI-J00 Remise à niveau (R&P) S0 0<br />

PhysI-C01 Intégration de Systèmes numériques (R&P) S2 4<br />

PhysI-C02 Conception de systèmes intégrés analogiques et mixtes (R&P) S1 5<br />

PhysI-J03 Processeurs et périphériques embarqués (R&P) S2 4<br />

PhysI-J04 Bus et Interfaces embarqués (P) S1 3<br />

PhysI-J05 Traitement du signal et applications sur DSP (R&P) S1 5<br />

PhysI-J06 Traitement d'image pour applications embarquées (P) S2 5<br />

PhysI-J07 Electronique des capteurs intégrés (R&P) S1 4<br />

PhysI-J08 Conception de microsystèmes (R&P) S1 5<br />

PhysI-J09 Fabrication et caractérisation de MEMS (R&P) S1 3<br />

PhysI-C20 Formation générale (P) S1 5<br />

PhysI-C21 Management de projet et projet (P) S2 5<br />

PhysI-C22 Stage (P) S2 12<br />

12/06/12<br />

2

Nom de l’UE : Intégration de Systèmes numériques<br />

Responsables : Hervé Mathias<br />

Mention : Information, Systèmes et Technologie (EEA)<br />

PhysI-C01<br />

type d’UE : CM + TP<br />

UE commune aux parcours SET et SECI(R&P)<br />

Objectifs :<br />

− Sensibiliser aux différents problèmes liés à la conception de circuits intégrés numériques (partitionnement<br />

logiciel/matériel, test…) et présenter les différentes alternatives pour réaliser des ASICs numériques.<br />

− Acquérir les méthodes de conception et d'optimisation des parties numériques intervenant au sein de systèmes sur<br />

puce (SoC) : compromis performances/taille/consommation/temps de conception.<br />

− Présenter des outils permettant l'automatisation de la conception (synthèse architecturale) et du dessin des masques<br />

(synthèse logique).<br />

Contenu des enseignements (avec nb d’heures) Cours TD TP<br />

♦ Les outils de CAO pour les systèmes sur puce :<br />

6 h<br />

− démarche de conception d’un système électronique<br />

− simulation de circuits logiques<br />

− synthèse de circuits logiques<br />

− simulation électrique<br />

− automatisation du dessin des masques<br />

− test et testabilité<br />

♦ Circuits intégrés numériques :<br />

18 h<br />

− FPGA<br />

− optimisation structurelle des circuits numériques : familles CMOS, mémoires<br />

intégrées<br />

− optimisation architecturale des performances : architectures parallèles, pipeline…<br />

− architectures faible consommation<br />

− Impact des technologies sub-micrométriques : Design for Yield<br />

♦ TP : conception et synthèse sur FPGA d'un système numérique<br />

16 h<br />

Enseignants : H. Mathias (MC), L. Lacassagne (MC), F. Thomas (Cadence), A. Mérigot (PR), M. Burlisson (Nexter<br />

Systems), X. Checoury(MC)<br />

Prérequis : Connaissance de VHDL<br />

Nombre maximum d’inscrits :<br />

Contrôle des connaissances : écrit (2/3) + TP (1/3)<br />

nb d’heures : 40 h<br />

ECTS : 4<br />

12/06/12<br />

3

Nom de l’UE : Conception de systèmes intégrés analogiques et mixtes<br />

PhysI-C02<br />

Responsables : Ming Zhang<br />

type d’UE : CM /TD/TP<br />

Mention : Information, Systèmes et Technologie (EEA)<br />

UE commune aux parcours SET et SECI(R&P)<br />

Objectifs : Plus de 75% des circuits intégrés de type systèmes sur puces (SoC) contiendront prochainement des<br />

fonctions analogiques. Ces fonctions réalisées sur technologie CMOS seront surtout utilisées pour les interfaces avec le<br />

monde extérieur (capteurs et actionneurs). L'objectif de ce cours est de fournir les connaissances indispensables à<br />

l'utilisation et la conception de ces fonctions analogiques : bruit, méthodes, fonctions intégrées, couplages avec les<br />

parties numériques, outils. L'objectif de la partie pratique sera la réalisation d'une partie d'un ASIC envoyé en fonderie<br />

dans le cours de l'année.<br />

Contenu des enseignements (avec nb d’heures) Cours TD TP<br />

♦ Introduction :<br />

4 h<br />

− évolution de la technologie MOS et des modèles de composants<br />

− intégration de capteurs, actionneurs, MEMS<br />

♦ Circuits intégrés analogiques :<br />

18 h<br />

− Techniques de dessin des masques analogique<br />

− Bruit dans les composants<br />

− Macro-fonctions analogiques (amplificateurs, comparateurs, filtres, références de<br />

tension, VCO …)<br />

− Circuits à capacités commutées<br />

− Architecture des circuits programmables analogiques (FPAA)<br />

♦ TP :<br />

− conception et simulation et dessin des masques d'un circuit intégré mixte (logiciel<br />

CADENCE) : par exemple PLL, conditionnement de capteur intégré<br />

− tests comparatifs entre l'ASIC et la même fonction réalisée sur FPAA<br />

28 h<br />

Enseignants : H. Mathias (MC), M. Zhang (MC), Nicolas Zérounian (MC)<br />

Prérequis : UE PhysI-436 ou équivalent<br />

Nombre maximum d’inscrits :<br />

Contrôle des connaissances : écrit (1/2) + TP (1/2)<br />

nb d’heures : 50 h<br />

ECTS : 5<br />

12/06/12<br />

4

Nom de l’UE : Formation générale<br />

Responsables : Nicolas Zérounian<br />

Mention : Information, Systèmes et Technologie (EEA)<br />

PhysI-C20<br />

type d’UE : CM + labo<br />

UE commune aux parcours SET et SECI(P)<br />

Objectifs :<br />

♦ Préparer les étudiants à l'écriture d'un CV et d'une lettre de motivation. Préparer les étudiants à un entretien<br />

d'embauche, Donner aux étudiants les bases de la communication dans les entreprises, la place de l'ingénieur<br />

dans l'entreprise, le contrat de travail.<br />

♦ Préparer au TOEIC. Améliorer le niveau d’anglais dans les 4 compétences de base : expression et compréhension<br />

écrites, expression et compréhension orales.<br />

Contenu des enseignements (avec nb d’heures) Cours TD TP<br />

♦ Anglais<br />

30 h<br />

− Test d'évaluation du niveau<br />

− Preparation au TOEIC (Test Of English for International Communication)<br />

− Rappels de grammaire (en fonction du niveau)<br />

− Lecture, compréhension et analyse de texte (articles, rapports...)<br />

− Compréhension orale<br />

− Participation orale<br />

− Débats et discussions<br />

− Exposé en anglais avec powerpoint...<br />

− Écriture d’un CV<br />

− Écriture d’une lettre de motivation<br />

− Préparation à un entretien d’embauche<br />

♦ Communication, droit du travail et droit des brevets<br />

20 h<br />

− Techniques d'écriture (écrire pour communiquer) et notes de synthèse<br />

− L'entreprise, la place de l'ingénieur<br />

− Contrat de travail, les conventions dans les entreprises<br />

− Rédaction de CV<br />

− Simulation d’entretien d’embauche<br />

− Lettre de motivation<br />

− Techniques d'exposé oral et conduite de réunion<br />

− Techniques d'entretiens et de négociation<br />

− Jeu de rôle<br />

♦ Recherche de stage : Les étudiants doivent fournir avant leur départ en stage un<br />

dossier résumant leurs démarches de recherche (annonces et CV/lettres de<br />

motivation correspondants)<br />

Enseignants : enseignants du laboratoire de langues (M. Oriol), J. Lemaitre, M. Cros (avocat)<br />

Prérequis : −−−<br />

Mise en commun : commun aux M2P du <strong>Master</strong> <strong>IST</strong><br />

Nombre maximum d’inscrits :<br />

Contrôle des connaissances : Anglais : exercices pendant les cours + TOEIC (1/2)<br />

Communication : participation, CV, lettre de motivation, simul. entretien (1/2)<br />

Nombre d’heures : 50 h<br />

ECTS : 5<br />

12/06/12<br />

5

Nom de l’UE : Gestion de projet et projet<br />

Responsables : Nicolas Zerounian<br />

Mention : Information, Systèmes et Technologie (EEA)<br />

PhysI-C21<br />

type d’UE : CM + TP +Projet<br />

UE commune aux parcours SET(P) et SECI(P)<br />

Objectifs :<br />

♦ Gestion de projet : Fournir aux étudiants les bases de la gestion d’un projet industriel.<br />

♦ Projet : Mettre les étudiants dans une situation de gestion et de réalisation de projets industriels<br />

Contenu des enseignements (avec nb d’heures) Cours TD TP<br />

♦ EC 1 - Gestion de projet :<br />

9 h 6 h<br />

− notion de projet :<br />

o définition; enjeu, objectif, but, acteur, le cycle de vie du projet<br />

o méthodologies, exemples de projets, exemples de non-projets, exemple fil<br />

rouge : un régulateur de climatisation automobile<br />

− spécificités des projets logiciels : objectifs et spécifications, notions de production<br />

et livraison, cycle de maintenance, gestion de configuration<br />

− qualité<br />

o notion de qualité, gestion documentaire (PAQL, DoD178), les 7 outils (causeeffets,<br />

Ishikawa, Pareto...), normes & standards<br />

(PAQL/SPICE/POSIX/C/CGNS, relations humaines)<br />

o chef de projet, équipe, communication, encadrement/délégation, conduite de<br />

réunion<br />

− estimation/pilotage : définition des objectifs, structure/ressources,<br />

prévision/livrables/jalons, gestion des priorités/risques<br />

− le suivi de projet : contrôler/suivre/prévoir/alerter, capitaliser l'acquis<br />

− Outil MS project : tâches, estimation coûts, ordonnancement, ressources/calendriers<br />

planification GANTT, PERL, suivi, édition de rapports, redéfinir les tâches, redéfinir<br />

les ressources, sous-traitance<br />

♦ EC 2 – Projet : mise en pratique des connaissances techniques acquises tout au long du 4 semaines<br />

cursus de l'étudiant, le projet pourra notamment être l'occasion de finaliser le système<br />

électronique conçu tout le long de l'année dans le cadre des TP des différentes UE :<br />

typiquement, il pourrait s'agir de la caractérisation de l'ASIC développé et du<br />

développement de l'électronique de mise en œuvre sur FPAA et FPGA.<br />

Enseignants : enseignants de la formation, M. Poinot (Ing.)<br />

Prérequis : −−−<br />

Mise en commun : EC 1 commun aux M2 R&T (UE Erreur ! Source du renvoi introuvable.60), 3I (Erreur ! Source<br />

du renvoi introuvable.95) du master <strong>IST</strong><br />

UE commune aux M2P SECI et SEE du master <strong>IST</strong><br />

Nombre maximum d’inscrits : −−−<br />

Contrôle des connaissances : Gestion de projet : contrôle continu en TP (1/5)<br />

Projet : travail (2/5) + rapport (1/4) + soutenance (1/5)<br />

nb d’heures : 15 h + projet de 4 semaines<br />

ECTS : 5<br />

12/06/12<br />

6

Nom de l’UE : Stage<br />

Responsables : Nicolas Zérounian<br />

Mention : Information, Systèmes et Technologie (EEA)<br />

PhysI-C22<br />

type d’UE : Stage<br />

UE commune aux parcours SET et SECI(P)<br />

Objectifs : Stage de 4 à 6 mois dans le domaine du parcours suivi<br />

Contenu des enseignements (avec nb d’heures) Cours TD TP<br />

♦ Stage :<br />

− mise en pratique des connaissances techniques acquises tout au long du cursus de<br />

l'étudiant<br />

− rédaction d'un rapport.<br />

− soutenance orale<br />

Enseignants : Un tuteur universitaire suit le stagiaire à distance durant toute la durée du stage<br />

Prérequis : −−−<br />

Nombre maximum d’inscrits : −−−<br />

Contrôle des connaissances :<br />

Evaluation : travail (6/12), rapport (3/12) et soutenance (3/12)<br />

nb d’heures :<br />

ECTS : 12<br />

12/06/12<br />

7

Nom de l’UE : Remise à niveau<br />

Responsables : Hervé Mathias<br />

PhysI-J00<br />

type d’UE : CM + TP<br />

Mention : Information, Systèmes et Technologie (EEA)<br />

Objectifs : Remise à niveau en informatique, en langages de modélisation et en électronique analogique intégrée<br />

Contenu des enseignements (avec nb d’heures) Cours TD TP<br />

Informatique 15h 15h<br />

♦ Bases du C<br />

♦ Bases du C++<br />

Langages de modélisation (VHDL)<br />

6h<br />

♦ VHDL pour la modélisation de systèmes numériques<br />

Electronique analogique intégrée<br />

4h<br />

♦ Transistor MOS: modèle statique et petit signaux<br />

♦ Cellules de bases (source commune, drain commun, grille commune, miroir de courant)<br />

Enseignants : H. Mathias (MC), M. Zhang (MC), S. Bouchafa (MC)<br />

Prérequis : −−−<br />

Mise en commun : les parties langages de modélisation et électronique analogique intégrée sont communes<br />

entre les parcours SET et SECI (R&P)<br />

Nombre maximum d’inscrits : −−−<br />

Contrôle des connaissances :<br />

nb d’heures : 40 h<br />

ECTS : 0<br />

12/06/12<br />

8

Nom de l’UE : Processeurs et périphériques Embarqués<br />

Responsables : Hervé Mathias<br />

Mention : Information, Systèmes et Technologie (EEA)<br />

PhysI-J03<br />

type d’UE : CM +TD+ TP<br />

UE commune aux parcours SET et SECI(R&P)<br />

Objectifs : Présenter les différentes architectures de processeurs embarqués et les spécificités liées à leur mise en<br />

œuvre : optimisation de l'architecture en fonction des besoins, personalisation du jeu d'instructions par adjonction de<br />

circuits numériques développés en VHDL, implantation d'IP et périphériques embarqués associés.<br />

Contenu des enseignements (avec nb d’heures) Cours TD TP<br />

♦ Architecture et mise en œuvre de processeur embarqué :<br />

9h<br />

En se basant sur le processeur utilisé en TP:<br />

− Organisation du processeur<br />

− Possibilités de personnalisation: modifications architecturales, jeu d'instruction<br />

− la gestion mémoire (segmentation et pagination)<br />

− les mémoires cache<br />

− la commutation de tâches, commutation de tâches par interruptions<br />

− Mise en œuvre et programmation en C<br />

♦ IP et périphériques embarqué :<br />

En se basant sur le système utilisé en TP:<br />

− DMA<br />

− Ports d'entrée/sortie<br />

− Contrôleurs de mémoire : SDRAM, Flash<br />

− Temporisateur<br />

− Mise en oeuvre<br />

3h<br />

♦ Travaux pratiques<br />

− Mise en œuvre d'un processeur embarqué compatible avec les outils de<br />

développement utilisés en électronique numérique (par exemple NIOS II avec les<br />

outils Altera (Quartus)) – Mini projets sur plusieurs séances pour la mise en œuvre de<br />

systèmes de contrôle de périphériques externes ou de systèmes de traitement d'image<br />

28 h<br />

Enseignants : S. Bouaziz (MC), A. Elouardi (MC), H. Mathias (MC)<br />

Prérequis :<br />

Nombre maximum d’inscrits :<br />

Contrôle des connaissances : écrit (1/2) + TP (1/2)<br />

nb d’heures : 40 h<br />

ECTS : 4<br />

12/06/12<br />

9

Nom de l’UE : Bus et interfaces embarqués<br />

Responsables : Abdelhafid Elouardi<br />

PhysI-J04<br />

type d’UE : CM + TP<br />

Mention : Information, Systèmes et Technologie (EEA)<br />

Objectifs : Former les étudiants aux différents protocoles d'échange de données et de commande que l'on peut<br />

rencontrer dans les systèmes embarqués.<br />

Contenu des enseignements (avec nb d’heures) Cours TD TP<br />

10 h 20 h<br />

♦ Bus et interfaces<br />

4h<br />

8h<br />

− UART<br />

− JTAG<br />

− bus actuels : PCI, AGP x1-x8 (architecture, performances, commandes, protocoles)<br />

− interfaces périphériques : USB 1 et 2, Fire-Wire, PCMCIA<br />

− interfaces périphériques : série, parallèle, GPIB/HPIB<br />

♦ Bus CAN : système on chip et Bus CAN (commun M2P SII)<br />

− les microcontrôleurs enfouis à base de SOPC dédiés à l'Internet : exemple BECK<br />

− présentation générale du bus CAN<br />

− historique, avantages, utilisation industriel, modèle OSI/ISO, caractéristique<br />

Physique<br />

− exemples de circuits CAN<br />

− mise en œuvre d'un module "cannisé" à base de périphérique CAN (exemple :<br />

SJA1000)<br />

− mise en œuvre du bus CAN au travers de microcontrôleurs "cannisés" : le 80C592 de<br />

Philips<br />

− étude détaillée d'un système enfoui multiplexé par un bus CAN<br />

− architecture détaillée du 80C592, ses divers périphériques on chip (timer,<br />

interruptions, I/O)<br />

− le contrôleur CAN on chip du 80C592, mise en œuvre logicielle, mécanisme<br />

d'optimisation d'échanges de données (DMA)<br />

− TP : prise en main de l'environnement logiciel pour la conception de programmes en<br />

C (famille de microcontrôleurs 80C5XX) ; mécanismes d'échanges de données sur le<br />

bus CAN, Trames REMOTE et DATA ; mécanismes pour la sécurisation des échanges<br />

de données sur le bus CAN<br />

6h<br />

12h<br />

Enseignants : S. Bouaziz (MC), L. Lacassagne (MC), A. Elouardi (MC), H. Mathias (MC)<br />

Prérequis : −−−<br />

Mise en commun : partie Bus CAN commun parcours M2P SII du master <strong>IST</strong>, voir descriptif et nbre heures et ECTS<br />

Nombre maximum d’inscrits : −−−<br />

Contrôle des connaissances : examen écrit (1/2) et TP (1/2)<br />

nb d’heures : 30 h<br />

ECTS : 3<br />

12/06/12<br />

10

Nom de l’UE : Traitement du signal et applications sur DSP<br />

Responsable : Thomas Rodet<br />

Mention : Information, Systèmes et Technologie (EEA)<br />

PhysI-J05<br />

type d’UE : CM + TD-TP<br />

UE commune aux parcours SET et SECI(R&P)<br />

Objectifs : Cette UE, au cœur de l’informatique industrielle, fournit des outils théoriques élaborés de<br />

modélisation, d’estimation et de traitement du signal tout en insistant sur l’implantation de ces outils sur des<br />

dispositifs de traitement numérique. Une part importante est accordée à l’expérimentation, dans un premier<br />

temps dans un environnement de simulation (Matlab) puis sur une maquette réelle centrée sur un DSP (de la<br />

famille TMS).<br />

Contenu des enseignements (avec nb d’heures) Cours TD-TP<br />

20 h 30 h<br />

♦ DSP ( commun M2 P SII) :<br />

8 h<br />

− approche architecture : caractéristique des processeurs modernes (cache, DMA,<br />

unités de calcul rapide)<br />

− architecture des ordinateurs<br />

− registres, unités de calculs<br />

− particularités des architectures parallèles VLIW (8 unités de calcul), impact sur le<br />

code<br />

− outils de développement (compilateur, assembleur, simulateur, débogueur)<br />

− problème des entrées-sorties (cache DMA)<br />

− techniques d’optimisation logicielles<br />

− problème des entrées-sorties (cache DMA)<br />

− étude de différents cas d’école<br />

♦ Traitement du signal :<br />

12 h<br />

− modélisation, estimation paramétrique, identification de processus<br />

− moindres carrés, moindres carrés récursifs, estimation au sens du maximum de<br />

vraisemblance, filtrage de Kalman<br />

− estimation spectrale<br />

− approche non paramétrique, approche paramétrique<br />

− éléments de théorie de la décision<br />

− tests d’hypothèses, critères de Bayes, de Neyman-Pearson, MinMax<br />

♦ Approche TS en Matlab, puis implantation sur DSP :<br />

26 h<br />

− compression du son avec algorithme de type LPC (modélisation, estimation<br />

paramétrique)<br />

− estimation spectrale : reconnaissance de notes de musiques (analyse spectrale non<br />

paramétrique / analyse spectrale paramétrique)<br />

− théorie de la décision : reconnaissance de touche DTMF avec/sans bruit (analyse<br />

spectrale, filtrage adapté, estimation au sens du maximum de vraisemblance)<br />

♦ Tracking (si caméra) de cible, asservissement du servo-moteur (filtrage de Kalman) ;<br />

impact du bruit du capteur, si tracking impossible, TP d’architecture<br />

4 h<br />

Enseignants : T. Rodet (MC), L. Lacassagne (MC)<br />

Prérequis : UE Erreur ! Source du renvoi introuvable.51ou Erreur ! Source du renvoi introuvable.52 du M1 <strong>IST</strong> ou<br />

équivalent<br />

Mise en commun : parcours M2P SET du master <strong>IST</strong><br />

partie DSP parcours 5.2<br />

Nombre maximum d’inscrits : −−−<br />

Contrôle des connaissances : examen écrit (2/3) + moyenne des TP (1/3)<br />

nb d’heures : 50 h<br />

ECTS : 5<br />

12/06/12<br />

<strong>11</strong>

Nom de l’UE : Traitement d'image pour applications embarquées<br />

Responsable : Samia Bouchafa<br />

PhysI-J06<br />

type d’UE : CM +TP<br />

Mention : Information, Systèmes et Technologie (EEA)<br />

Objectifs : Former les étudiants aux techniques, méthodes et algorithmes de reconstruction et de restauration de<br />

signaux, d’images et de séquences vidéo. La majeure partie du cours concerne les techniques les plus courantes et la<br />

dernière partie concerne des méthodes plus modernes.<br />

Contenu des enseignements (avec nb d’heures) Cours TD TP<br />

38 h 12 h<br />

♦ Applications possibles, problèmes génériques :<br />

− imagerie médicale (IRM, scanner), astronomique, satellitaire, en évaluation nondestructive.<br />

− déconvolution, sur résolution, synthèse de Fourier, tomographie…<br />

♦ Méthodes et algorithmes :<br />

−<br />

moindres carrés et filtrage inverse<br />

− pénalisation quadratique, solution de Hunt et filtrage de Wiener<br />

interprétation bayésienne : moindres carrés, pénalisation / vraisemblance, loi a<br />

posteriori.<br />

♦ Travaux pratiques :<br />

− Reconstruction d'une image sur-résolue à partir d'une séquence vidéo prise à l'aide<br />

d'une webcam : Estimation du mouvement dans la scène, reconstruction sur-résolue<br />

(deux séances de 3 heures)<br />

Enseignants : S. Bouchafa (MC), T. Rodet (MC), G. Le Besnerais (Onéra)<br />

Prérequis : UE PhysI-451 ou PhysI-452 du M1 <strong>IST</strong> ou équivalent<br />

Nombre maximum d’inscrits :<br />

Contrôle des connaissances : examen écrit (3/4) + TP (1/4)<br />

nb d’heures : 50 h<br />

ECTS : 5<br />

12/06/12<br />

12

Nom de l’UE : Electronique des capteurs intégrés<br />

Responsable : Hervé Mathias<br />

PhysI-J07<br />

type d’UE : CM +TP<br />

Mention : Information, Systèmes et Technologie (EEA)<br />

Objectifs : Former les étudiants aux techniques de mise en œuvre des capteurs optiques et MEMS. Présentation de la<br />

physique de transduction associée et modélisation des différents éléments de la chaîne de mesure jusqu'à la conversion<br />

Analogique/Numérique afin de permettre une optimisation globale des performances de cette chaîne.<br />

Contenu des enseignements (avec nb d’heures) Cours TD TP<br />

28 h 12 h<br />

♦ Cours :<br />

− Caractéristiques d'une chaîne de mesure : sensibilité, dynamique, linéarité,<br />

résolution, méthodes de linéarisation et de calibration<br />

3h<br />

− Electronique des capteurs optiques: principe de détection, topologies de pixels,<br />

circuits de lecture, architecture des capteurs CCD et imageurs CMOS<br />

6 h<br />

− Electronique des MEMS : principes d'actionnement et de détection, piézorésistivité,<br />

conception de circuits de détection faible bruit, architectures d'oscillateurs intégrés<br />

à base de résonateurs MEMS<br />

6h<br />

− Conversion Analogique/Numérique : bruit de quantification, linéarité, convertisseur 6h<br />

−<br />

−<br />

flash, convertisseur à approximations successives, convertisseur sigma-delta<br />

Optimisation d'une chaîne de mesure intégrée à base de MEMS<br />

Langage de modélisation (VHDL-AMS)<br />

4h<br />

3h<br />

♦ TP :<br />

−<br />

−<br />

Modélisation en VHDL-AMS d'une chaîne de mesure intégrée<br />

Mise en œuvre sur FPAA de la chaîne de mesure modélisée<br />

8h<br />

4h<br />

Enseignants : H. Mathias (MC), A. Elouardi (MC), N. Llaser (PRAG), A. Dupret (MC), M. Poirier Quinot (MC)<br />

Prérequis :<br />

Nombre maximum d’inscrits :<br />

Contrôle des connaissances : écrit (2/3)+ TP (1/3)<br />

___________________________________________________________________________<br />

nb d’heures : 40 h<br />

ECTS : 4<br />

12/06/12<br />

13

Nom de l’UE : Conception de microsystèmes<br />

Responsable : Hervé Mathias<br />

Mention : Information, Systèmes et Technologie (EEA)<br />

PhysI-J08<br />

type d’UE : CM +TP<br />

UE partiellement commune Nanosciences et SECI(R&P)<br />

Objectifs : Former les étudiants aux techniques de conception et de simulation de dispositifs MEMS. Après des<br />

notions rapides sur la physique des MEMS (mécanique) et sur les méthodes de modélisation numériques<br />

correspondantes, les étudiants verront les démarches de conception du système complet incluant celle du<br />

microdispositif et de l'électronique associée, afin d'optimiser de manière globale les performances.<br />

Contenu des enseignements (avec nb d’heures) Cours TD TP<br />

26h<br />

24h<br />

Conception des MEMS et NEMS<br />

18h<br />

♦ Physique des microsystèmes: contraintes, déformations, equation de Poisson, de Navier<br />

Stokes …<br />

♦ Méthodes de résolution numérique d'équations aux dérivées partielles: éléments finis,<br />

éléments frontières, méthode de Fourier<br />

♦ Conception et simulation de MEMS/NEMS : prise en compte des couplages, des nonlinéarités<br />

♦ Travaux pratiques: établissement d'un modèle d'ordre réduit de microsystème<br />

12h<br />

(Matlab/Simulink); Modélisation de dispositifs MEMS par éléments finis (ANSYS);<br />

Conception globale d'un microsystème<br />

8h<br />

♦ Prise en compte des non-idéalités de l'électronique associée<br />

♦ Mise en équation des caractéristiques du microsystème : détermination des<br />

caractéristiques (sensibilité, biais, linéarité) de la chaîne globale; études de sensibilité<br />

pour dimensionner et choisir les différents éléments.<br />

♦ Détermination de la résolution : étude globale du bruit du système<br />

♦ Travaux pratiques : Conception d'un microsystème (par exemple accéléromètre) et de<br />

son électronique associée sous Coventor avec obtention du dessin des masques du<br />

dispositif MEMS<br />

12h<br />

Enseignants : H. Mathias (MC), J. Juillard (Supélec)<br />

Pré requis : −−−<br />

Mise en commun : la partie Conception des MEMS et NEMS est commune au parcours Nanodispo<br />

Nombre maximum d’inscrits : −−−<br />

Contrôle des connaissances : examen écrit (2/3) + TP (1/3)<br />

nb d’heures : 50 h<br />

ECTS : 5<br />

12/06/12<br />

14

Nom de l’UE : Fabrication et caractérisation de MEMS<br />

Responsables : Élisabeth Dufour-Gergam<br />

Mention : Information, Systèmes et Technologie (EEA)<br />

PhysI-J09<br />

type d’UE : CM + TP<br />

UE commune Nanosciences et SECI(R&P)<br />

Objectifs : Former les étudiants aux techniques de fabrication et de caractérisation de dispositifs MEMS. La plus<br />

grande partie de cette UE se fera sous forme de TP en salle blanche. Le cadre de cette UE est l'UE projet techno<br />

logique du parcours Nanosciences mais avec un contenu lié aux dispositifs conçus dans les autres modules.<br />

Contenu des enseignements (avec nb d’heures) Cours TD TP<br />

6 h 24 h<br />

♦ Fabrication de MEMS<br />

6 h 16 h<br />

− Photolithographie<br />

− Gravure : RIE, gravure humide<br />

− Bonding<br />

♦ Caractérisation<br />

− Caractérisation optique et électrique des dispositifs fabriqués<br />

8 h<br />

Enseignants : É. Dufour-Gergam (PU), H. Mathias (MC), F. Parrain (MC)<br />

Prérequis : −−−<br />

Nombre maximum d’inscrits : −−−<br />

Contrôle des connaissances : examen écrit (2/3) + TP (1/3)<br />

nb d’heures : 30 h<br />

ECTS : 3<br />

12/06/12<br />

15