LEZIONE #05 del 12-Mag-2008 (2 ore) - Dipartimento di Ingegneria ...

LEZIONE #05 del 12-Mag-2008 (2 ore) - Dipartimento di Ingegneria ...

LEZIONE #05 del 12-Mag-2008 (2 ore) - Dipartimento di Ingegneria ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Branch Pre<strong>di</strong>ction<br />

(parte seconda)<br />

Calcolatori Elettronici 2<br />

http://www.<strong>di</strong>i.unisi.it/~giorgi/<strong>di</strong>dattica/calel2<br />

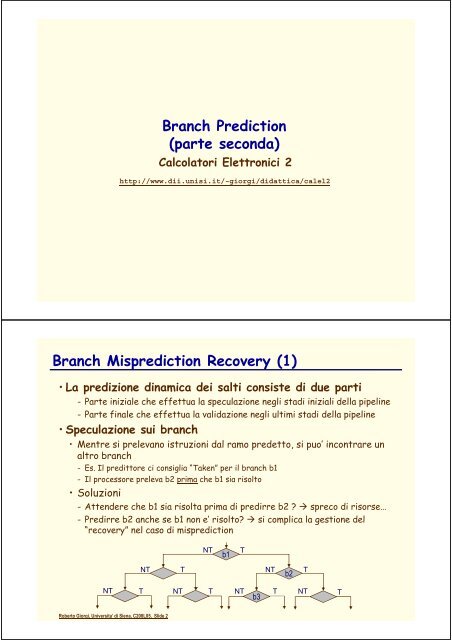

Branch Mispre<strong>di</strong>ction Recovery (1)<br />

• La pre<strong>di</strong>zione <strong>di</strong>namica dei salti consiste <strong>di</strong> due parti<br />

- Parte iniziale che effettua la speculazione negli sta<strong>di</strong> iniziali <strong>del</strong>la pipeline<br />

- Parte finale che effettua la validazione negli ultimi sta<strong>di</strong> <strong>del</strong>la pipeline<br />

• Speculazione sui branch<br />

• Mentre si prelevano istruzioni dal ramo predetto, si puo’ incontrare un<br />

altro branch<br />

- Es. Il pre<strong>di</strong>tt<strong>ore</strong> ci consiglia “Taken” per il branch b1<br />

- Il process<strong>ore</strong> preleva b2 prima che b1 sia risolto<br />

• Soluzioni<br />

- Attendere che b1 sia risolta prima <strong>di</strong> pre<strong>di</strong>rre b2 ? spreco <strong>di</strong> risorse…<br />

- Pre<strong>di</strong>rre b2 anche se b1 non e’ risolto? si complica la gestione <strong>del</strong><br />

“recovery” nel caso <strong>di</strong> mispre<strong>di</strong>ction<br />

NT<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 2<br />

T<br />

NT T NT<br />

NT<br />

T<br />

b1<br />

T<br />

NT<br />

b2<br />

T<br />

NT T NT<br />

b3<br />

T

Branch Mispre<strong>di</strong>ction Recovery (2)<br />

• Come si recupera (recovery) in questo caso<br />

• Vorremmo recuperare da una situazione <strong>di</strong> mispre<strong>di</strong>ction multipli<br />

• Situazione piu’ complessa: primo branch mispre<strong>di</strong>cted, secondo giusto<br />

• Esempio: stiamo speculando su 3 branch, b1, b2, b3<br />

- Le pre<strong>di</strong>zioni sono evidenziate con la linee tratteggiata<br />

- Le istruzioni <strong>di</strong> ogni ramo predetto sono residenti nel process<strong>ore</strong><br />

• Idea: a ogni istruzione su un dato ramo speculativo si assegna in TAG<br />

- Ogni ramo speculativo ha il proprio tag (Tag1, Tag2, Tag3)<br />

NT<br />

NT T NT<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 3<br />

T<br />

NT<br />

T<br />

T<br />

(Tag 2)<br />

(Tag 1)<br />

NT<br />

T<br />

NT T NT<br />

(Tag 3)<br />

Branch Mispre<strong>di</strong>ction Recovery (3)<br />

• Validazione dei branch<br />

• Quando il branch e’ risolto (<strong>di</strong>rezione e target sono noti)<br />

- CASO DI PREDIZIONE CORRETTA<br />

-Il tag viene rimosso e le istruzioni su quel ramo <strong>di</strong>vengono non-speculative<br />

- CASO DI PREDIZIONE ERRATA (MISPREDICTION)<br />

-Il ramo errato viene bloccato ed eliminato dalla pipeline<br />

-Devono essere rimossi anche tutti i rami speculativi successivi<br />

-Il ramo corretto viene eseguito dall’inizio inserendolo in pipeline<br />

• Esempio<br />

- Il secondo branch non e’ stato azzeccato<br />

- Tutte le istruzioni con Tag2 e Tag3 devono essere rimosse<br />

NT<br />

NT T NT<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 4<br />

T<br />

NT<br />

T<br />

T<br />

(Tag 2)<br />

NT<br />

T<br />

NT T NT<br />

(Tag 3)<br />

T<br />

T<br />

Ricominciare<br />

da qui!

Esempio - PowerPC 604 (1)<br />

• Microprocess<strong>ore</strong> Superscalare a 4 vie<br />

• Puo’ effettuare fetch, decode, execute <strong>di</strong> 4 istruzioni per ciclo<br />

• Branch Pre<strong>di</strong>ction<br />

• Usa due buffer separati:<br />

- Branch Target Address Cache (BTAC)<br />

- Branch History Table (BHT)<br />

• Vengono in<strong>di</strong>rizzati entrambi nello sta<strong>di</strong>o <strong>di</strong> fetch<br />

• BTAC (analogo al BTB)<br />

• Cache fully-associative a 64 elementi, risponde in 1 ciclo<br />

• Memorizza l’in<strong>di</strong>rizzo target <strong>del</strong> salto<br />

• BHT<br />

• Cache ad accesso <strong>di</strong>retto a 5<strong>12</strong> elementi, risponde in 2 cicli<br />

• Memorizza i bit <strong>di</strong> storia dei branch<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 5<br />

Esempio - PowerPC 604 (2)<br />

+4<br />

BHT pre<strong>di</strong>ction<br />

BTAC pre<strong>di</strong>ction<br />

Branch<br />

Pre<strong>di</strong>ction<br />

PC Branch History<br />

PC<br />

Table (BHT)<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 6<br />

PC<br />

Branch Target<br />

Address Cache<br />

(BTAC)<br />

PC<br />

BHT<br />

BTAC<br />

update update<br />

execute<br />

commit<br />

I-cache<br />

decode<br />

decode buffer<br />

<strong>di</strong>spatch buffer<br />

<strong>di</strong>spatch<br />

Reservation stations<br />

BRN SFX SFX CFX FPL LS<br />

branch<br />

Re-order buffer

Esempio - PowerPC 604 (3)<br />

• Hit nel BTAC<br />

• In<strong>di</strong>ca la presenza <strong>di</strong> un branch nella coda <strong>di</strong> fetch<br />

• L’in<strong>di</strong>rizzo target prelevato dal BTAC viene usato al ciclo successivo<br />

• Al secondo ciclo viene consultato il BHT<br />

• La pre<strong>di</strong>zione deve essere “taken”, se avevo fatto hit in BTAC al ciclo prima<br />

• Se le due pre<strong>di</strong>zioni NON sono in accordo?<br />

• Si butta la pre<strong>di</strong>zione <strong>del</strong> BTAC (significa che BHT ha predetto “not-taken”)<br />

• Il fetch continua dal ramo in cascata<br />

• La pre<strong>di</strong>zione <strong>del</strong> BHT prevale su quella <strong>del</strong> BTAC<br />

• Dopo aver risolto il branch si devono aggiornare sia BTAC che BHT<br />

• Perche’ servono entrambi ?<br />

• Il BTAC e’ piu’ veloce: se la pre<strong>di</strong>zione e’ giusta non attendo alcun ciclo<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 7<br />

Esempio - PowerPC 604 (4)<br />

• Il PowerPC 604 e’ superscalare<br />

• Nelle reservation-station ci possono essere fino a 4 istruzioni <strong>di</strong> salto<br />

• E’ necessario usare dei tag a 2 bit per gestire la speculazione<br />

• Segue lo schema introdotto poco sopra<br />

• In particolare le risorse occupate dalle istruzioni speculative<br />

debbono essere liberate in caso <strong>di</strong> mispre<strong>di</strong>ction<br />

(es. Reorder Buffer, una struttura tipica dei processori superscalari)<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 8

Pre<strong>di</strong>ttori a correlazione: gselect e gshare<br />

• Per generare l’in<strong>di</strong>ce <strong>del</strong>la PHT, Pan e (successivamente) McFarling<br />

suggeriscono <strong>di</strong> usare sia l’in<strong>di</strong>rizzo <strong>del</strong> branch (BIA) che la stringa<br />

<strong>di</strong> storia globale (BHSR)<br />

• La semplificazione e’ <strong>di</strong> NON usare una BHT con piu’ elementi<br />

• gselect [Pan92]<br />

• Alcuni bit <strong>del</strong> BIA sono accostati ai bit <strong>del</strong>la global history<br />

• gshare [McFarling93]<br />

• I bit <strong>del</strong> BIA sono “mescolati” (hashed) con quelli <strong>del</strong>la global history<br />

• La funzione <strong>di</strong> “mescolamento” <strong>di</strong> solito e’ l’operazione <strong>di</strong> XOR<br />

Branch<br />

address<br />

(BIA)<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 9<br />

Global<br />

history<br />

(BHSR)<br />

gselect 4/4 gshare 8/8<br />

0000 0000 0000 0001 0000 0001 00000001<br />

00000000 00000000 00000000 00000000<br />

11111111 00000000 11110000 11111111<br />

11111111 10000000 11110000 01111111<br />

gselect [Pan92]<br />

• m bit dall’in<strong>di</strong>rizzo (BIA) sono accostati ai k bit <strong>del</strong> BHSR<br />

• Schema molto semplice: 1 BHSR e 1 piccolo PHT<br />

BHSR<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 10<br />

k<br />

BIA<br />

m<br />

k+m<br />

PHT<br />

…<br />

2 k+m x j<br />

entries<br />

pre<strong>di</strong>ction

gshare [McFarling93]<br />

• m bit <strong>del</strong>l’in<strong>di</strong>rizzo BIA sono messi in XOR con il BHSR<br />

• Schema molto semplice: 1 BHSR e 1 piccolo PHT<br />

• Usato nell’Alpha 2<strong>12</strong>64<br />

BHSR<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 11<br />

BIA<br />

Di solito sono i bit meno significativi <strong>del</strong> BIA<br />

Inoltre, <strong>di</strong> solito k == m<br />

k<br />

m<br />

max{k, m}<br />

PHT<br />

…<br />

2 max{k, m} x j<br />

entries<br />

Prestazioni <strong>di</strong> gshare, gselect, GAg<br />

Pre<strong>di</strong>ctor Accuracy (%)<br />

98<br />

96<br />

94<br />

92<br />

90<br />

88<br />

86<br />

84<br />

Grafico da [McFarling93]<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide <strong>12</strong><br />

pre<strong>di</strong>ction<br />

32 64 256 1K 4K 16K 64K<br />

Pre<strong>di</strong>ctor Size(bytes)<br />

“global” si riferisce al pre<strong>di</strong>tt<strong>ore</strong> GAg <strong>di</strong> Yeh e Patt<br />

I benchmark usati sono gli stessi 9 <strong>di</strong> SPEC-89 usati nei lavori [Yeh92] e [Yeh93]<br />

gshare<br />

gselect<br />

global

Pre<strong>di</strong>ttori “competitivi” (“Tournament”)<br />

• Certi pre<strong>di</strong>ttori funzionano bene con determinati branch<br />

• La prima proposta <strong>di</strong> usare due pre<strong>di</strong>ttori competitivi e’ presentata<br />

da McFarling [McFarling93] (bimodal+gshare)<br />

• Selezionare <strong>di</strong>namicamente una pre<strong>di</strong>zione fra piu’ pre<strong>di</strong>ttori<br />

• Usare la storia per selezionare un pre<strong>di</strong>tt<strong>ore</strong><br />

BHT<br />

BIA<br />

• Esempio: Alpha 2<strong>12</strong>64<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 13<br />

Path History<br />

Pre<strong>di</strong>ctor 1<br />

Pre<strong>di</strong>ctor 2<br />

M<br />

U pre<strong>di</strong>ction<br />

U<br />

X<br />

Pre<strong>di</strong>ctor<br />

selection<br />

logic<br />

• Dimensione totale <strong>del</strong> pre<strong>di</strong>tt<strong>ore</strong> pari a 29k bits<br />

• A BP = 97.4%(SPEC89 average)<br />

99.9% (SPECfp95 average), 99% (SPECint95 average)<br />

Pre<strong>di</strong>tt<strong>ore</strong> <strong>del</strong>l’in<strong>di</strong>rizzo <strong>di</strong> ritorno<br />

• Alcuni salti variano l’in<strong>di</strong>rizzo target nello stesso programma<br />

• Tali salti sono tipicamente “in<strong>di</strong>rect jumps”<br />

• In particolare, fra questi ci sono i salti <strong>di</strong> ritorno da procedura<br />

• Nel caso <strong>di</strong> SPEC-89 i salti da ritorno da procedura sono l’85%<br />

• Pre<strong>di</strong>zione <strong>del</strong>le istruzioni <strong>di</strong> ritorno da procedura<br />

• L’esito e’ facile da pre<strong>di</strong>rre: always taken!<br />

• Il target non e’ facile da pre<strong>di</strong>rre: la stessa procedura puo’ essere<br />

invocata da <strong>di</strong>versi punti <strong>di</strong> un programma<br />

• Il BTB per pre<strong>di</strong>rre il target puo’ condurre a mispre<strong>di</strong>ction<br />

• E’ stato proposto un piccolo stack per mantenere gli in<strong>di</strong>rizzi<br />

<strong>di</strong> ritorno [Kaeli91]<br />

• Al momento <strong>del</strong>la chiamata si fa push <strong>del</strong>l’in<strong>di</strong>rizzo <strong>di</strong> ritorno in tale stack<br />

• Al momento <strong>del</strong> ritorno basta fare una pop da tale stack<br />

• Funziona come una cache dei piu’ recenti in<strong>di</strong>rizzi <strong>di</strong> ritorno<br />

• Se tale stack e’ sufficientemente grande pre<strong>di</strong>ce tutti i ritorni<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 14

Pre<strong>di</strong>zioni multiple [Yeh93-ics]<br />

• Idea: pre<strong>di</strong>rre i salti successivi anche se i precedenti<br />

non sono risolti<br />

• Effettuare 1 pre<strong>di</strong>zione per ciclo<br />

• Mentre si cerca <strong>di</strong> effettuare le pre<strong>di</strong>zioni successive,<br />

puo’ essere utile aggiornare speculativamente PHT e BHT<br />

• La tecnica funziona bene se l’accuratezza <strong>del</strong>la prima<br />

pre<strong>di</strong>zione e’ alta<br />

• 1 st pre<strong>di</strong>zione – 96% <strong>di</strong> accuratezza =><br />

- 2 nd pre<strong>di</strong>zione – 92.16% accuratezza =><br />

-4 th pre<strong>di</strong>zione – 84.93% accuratezza<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 15<br />

Pre<strong>di</strong>zioni multiple (2)<br />

• Idea2: effettuare PIU’ pre<strong>di</strong>zioni per ciclo<br />

• Questo permette <strong>di</strong> prelevare piu’ basic block (possibilmente<br />

giusti) simultaneamente<br />

• Si puo’ usare come schema base il GAg<br />

• Ha il vantaggio <strong>di</strong> poter effettuare pre<strong>di</strong>zioni senza il BIA<br />

Global BHSR<br />

(k bits)<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 16<br />

k<br />

k-1<br />

PHT<br />

M<br />

U<br />

X<br />

Secondary pre<strong>di</strong>ction<br />

Primary pre<strong>di</strong>ction<br />

Nota: con k bit si seleziona un elemento <strong>del</strong>la PHT (pre<strong>di</strong>zione primaria). Usando k-1 bit meno significativi<br />

seleziono I prossimi due possibili elementi <strong>del</strong>la PHT: da questi posso selezionarne uno uilizzando la<br />

pre<strong>di</strong>zione primaria e ottenendo cosi’ la pre<strong>di</strong>zione secondaria

Eager Execution [Uht95]<br />

• In un gruppo <strong>di</strong> 4 istruzioni e’ possibile che tutte e 4<br />

siano branch<br />

• Si deve far ricorso ad un BTB a 4 porte<br />

(similmente al pre<strong>di</strong>tt<strong>ore</strong> multiplo <strong>di</strong> Yeh)<br />

• Eager Execution<br />

• Si eseguono sia il ramo taken che quello not-taken senza pre<strong>di</strong>zioni<br />

- Il fetch avviene da entrambi i rami taken e not-taken<br />

- Nel lavoro <strong>di</strong> Uht il fetch viene limitato a 6 ramificazioni<br />

- Vengono via via buttati i rami sbagliatai nel momento in cui i branch sono risolti<br />

- Naturalmente viene buttato parecchio lavoro… ma e’ veloce!<br />

• Disjoint Eager Execution<br />

- In questo caso si considera la brench pre<strong>di</strong>ction mentre si fa il fetch<br />

- Si prelevano solo istruzioni dai rami predetti, fino a 6 ramificazioni<br />

- Se il ramo e’ sbagliato, semplicemente si fa ripartire la pipeline<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 17<br />

Trace Cache<br />

• Cattura sequenze <strong>di</strong> basic-blocks (tracce <strong>di</strong>naniche) in una cache che<br />

sostituisce la cache istruzioni<br />

• Tale cache e’ in<strong>di</strong>cizzata dal target <strong>di</strong> un salto<br />

• Gli elementi <strong>di</strong> tale cache sono asssemblati <strong>di</strong>namicamente mentre il programma esegue le<br />

sue istruzioni<br />

• Se c’e’ hit nella trace cache<br />

• Le istruzioni vengono prelevate dalla trace cache<br />

• La sequenza prelevata tipicamente contiene piu’ basic-block<br />

(ovvero una sequenza <strong>di</strong> piu’ taken branch)<br />

• Si elimina la necessita’ <strong>di</strong> fare il fetch <strong>di</strong> piu’ target<br />

• Inoltre la cache non deve essere con piu’ porte<br />

Quando il co<strong>di</strong>ce viene eseguito<br />

la prima volta: si registra la<br />

sequenza nella trace cache<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 18<br />

B1<br />

B2 B3<br />

B4<br />

B1 B3 B4<br />

va nella trace cache<br />

B1<br />

B3<br />

B4<br />

La volta successiva si<br />

legge la sequenza dalla<br />

trace cache: non c’e’<br />

bisogno <strong>di</strong> pre<strong>di</strong>rla !

ALPHA 2<strong>12</strong>64<br />

Branch Pre<strong>di</strong>ction case study<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L01, Slide 19<br />

Process<strong>ore</strong> Alpha 2<strong>12</strong>64<br />

• 500-600 MHz, 15x10 6 transistors, 2.2V, 0.35µ CMOS<br />

• Process<strong>ore</strong> a 64-bit<br />

• Process<strong>ore</strong> Superscalare a 4 vie<br />

• Puo’ prelevare ed eseguire fino a 4 istruzioni per ciclo<br />

• L’esecuzione avviene “fuori or<strong>di</strong>ne” (out-of-order)<br />

• Secondo Hennessy e Patterson ha il pre<strong>di</strong>tt<strong>ore</strong> piu’<br />

sofisticato implmentato fino al 2003<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 20

Pre<strong>di</strong>tt<strong>ore</strong> <strong>del</strong>l’Alpha 2<strong>12</strong>64 [Alpha99]<br />

• Tournament Pre<strong>di</strong>ctor<br />

• Sceglie <strong>di</strong>namicamente fra due pre<strong>di</strong>ttori<br />

- Il “pre<strong>di</strong>tt<strong>ore</strong> locale” (sinistra) – equivalente ad uno schena PAg<br />

- Il “pre<strong>di</strong>tt<strong>ore</strong> globale” (destra) – equivalente ad uno schema Gag<br />

- La selezione <strong>del</strong> pre<strong>di</strong>tt<strong>ore</strong> avviene attraverso una storia degli esiti<br />

competitivi data in pasto al solito contat<strong>ore</strong> a saturazione a 2 bit.<br />

Local pre<strong>di</strong>ctor<br />

Local<br />

history<br />

table<br />

(1024 x 10)<br />

Program<br />

counter<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 21<br />

Local<br />

pre<strong>di</strong>ction<br />

(1024 x 3)<br />

branch<br />

pre<strong>di</strong>ction<br />

MUX<br />

Global pre<strong>di</strong>ction<br />

(4096 x 2)<br />

Alpha 2<strong>12</strong>64 - Pre<strong>di</strong>tt<strong>ore</strong> Locale<br />

• Local History Table (LHT)<br />

Choice pre<strong>di</strong>ction<br />

(4096 x 2)<br />

Path history<br />

• Equivalente alla BHT <strong>del</strong>lo schema PAg (k=10, 1024 entry BHT (m=10))<br />

• Mantiene gli ultimi 10 esiti per un massimo <strong>di</strong> 1024 branch<br />

• E’ in<strong>di</strong>cizzato dall’in<strong>di</strong>rizzo <strong>del</strong>l’istruzione <strong>di</strong> salto (BIA)<br />

• Local Pre<strong>di</strong>ction Table (LPT)<br />

• Equivalente a una PHT <strong>del</strong>lo schema PAg (j=3, 1024 entries(k=10))<br />

• E’ in<strong>di</strong>cizzata dall’elemento <strong>di</strong> storia <strong>del</strong>la LHT<br />

• La FSM e’ un contat<strong>ore</strong> a saturazione a 3 bit<br />

• La pre<strong>di</strong>zione coincide col bit piu’ significativo <strong>del</strong>lo stato (1=T)<br />

• La LHT e la LPT sono aggiornate dopo che il branch viene<br />

risolto<br />

• Funziona bene per sequenze alternativamente T e N<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 22

Alpha 2<strong>12</strong>64 - Pre<strong>di</strong>tt<strong>ore</strong> Globale<br />

• Tabella da 4096 elementi<br />

• E’ equivalente alla PHT <strong>del</strong>lo schema GAg (j=2, 4096-entry PHT (k=<strong>12</strong>))<br />

• E’ in<strong>di</strong>cizzata con un registro <strong>di</strong> storia globale a <strong>12</strong> bit<br />

• Pre<strong>di</strong>tt<strong>ore</strong><br />

• La FSM e’ un contat<strong>ore</strong> a saturazione a 2-bit<br />

• La pre<strong>di</strong>zione coincide col bit piu’ significativo <strong>del</strong>lo stato (1=T)<br />

• Funziona bene per branch che sono influenzati da branch<br />

precedenti<br />

• Esempio:<br />

if (x == 10)<br />

{<br />

…<br />

}<br />

if (x % 2 == 0)<br />

…<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 23<br />

Se questo e’ taken…<br />

…e x non e’ cambiata qui…<br />

…anche questo branch sara’ taken<br />

Un pre<strong>di</strong>tt<strong>ore</strong> Globale<br />

tipicamente apprende<br />

e pre<strong>di</strong>ce correttamente<br />

situazioni <strong>di</strong> questo tipo<br />

Alpha 2<strong>12</strong>64 - Dimensione totale <strong>del</strong> pre<strong>di</strong>tt<strong>ore</strong><br />

• Pre<strong>di</strong>tt<strong>ore</strong> Globale<br />

• 4096 x 2 = 8K bits<br />

• Pre<strong>di</strong>tt<strong>ore</strong> Locale<br />

• Local History Table – 1024 x 10 = 10K bits<br />

• Local Pre<strong>di</strong>ction Table – 1024 x 3 = 3K bits<br />

• Logica <strong>di</strong> selezione <strong>del</strong> pre<strong>di</strong>tt<strong>ore</strong><br />

• 4096 x 2 = 8K bits<br />

• Totale<br />

• 29K bits<br />

• ~180,000 transistors<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 24

Uso <strong>del</strong> pre<strong>di</strong>tt<strong>ore</strong> Globale rispetto a Locale<br />

li<br />

eqntott<br />

espresso<br />

gcc<br />

fpppp<br />

spice<br />

doduc<br />

tomcatv<br />

matrix300<br />

nasa7<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 25<br />

Fraction of pre<strong>di</strong>ctions by local pre<strong>di</strong>ctor<br />

37<br />

0 10 20 30 40 50 60 70 80 90 100<br />

Percentuale <strong>di</strong> branch predetti dal local pre<strong>di</strong>ctor<br />

Numero <strong>di</strong> pre<strong>di</strong>zioni <strong>del</strong> pre<strong>di</strong>tt<strong>ore</strong> locale, normalizzato rispetto<br />

al numero totale <strong>di</strong> pre<strong>di</strong>zioni (locali+globali)<br />

Grafico da [Hennessy02]<br />

Prestazioni dei pre<strong>di</strong>ttori – A BP<br />

tomcatv<br />

doduc<br />

fpppp<br />

li<br />

espresso<br />

gcc<br />

Grafico da [Hennessy02]<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 26<br />

55<br />

70%<br />

63<br />

77%<br />

69<br />

84%<br />

72<br />

86%<br />

82%<br />

88%<br />

86%<br />

82%<br />

88%<br />

76<br />

95%<br />

94%<br />

99%<br />

99%<br />

100%<br />

97%<br />

98%<br />

98%<br />

96%<br />

0% 20% 40% 60% 80% 100%<br />

Branch pre<strong>di</strong>ction accuracy<br />

90<br />

94<br />

98<br />

100<br />

Profile-based<br />

2-bit counter<br />

Tournament

Prestazioni dei pre<strong>di</strong>ttori: mispred.rate vs. <strong>di</strong>m.<br />

Con<strong>di</strong>tional branch mispre<strong>di</strong>ction rate<br />

10%<br />

9%<br />

8%<br />

7%<br />

6%<br />

5%<br />

4%<br />

3%<br />

2%<br />

1%<br />

0%<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 27<br />

P6<br />

Benchmark Suite: SPEC89<br />

Local<br />

Correlating<br />

Tournament<br />

0 8 16 24 32 40 48 56 64 72 80 88 96 104 1<strong>12</strong> <strong>12</strong>0 <strong>12</strong>8<br />

Branch Pre<strong>di</strong>ction case study<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L01, Slide 28<br />

Total pre<strong>di</strong>ctor size (Kbits)<br />

Grafico da [Hennessy02]

Branch Pre<strong>di</strong>ction nel P6 [Shen02]<br />

• Risoluzione <strong>del</strong> branch (taken/not taken)<br />

• E’ effettuata nella JEU (Jump Execution Unit)<br />

• Il BTB pre<strong>di</strong>ce il target non appena la IFU (Instruction Fetch Unit) lo<br />

preleva<br />

• Tutti gli in<strong>di</strong>rizzi sono verificati dal BAC (Branch Address Calculator) o<br />

dalla JEU<br />

• Branch Target Buffer (BTB)<br />

• Opera nei primi sta<strong>di</strong> <strong>del</strong>la pipeline<br />

• Parte dall’in<strong>di</strong>rizzo <strong>del</strong>l’IP (Instruction Pointer) e produce una<br />

pre<strong>di</strong>zione <strong>del</strong>l’esito e <strong>del</strong> target<br />

• L’in<strong>di</strong>rizzo target predetto viene inviato alla IFU per il prelievo<br />

• Aggiornamento <strong>del</strong> BTB<br />

• Il BTB viene aggiornato non appena la JEU risolve il branch<br />

• Questo puo’ essere troppo tar<strong>di</strong> se il branch successivo arriva<br />

nelle istruzioni imme<strong>di</strong>atamente successive<br />

-Il BTB viene pertanto speculaticamente aggiornato al momento <strong>del</strong>la pre<strong>di</strong>zione<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 29<br />

P6 - Algoritmo <strong>di</strong> Branch Pre<strong>di</strong>ction<br />

• Basato sullo schema 2-level adaptive [Yeh92]<br />

• Primo livello – storia degli esiti dei branch<br />

• Secondo livello – comportamento <strong>del</strong> branch per un dato pattern <strong>di</strong> storia<br />

• Differenze rispetto a [Yeh92]<br />

- C’e’ una copia speculativa <strong>del</strong> BHT che consente <strong>di</strong> effettuare le pre<strong>di</strong>zioni prima che si<br />

abbia la risoluzione (e l’aggiornamento)<br />

• Per ogni branch…<br />

• Il BTB mantiene k bit <strong>di</strong> storia “reale” (detta BHR ==BHT)<br />

- Taken/Not-taken per gli ultimi N salti<br />

• Il BHT in<strong>di</strong>cizza una tabella <strong>di</strong> 2k elementi <strong>di</strong> stato (Pattern Table – PT ==PHT)<br />

- La FSM relativa e’ il solito contat<strong>ore</strong> a saturazione<br />

• La BTB usa 4-bit <strong>di</strong> pattern table “semilocale” per set<br />

• Ogni elemento ha 4 bit <strong>di</strong> storia<br />

• Quattro branch in un set usano la stessa pattern table<br />

• Aggiornamento speculativo <strong>del</strong> BHR<br />

• Una copia speculativa <strong>del</strong> BHR viene aggiornata con l’attuale pre<strong>di</strong>zione<br />

- Tale copia viene utilizzata nel caso arrivi un branch prima che il precedente sia risolto<br />

• La BHR reale viene aggiornato con l’esito effettivo dopo la risoluzione <strong>del</strong> branch<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 30

Algoritmo <strong>di</strong> Branch Pre<strong>di</strong>ction - BTB<br />

• BTB e’ sud<strong>di</strong>visa in due sta<strong>di</strong><br />

• Il motivo e’ dovuto alla velocita’ <strong>del</strong> circuito<br />

• I branch predetti “taken” inseriscono una bolla nella pipeline<br />

• Se non c’e’ hit nel BTB<br />

• Si utilizza una pre<strong>di</strong>zione <strong>di</strong> tipo statico<br />

• BTFN=Bachward Taken, Forward Not-taken<br />

• Return stack<br />

• La BTB mantiene inoltre un “return stack” [Kaeli91] <strong>di</strong> 16 elementi<br />

• Questo aiuta a pre<strong>di</strong>rre l’in<strong>di</strong>rizzo <strong>di</strong> ritorno <strong>del</strong>le funzioni<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 31<br />

PENTIUM 4 & PENTIUM M<br />

Branch Pre<strong>di</strong>ction case study<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L01, Slide 32

P4 - Branch pre<strong>di</strong>ction [Boggs03]<br />

• Secondo Intel, il piu’ sofisticato schema <strong>di</strong> pre<strong>di</strong>zione al 2007<br />

• Non molti dettagli sono <strong>di</strong>sponibili<br />

• Si avvale <strong>di</strong> due maniere <strong>di</strong> pre<strong>di</strong>rre il branch (simile al P6)<br />

• Se BTB fa hit si usa tale pre<strong>di</strong>zione<br />

• In caso contrario si usa una pre<strong>di</strong>zine statica<br />

• Miglioramenti introdotti nel Pentium M [Gochman03]<br />

- Pre<strong>di</strong>zione dei branch in<strong>di</strong>retti<br />

- Rivelat<strong>ore</strong> <strong>di</strong> loop<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 33<br />

P4 - Branch Pre<strong>di</strong>ction statica<br />

• Generazioni precedenti<br />

• I “backward branch” venivano sempre “taken”<br />

• Backward branches nel P4<br />

• Si controlla se ricade su una chiusura <strong>di</strong> un loop oppure no<br />

- La decisione si basa su una soglia definita in maniera empirica<br />

-Se offset < soglia allora deduco che sono nel caso <strong>di</strong> una chiusa <strong>di</strong> loop pre<strong>di</strong>co taken<br />

-Se offset > soglia deduco che NON sono nel caso <strong>di</strong> una chiusa <strong>di</strong> loop pre<strong>di</strong>co not-taken<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 34

P4 – Pre<strong>di</strong>zione <strong>di</strong>namica dei branch<br />

• Il pre<strong>di</strong>tt<strong>ore</strong> e’ 8 volte piu’ grande <strong>di</strong> quello <strong>del</strong> P6 (4KB)<br />

• L’algoritmo preciso non e’ stato <strong>di</strong>vulgato<br />

• Il pre<strong>di</strong>tt<strong>ore</strong> si combina con la Trace Cache<br />

• La Trace Cache sostituisce la Cache Istruzioni<br />

• Componenti<br />

• Return Address Stack – 16 elementi (v. [Kaeli91])<br />

• In<strong>di</strong>rect Branch Pre<strong>di</strong>ctor (v. slide successiva)<br />

• Loop detector (v. due slide avanti)<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 35<br />

In<strong>di</strong>rect Branch Pre<strong>di</strong>ctor<br />

• Risolve i branch in<strong>di</strong>retti <strong>di</strong>pendenti dai dati<br />

• Sono molto frequenti nei programmi object-oriented (Java, C++)<br />

• Ci sono due casi<br />

• Branch in<strong>di</strong>retti con 1 target (piu’ facili da pre<strong>di</strong>rre)<br />

• Branch in<strong>di</strong>retti con piu’ target (es. statement “case”)<br />

in cui il target <strong>di</strong>pende dai dati <strong>del</strong> programma<br />

• Il pre<strong>di</strong>tt<strong>ore</strong> <strong>di</strong>fferenzia fra questi due casi<br />

• Data-independent<br />

- Viene usato solo l’IP per selezionare il branch target<br />

- Si memorizza il target in una tabella in<strong>di</strong>cizzata dall’IP<br />

• Data-dependent<br />

- Si usa la storia globale degli esiti per selezionare il branch target<br />

- Si memorizza il target in una tabella in<strong>di</strong>cizzata dalla storia globale<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 36

Loop pre<strong>di</strong>ctor<br />

• Cerca <strong>di</strong> scoprire se il branch chiude un ciclo oppure no<br />

• Un branch chiude un ciclo se salta piu’ volte in una <strong>di</strong>rezione (sia essa<br />

taken che not taken)<br />

• L’ultimo movimento avviene in <strong>di</strong>rezione opposta per terminare il loop<br />

• Questa tecnica funziona meglio <strong>di</strong> altri pre<strong>di</strong>ttori per i loop<br />

Conta quante volte questo<br />

branch ha saltato ad un<br />

dato in<strong>di</strong>rizzo<br />

Rivela quando il contat<strong>ore</strong><br />

ha raggiungo il limite per<br />

cui si ripristina<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 37<br />

0<br />

-1<br />

Count Limit Pre<strong>di</strong>ction<br />

=<br />

pre<strong>di</strong>ction<br />

Pre<strong>di</strong>ce che il loop si<br />

chiude fintanto che il<br />

contat<strong>ore</strong> e’ al <strong>di</strong> sotto <strong>del</strong><br />

limite memorizzato<br />

Suggerimenti software per la branch pre<strong>di</strong>ction<br />

• Il P4 consente al software <strong>di</strong> passare suggerimenti (hints) al<br />

process<strong>ore</strong><br />

• L’hardware <strong>di</strong> Branch Pre<strong>di</strong>ction e <strong>di</strong> formazione <strong>del</strong>la traccia<br />

consulta questa informazioni per migliorare le prestazioni<br />

• Cambiamenti nell’ISA<br />

• Le istruzioni <strong>di</strong> branch devono essere mo<strong>di</strong>ficate per supportare i<br />

suggerimenti<br />

• Si aggiungono dei prefissi ai salti con<strong>di</strong>zionali<br />

• La tecnica e’ usata solo nel momento in cui si crea la traccia<br />

• Dopo la creazione <strong>del</strong>la traccia gli hints <strong>del</strong> software non vengono piu’<br />

considerati<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 38

Prestazioni<br />

• Confronto tra due generazioni <strong>di</strong> architetture Intel (130nm vs 90nm)<br />

SPECint_base2000 130nm 90nm<br />

164.gzip 1.03 1.01<br />

175.vpr 1.32 1.21<br />

176.gcc 0.85 0.70<br />

181.mcf 1.35 1.22<br />

186.crafty 0.72 0.69<br />

197.parser 1.06 0.87<br />

252.eon 0.44 0.39<br />

253.perlbmk 0.62 0.28<br />

254.gap 0.33 0.24<br />

255.vortex 0.08 0.09<br />

256.bzip2 1.19 1.<strong>12</strong><br />

300.twolf 1.32 1.23<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 39<br />

References<br />

Nella tabella a lato si riporta il numero<br />

<strong>di</strong> mispre<strong>di</strong>ction su 100 istruzioni <strong>di</strong><br />

branch, nal caso <strong>del</strong>l’architettura P4 a<br />

130 nm e a 90 nm.<br />

Dati forniti da Intel.<br />

[Alpha99] Compaq Computer Corporation, Alpha 2<strong>12</strong>64 Microprocessor Hardware Reference<br />

Manual, 1999.<br />

[Boggs03] Boggs D., et. al. The Microarchitecture of the Intel ® Pentium ® 4 Processor on 90nm<br />

Technology. Intel ® Technology Journal, Vol 08, Issue 01, February 18, 2003.<br />

[Gochman03] Gochman S., et. al. The Intel ® Pentium ® M Processor: Microarchitecture and<br />

Performance. Intel ® Technology Journal, Vol 07, Issue 02, May 21, 2003.<br />

[Hennessy02] Hennessy, J. L. and Patterson, D. A. 2002 Computer Architecture: a Quantitative<br />

Approach. 3 rd E<strong>di</strong>tion. Morgan Kaufmann Publishers Inc. 2002.<br />

[Kaeli91] D. R. Kaeli and P. G. Emma. Branch history table pre<strong>di</strong>ction of moving target<br />

branches due to subroutine returns. In Proc. ISCA-18, pages 34–41, May 1991.<br />

[McFarling93] McFarling, S . Combining Combining branch branch pre<strong>di</strong>ctors. pre<strong>di</strong>ctors. Technical Report TN-36, Digital<br />

Western Research Laboratory, June 1993.<br />

[Pan92] S. T. Pan, K. So, and J. T. Rahmeh. Improving the accuracy of dynamic branch<br />

pre<strong>di</strong>ction using branch correlation. In Procee<strong>di</strong>ngs of ASPLOS V, pages 76–84,<br />

Boston, MA, October 1992.<br />

[Shen02] Shen J. P. , Lipasti M. Modern Processor Design, McGraw Hill Higher Education;<br />

Beta Ed e<strong>di</strong>tion (November 1, 2002).<br />

[Yeh93-ics] Yeh, T., Marr, D. T., and Patt, Y. N. 1993. Increasing the instruction fetch rate via<br />

multiple branch pre<strong>di</strong>ction and a branch address cache. In Procee<strong>di</strong>ngs of the 7th<br />

International Conference on Supercomputing (Tokyo, Japan, July 19 - 23, 1993).<br />

[Uht95] Uht, A. K., Sindagi, V., Hall, K. Disjoint eager execution: an optimal form of<br />

speculative execution. In Procee<strong>di</strong>ngs of the 28th Annual international Symposium<br />

on Microarchitecture (Dec. 1995).<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 40