Uitwerking

Uitwerking

Uitwerking

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

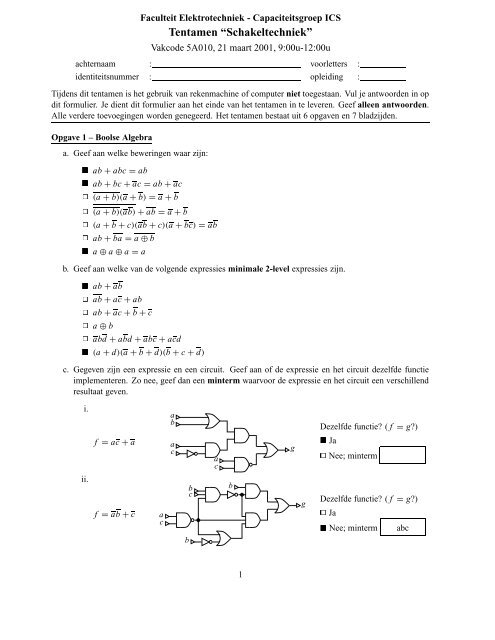

Faculteit Elektrotechniek - Capaciteitsgroep ICS<br />

Tentamen “Schakeltechniek”<br />

Vakcode 5A010, 21 maart 2001, 9:00u-12:00u<br />

achternaam : voorletters :<br />

identiteitsnummer : opleiding :<br />

Tijdens dit tentamen is het gebruik van rekenmachine of computer niet toegestaan. Vul je antwoorden in op<br />

dit formulier. Je dient dit formulier aan het einde van het tentamen in te leveren. Geef alleen antwoorden.<br />

Alle verdere toevoegingen worden genegeerd. Het tentamen bestaat uit 6 opgaven en 7 bladzijden.<br />

Opgave 1 – Boolse Algebra<br />

a. Geef aan welke beweringen waar zijn:<br />

¡<br />

¡<br />

¡<br />

¡<br />

ab + abc = ab<br />

ab + bc + ac = ab + ac<br />

(a + b)(a + b) = a + b<br />

(a + b)(ab) + ab = a + b<br />

(a + b + c)(ab + c)(a + bc) = ab<br />

ab + ba = a ⊕ b<br />

a ⊕ a ⊕ a = a<br />

b. Geef aan welke van de volgende expressies minimale 2-level expressies zijn.<br />

¡<br />

¡<br />

¡<br />

¡<br />

ab + ab<br />

ab + ac + ab<br />

ab + ac + b + c<br />

a ⊕ b<br />

abd + abd + abc + acd<br />

(a + d)(a + b + d)(b + c + d)<br />

c. Gegeven zijn een expressie en een circuit. Geef aan of de expressie en het circuit dezelfde functie<br />

implementeren. Zo nee, geef dan een minterm waarvoor de expressie en het circuit een verschillend<br />

resultaat geven.<br />

i.<br />

ii.<br />

f = ac + a<br />

f = ab + c<br />

a<br />

c<br />

a<br />

b<br />

a<br />

c<br />

b<br />

b c<br />

a<br />

c<br />

b<br />

1<br />

g<br />

g<br />

Dezelfde functie? ( f = g?)<br />

Ja<br />

¡ Nee; minterm<br />

Dezelfde functie? ( f = g?)<br />

¡<br />

Ja<br />

Nee; minterm abc

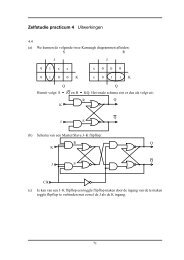

Opgave 2 – Minimaliseren<br />

Beschouw het volgende circuit met 4 ingangen.<br />

a<br />

c<br />

a<br />

b<br />

c<br />

c<br />

d<br />

a. Vul het volgende Karnaugh diagram voor f in.<br />

0<br />

1<br />

1 1<br />

1<br />

0 1 0<br />

b. Geef een minimale som van produkten expressie voor f .<br />

d<br />

0<br />

0<br />

0<br />

0<br />

a<br />

0<br />

0<br />

c<br />

acd + abc + acd<br />

Geef een minimale produkt van sommen expressie voor f .<br />

(a + c)(b + c)(a + d)(a + c + d)<br />

c. Ga er nu van uit dat de ingangen c en d van bovenstaand circuit met elkaar verbonden worden. We<br />

gebruiken deze kennis om het circuit te minimaliseren. Vul het volgende Karnaugh diagram in.<br />

0 1 x<br />

x<br />

x<br />

x x<br />

0 0<br />

Geef een minimale som van produkten expressie.<br />

d<br />

a<br />

1<br />

1<br />

x<br />

ac + ab<br />

2<br />

c<br />

0<br />

1<br />

x<br />

0<br />

0<br />

x<br />

b<br />

b<br />

f

Faculteit Elektrotechniek - Capaciteitsgroep ICS<br />

Tentamen “Schakeltechniek”<br />

Vakcode 5A010, 21 maart 2001, 9:00u-12:00u<br />

achternaam : voorletters :<br />

identiteitsnummer : opleiding :<br />

Opgave 3 – Getalrepresentaties en talstelsels<br />

a. Gegeven een aantal binaire getallen. Geef de decimale waarde van elk binair getal uitgaande van de<br />

gegeven getalrepresentatie.<br />

signed magnitude ones complement twos complement<br />

10011 −3 −12 −13<br />

01010 10 10 10<br />

b. Gegeven een aantal decimale getallen. Geef de binaire representatie van elk getal in de gegeven<br />

getalrepresentatie. Gebruik in alle gevallen 5 bits.<br />

signed magnitude ones complement twos complement<br />

11 01011 01011 01011<br />

−2 10010 11101 11110<br />

c. Streep in de volgende beweringen die getalrepresentaties door waarvoor de bewering niet waar is.<br />

- In signed magnitude / ones complement / twos complement hebben alle getallen een unieke<br />

representatie.<br />

- De meest geschikte representatie voor aritmetische berekeningen (optellen/aftrekken) is signed<br />

magnitude / ones complement / twos complement.<br />

d. Gegeven een aantal getallen in het ternaire (3-tallig) talstelsel. Geef de representatie van elk getal in<br />

de verschillende talstelsels.<br />

e. Maak de volgende optellingen af.<br />

octaal decimaal hexadecimaal<br />

21 7 7 7<br />

12102 222 146 92<br />

binair : ternair :<br />

001011 + 000110 = 010001 001011 + 022021 = 100102<br />

octaal : hexadecimaal :<br />

1234 + 4176 = 5432 5241 + 47CF = 9A10<br />

3

Opgave 4 – Tijddiagrammen en gatedelays<br />

Beschouw het volgende circuit met 3 ingangen.<br />

a b<br />

a c<br />

c<br />

d<br />

e<br />

a. Ga er van uit dat alle poorten een vertraging van 1 tijdeenheid hebben. Maak het volgende tijddiagram<br />

af.<br />

a<br />

b<br />

c<br />

d<br />

e<br />

f<br />

g<br />

b. Gegeven het volgende tijddiagram. Leidt hier uit af wat de vertragingen van de verschillende poorten<br />

zijn, uitgedrukt in tijdeenheden. Ga er van uit dat alle poorten een minimale vertraging van 1 tijdeenheid<br />

hebben.<br />

a<br />

b<br />

c<br />

g<br />

and 1 or 1<br />

nand 1 xor 2<br />

4<br />

f<br />

g

Faculteit Elektrotechniek - Capaciteitsgroep ICS<br />

Tentamen “Schakeltechniek”<br />

Vakcode 5A010, 21 maart 2001, 9:00u-12:00u<br />

achternaam : voorletters :<br />

identiteitsnummer : opleiding :<br />

Opgave 5 – CMOS<br />

Gegeven de volgende CMOS netwerken. Met welke expressie(s) kan de functie van het netwerk worden<br />

uitgedrukt? (Let op: per onderdeel kunnen meerdere antwoorden juist zijn.)<br />

a<br />

b<br />

a<br />

¡<br />

¡<br />

¡<br />

a<br />

c<br />

b<br />

c<br />

f<br />

f = ab + c<br />

f = ab + c<br />

f = (a + b)c<br />

f = (a + b)c<br />

¡<br />

¡<br />

¡<br />

b<br />

f = a + b<br />

f = a + b<br />

f = a + b<br />

f = a ⊕ b<br />

b<br />

f<br />

a c<br />

b<br />

¡<br />

¡<br />

b<br />

5<br />

b<br />

c<br />

a<br />

f = b + ac<br />

f = b + ac<br />

f = (a + c)b<br />

f = (a + c)b<br />

¡<br />

¡<br />

¡<br />

a<br />

a<br />

f = a + b + ab<br />

f = a + b + ab<br />

f = a ⊕ b<br />

f = a ⊕ b<br />

f<br />

b<br />

a<br />

b<br />

f

Opgave 6 – Mealy machines<br />

We gaan een Mealy machine ontwerpen die aan de volgende specificatie voldoet. Het circuit heeft 2 ingangen;<br />

deze ingangen coderen een 2-bits getal. Het circuit telt 2 2-bits getallen bij elkaar op, namelijk het getal<br />

dat in de huidige klok cycle op de ingang staat en het getal dat in de vorige cycle op de ingang stond. In de<br />

eerste cycle is dit laatste getal natuurlijk niet gedefinieerd; het circuit dient dan uit te gaan van het getal 0.<br />

Het resultaat van de optelling wordt in binaire vorm via een aantal uitgangen als uitvoer gegeven.<br />

a. Teken een toestandsdiagram voor de gevraagde Mealy machine.<br />

11/011<br />

00/000<br />

00/001<br />

0<br />

01/001<br />

00/010<br />

01/100<br />

1<br />

3<br />

11/110<br />

00/011<br />

10/010<br />

11/100<br />

10/101<br />

11/101<br />

01/011<br />

01/010<br />

2<br />

10/100<br />

10/011<br />

b. Ga er van uit dat de Mealy machine met behulp van D-flipflops gemaakt wordt. Geef een toestandscodering<br />

en vul de volgende waarheidstabel in.<br />

toestand Q1 Q0<br />

0 0 0<br />

1 0 1<br />

2 1 0<br />

3 1 1<br />

i1 i0 Q1 Q0 D1 D0 o2 o1 o0<br />

0 0 0 0 0 0 0 0 0<br />

0 0 0 1 0 0 0 0 1<br />

0 0 1 0 0 0 0 1 0<br />

0 0 1 1 0 0 0 1 1<br />

0 1 0 0 0 1 0 0 1<br />

0 1 0 1 0 1 0 1 0<br />

0 1 1 0 0 1 0 1 1<br />

0 1 1 1 0 1 1 0 0<br />

1 0 0 0 1 0 0 1 0<br />

1 0 0 1 1 0 0 1 1<br />

1 0 1 0 1 0 1 0 0<br />

1 0 1 1 1 0 1 0 1<br />

1 1 0 0 1 1 0 1 1<br />

1 1 0 1 1 1 1 0 0<br />

1 1 1 0 1 1 1 0 1<br />

1 1 1 1 1 1 1 1 0<br />

6

Faculteit Elektrotechniek - Capaciteitsgroep ICS<br />

Tentamen “Schakeltechniek”<br />

Vakcode 5A010, 21 maart 2001, 9:00u-12:00u<br />

achternaam : voorletters :<br />

identiteitsnummer : opleiding :<br />

c. Teken een implementatie in de volgende PLA. Vergeet niet de in- en uitgangen namen te geven.<br />

Q0<br />

D0<br />

Q1<br />

D1<br />

i1<br />

i0<br />

o2 o1<br />

d. Teken een implementatie die slechts gebruik maakt van D-flipflops, halfadders en fulladders.<br />

i0<br />

i1<br />

D0<br />

D1<br />

7<br />

Q0<br />

Q1<br />

HA<br />

FA<br />

o0<br />

o1<br />

o2<br />

o0