Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

,ceil(T,<br />

节<br />

的<br />

个<br />

的<br />

选<br />

块<br />

或<br />

块<br />

块<br />

或<br />

,B<br />

或<br />

所<br />

个<br />

节<br />

块<br />

或<br />

。<strong>CUDA</strong><br />

,T<br />

或<br />

个<br />

5.2 每 个 块 的 线 程 数 量<br />

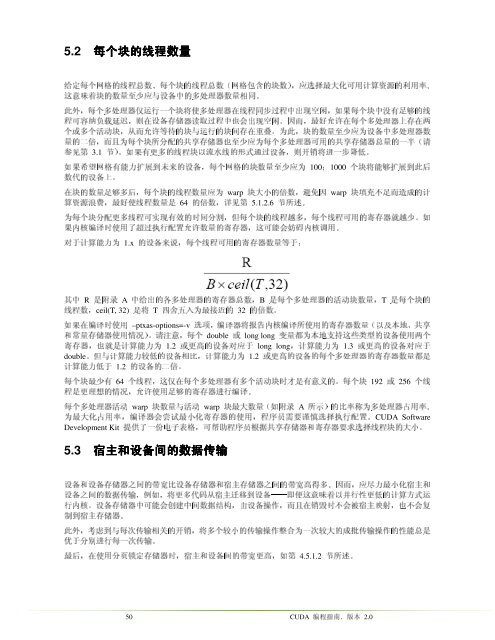

定 每 个 网 格 的 线 程 总 数 、 每 线 程 总 数 ( 网 格 包 含 的 块 数 ), 应 选 择 最 大 化 可 用 计 算 资 源 的 利 用 率 。 这 意 味 着 块 的 数 量 至 少 应 与 设 备 中 的 多 处 理 器 数 量 相 同 。 此 外 , 每 个 多 处 理 器 仅 运 行 一 个 块 将 使 多 处 理 器 在 线 程 同 步 过 程 中 出 现 空 闲 , 如 果 每 个 块 中 没 有 足 够 的 线 给<br />

程 可 容 纳 负 载 延 迟 , 则 在 设 备 存 储 器 读 取 过 程 中 也 会 出 现 空 闲 。 因 而 , 最 好 允 许 在 每 个 多 处 理 器 上 存 在 两<br />

或 多 个 活 动 块 , 从 而 允 许 等 待 块 与 运 行 的 块 间 存 在 重 叠 。 为 此 , 块 的 数 量 至 少 应 为 设 备 中 多 处 理 器 数 量 的 二 倍 , 而 且 为 每 个 块 所 分 配 的 共 享 存 储 器 也 至 少 应 为 每 个 多 处 理 器 可 用 的 共 享 存 储 器 总 量 的 一 半 ( 请 参 见 )。 如 果 有 更 多 的 线 程 块 以 流 水 线 的 形 式 通 过 设 备 , 则 开 销 将 进 一 步 降 低 。 个<br />

代 的 设 备 上 。 的 节 数<br />

每 个 块 分 配 更 多 线 程 可 实 现 有 效 的 时 间 分 割 , 但 每 个 块 的 线 程 越 多 , 每 个 线 程 可 用 的 寄 存 器 就 越 少 。 如 为<br />

第 3.1<br />

线 程 数<br />

附<br />

出 的 各 多 处 理 器 的 寄 存 器 总 数 每 个 多 处 理 器 的 活 动 块 数 量 倍 数 。 给<br />

每 个 块 的<br />

32) 是 中 是<br />

四<br />

的<br />

是<br />

是<br />

100;1000 希 望 网 格 有 能 力 扩 展 到 未 来 的 设 备 , 每 个 网 格 的 块 数 量 至 少 应 为 果 如<br />

块 将 能 够 扩 展 到 此 后<br />

内 核 编 译 时 使 用 了 超 过 执 行 配 置 允 许 数 量 的 寄 存 器 , 这 可 能 会 妨 碍 内 核 调 用 。 果<br />

warp 的 数 量 足 够 多 后 , 每 个 块 的 线 程 数 量 应 为 块 在<br />

warp 的 倍 数 , 避 免 因 小 大<br />

填 充 不 足 而 造 成 的 计<br />

64 源 浪 费 , 最 好 使 线 程 数 量 是 资 算<br />

5.1.2.6 , 详 见 第 数 倍<br />

述 。 所<br />

1.x 计 算 能 力 为 于 对<br />

备 来 说 , 每 个 线 程 可 用 的 寄 存 器 数 量 等 于 : 设<br />

long<br />

long, 计 变<br />

R 中 其<br />

录 A<br />

将 T<br />

32 入 为 最 接 近 的 五 舍<br />

–ptxas-options=-v 在 编 译 时 使 用 果 如<br />

, 编 译 器 将 报 告 内 核 编 译 所 使 用 的 寄 存 器 数 量 ( 以 及 本 地 、 共 享 更 高 的 设 备 的 每 个 多 处 理 器 的 寄 存 器 数 量 都 是 项<br />

double 量 存 储 器 使 用 情 况 )。 请 注 意 , 每 个 常 和<br />

long<br />

量 都 为 本 地 支 持 这 些 类 型 的 设 备 使 用 两 个<br />

最 大 化 占 用 率 , 编 译 器 会 尝 试 最 小 化 寄 存 器 的 使 用 , 程 序 员 需 要 谨 慎 选 择 执 行 配 置 供 了 一 份 电 子 表 格 , 可 帮 助 程 序 员 根 据 共 享 存 储 器 和 寄 存 器 要 求 选 择 线 程 块 的 大 小 。 为<br />

1.2 器 , 也 就 是 计 算 能 力 为 存 寄<br />

更 高 的 设 备 对 应<br />

高 的 设 备 对 应 于 更<br />

Development Kit 提<br />

Software<br />

线<br />

于 long<br />

1.3 力 为 能 算<br />

但 计 算 能 力 低<br />

double。<br />

1.2 算 能 力 较 低 的 设 备 相 比 , 计 算 能 力 为 计 与<br />

于 1.2<br />

5.3 宿 主 和 设 备 间 的 数 据 传 输<br />

备 的 二 倍 。 程 是 更 理 想 的 情 况 , 允 许 使 用 足 够 的 寄 存 器 进 行 编 译 。 设<br />

64 块 最 少 有 个 每<br />

192 , 这 仅 在 每 个 多 处 理 器 有 多 个 活 动 块 时 才 是 有 意 义 的 。 每 个 块 程 线<br />

256<br />

warp 多 处 理 器 活 动 个 每<br />

warp 与 活 动 量 数<br />

A 数 量 ( 如 附 录 大 最<br />

示 ) 的 比 率 称 为 多 处 理 器 占 用 率 。<br />

和 设 备 存 储 器 之 间 的 带 宽 比 设 备 存 储 器 和 宿 主 存 储 器 之 间 的 带 宽 高 得 多 。 因 而 , 应 尽 力 最 小 化 宿 主 和 设 备 之 间 的 数 据 传 输 , 例 如 , 将 更 多 代 码 从 宿 主 迁 移 到 设 备 —— 即 便 这 意 味 着 以 并 行 性 更 低 的 计 算 方 式 运 行 内 核 。 设 备 存 储 器 中 可 能 会 创 建 中 间 数 据 结 构 , 由 设 备 , 而 且 在 销 毁 时 不 会 被 宿 主 映 射 , 也 不 会 复 制 到 宿 主 存 储 器 。<br />

外 , 考 虑 到 与 每 相 关 的 开 销 , 将 多 个 较 小 的 传 输 操 作 整 合 为 一 次 较 大 的 成 批 传 输 操 作 的 性 能 总 是 优 于 分 别 进 行 每 一 次 传 输 。 此<br />

50 <strong>CUDA</strong> 编<br />

4.5.1.2 , 在 使 用 分 页 锁 定 存 储 器 时 , 宿 主 和 设 备 间 的 带 宽 更 高 , 如 第 后 最<br />

述 。 所<br />

2.0 南 , 版 本 指 程