Elektroniktidningen

Elektroniktidningen

Elektroniktidningen

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

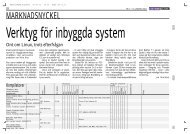

SoC FPGAsCompany AnnouncementUser-customisableARM-based SoCsAuthor: Todd Koelling, senior manager,embedded products, at Altera.Today’s highly competitive market is forcingembedded systems designers to re-examine theirdesign and development process. Increasingsystem complexity, performance, power and spaceconstraints push the limits of conventionalmethods. At the same time, evolving standards,emerging markets and shifting trends require agreat deal more agility and responsiveness in thedesign process. Designers not only need to createmuch more complex systems, but also need to beable to very rapidly turn new or derivative designs.One market development that is actuallyadvantageous to designers is the emergence ofthe ARM processor as the dominant platform forembedded systems. As a result, a growingnumber of ARM-based solutions have emerged,from standard products, to soft ARM IP cores, tohard IP for implementation in programmablelogic and ASIC.Multichip solutions are relatively easy toimplement, but are costly and often lack theflexibility and performance/power designersneed. Single-chip solutions that employ softprocessor cores are also relatively easy toimplement, but are limited in their performance.At the other end of the spectrum, ASIC SoCswith on-board hardened ARM cores offerexcellent power, performance, and optimisation,but are slow to market due to developmenttimes, inflexible, and too costly for the vastmajority of applications.Single-chip FPGA-based implementation, with itslow cost and fast time-to-market, offers anintuitively attractive alternative to multi-chip andASIC SoC options. Traditionally, FPGA-basedARM systems have been implemented usingHDL-based “soft” ARM cores. However, for agrowing spectrum of systems, the combination ofa highly optimised, hardened ARM core on anFPGA platform offers a superior solution.The ARM-based SoC FPGA (as shown in Figure2) tightly couples a highly optimised “hard”processor system (HPS) with an on-chip FPGA.The HPS, which includes the dual-core ARMprocessor, multiport memory controller andmultiple peripheral elements, offers up to 4,000MIPS (Dhrystones 2.1 benchmark) of processingperformance for under 1.8 W. These hard IPblocks offer high performance while loweringpower and cost, and freeing up logic resourcesfor product differentiation. On-chip FPGA fabriccan be customised by the designer to createapplication-specific logic. Programmability allowsthe flexibility to adapt designs to new or changingcommunications standards, networkingprotocols, and performance tuning.Design teams deploying FPGA SoC technologycan capitalise on its significant productivity andcompetitive advantages. Hard IP elementsdeliver the best performance, lowest power andhighest density possible, while on-chip FPGAfabric offers the ability to rapidly differentiate,augment and/or customise functionality, duringdesign or in the field. The field-programmableplatform, combined with highly automated andwell-supported design and softwaredevelopment tools, enables the design team todevelop a custom SoC, using off-the-shelfdevices, in a fraction of the time of ASIC ormulti-chip devices.A tipping point has been reached at whichFPGA-based SoC has emerged as a viable andadvantageous solution over conventional designapproaches for today’s embedded systemapplications. With this powerful capability,designers can not only surmount their mostpressing execution challenges, but also stand togain significant time-to-market, price/performance,product differentiation and longevity advantages.Figure 2 FPGA SoC IntegrationSoC FPGA at a Glance• Increased system performance• Dual-core ARM Cortex-A9 MPCoreprocessor• 4,000 DMIPS for under 1.8W• >125 Gbps processor to FPGAinterconnect• Integrated Hard IP delivers performanceadvantages• Reduced power consumption• Up to 30% power savings vs. 2-chipsolution• Reduced board size• Up to 55% form factor reduction• Reduced system costs• Lower component cost• Reduction in PCB complexity and cost• Development Flow• Standard Altera hardware developmentflow• Proven Virtual Target softwareprototyping methodology• ARM’s ecosystem supportFigure 1 Growth of Processors in FPGA120,000Without CPUWith CPU100,000Design Starts80,00060,00040,00050%20,00001999 2000 2001 2002 2003 2004 2005 2006 2007 2008 2009 2010 2011 2012 2013 2014Source: Gartner Sept 2010Scan to learn moreVisit http://www.altera.com/devices/processor/soc-fpga/proc-soc-fpga.html for more information