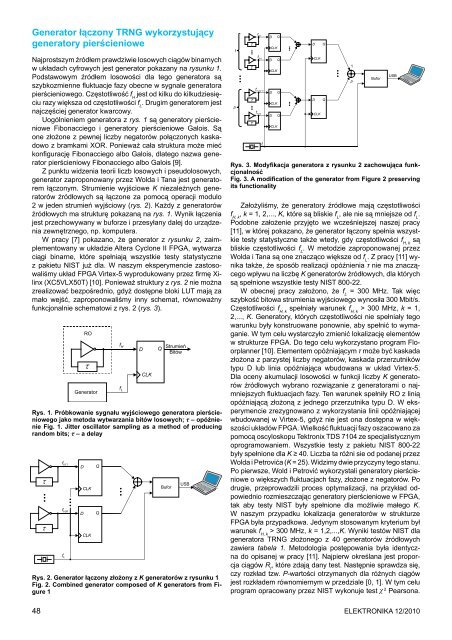

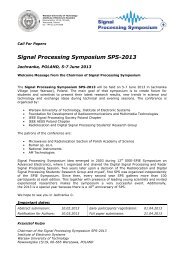

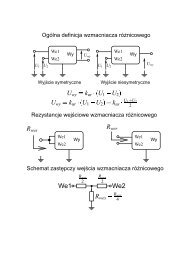

Generator łączony TRNG wykorzystującygeneratory pierścienioweNajprostszym źródłem prawdziwie losowych ciągów binarnychw układach cyfrowych jest generator pokazany na rysunku 1.Podstawowym źródłem losowości dla tego generatora sąszybkozmienne fluktuacje fazy obecne w sygnale generatorapierścieniowego. Częstotliwość f Hjest od kilku do kilkudziesięciurazy większa od częstotliwości f L. Drugim generatorem jestnajczęściej generator kwarcowy.Uogólnieniem generatora z rys. 1 są generatory pierścienioweFibonacciego i generatory pierścieniowe Galois. Sąone złożone z pewnej liczby negatorów połączonych kaskadowoz bramkami XOR. Ponieważ cała struktura może miećkonfigurację Fibonacciego albo Galois, dlatego nazwa generatorpierścieniowy Fibonacciego albo Galois [9].Z punktu widzenia teorii liczb losowych i pseudolosowych,generator zaproponowany przez Wolda i Tana jest generatoremłączonym. Strumienie wyjściowe K niezależnych generatorówźródłowych są łączone za pomocą operacji modulo2 w jeden strumień wyjściowy (rys. 2). Każdy z generatorówźródłowych ma strukturę pokazaną na rys. 1. Wynik łączeniajest przechowywany w buforze i przesyłany dalej do urządzeniazewnętrznego, np. komputera.W pracy [7] pokazano, że generator z rysunku 2, zaimplementowanyw układzie Altera Cyclone II FPGA, wytwarzaciągi binarne, które spełniają wszystkie testy statystycznez pakietu NIST już dla. W naszym eksperymencie zastosowaliśmyukład FPGA Virtex-5 wyprodukowany przez firmę Xilinx(XC5VLX50T) [10]. Ponieważ struktury z rys. 2 nie możnazrealizować bezpośrednio, gdyż dostępne bloki LUT mają zamało wejść, zaproponowaliśmy inny schemat, równoważnyfunkcjonalnie schematowi z rys. 2 (rys. 3).Rys. 1. Próbkowanie sygnału wyjściowego generatora pierścieniowegojako metoda wytwarzania bitów losowych; τ – opóźnienieFig. 1. Jitter oscillator sampling as a method of producingrandom bits; τ – a delayRys. 2. Generator łączony złożony z K generatorów z rysunku 1Fig. 2. Combined generator composed of K generators from Figure148Rys. 3. Modyfikacja generatora z rysunku 2 zachowująca funkcjonalnośćFig. 3. A modification of the generator from Figure 2 preservingits functionalityZałożyliśmy, że generatory źródłowe mają częstotliwościf H, k, k = 1, 2,..., K, które są bliskie f L, ale nie są mniejsze od f L.Podobne założenie przyjęto we wcześniejszej naszej pracy[11], w której pokazano, że generator łączony spełnia wszystkietesty statystyczne także wtedy, gdy częstotliwości f H, ksąbliskie częstotliwości f L. W metodzie zaproponowanej przezWolda i Tana są one znacząco większe od f L. Z pracy [11] wynikatakże, że sposób realizacji opóźnienia τ nie ma znaczącegowpływu na liczbę K generatorów źródłowych, dla którychsą spełnione wszystkie testy NIST 800-22.W obecnej pracy założono, że f L= 300 MHz. Tak więcszybkość bitowa strumienia wyjściowego wynosiła 300 Mbit/s.Częstotliwości f H, kspełniały warunek f H, k> 300 MHz, k = 1,2,..., K. Generatory, których częstotliwości nie spełniały tegowarunku były konstruowane ponownie, aby spełnić to wymaganie.W tym celu wystarczyło zmienić lokalizację elementóww strukturze FPGA. Do tego celu wykorzystano program Floorplanner[10]. Elementem opóźniającym τ może być kaskadazłożona z parzystej liczby negatorów, kaskada przerzutnikówtypu D lub linia opóźniająca wbudowana w układ Virtex-5.Dla oceny akumulacji losowości w funkcji liczby K generatorówźródłowych wybrano rozwiązanie z generatorami o najmniejszychfluktuacjach fazy. Ten warunek spełniły RO z liniąopóźniającą złożoną z jednego przerzutnika typu D. W eksperymenciezrezygnowano z wykorzystania linii opóźniającejwbudowanej w Virtex-5, gdyż nie jest ona dostępna w większościukładów FPGA. Wielkość fluktuacji fazy oszacowano zapomocą oscyloskopu Tektronix TDS 7104 ze specjalistycznymoprogramowaniem. Wszystkie testy z pakietu NIST 800-22były spełnione dla K ≥ 40. Liczba ta różni sie od podanej przezWolda i Petrovića (K = 25). Widzimy dwie przyczyny tego stanu.Po pierwsze, Wold i Petrović wykorzystali generatory pierścienioweo większych fluktuacjach fazy, złożone z negatorów. Podrugie, przeprowadzili proces optymalizacji, na przykład odpowiedniorozmieszczając generatory pierścieniowe w FPGA,tak aby testy NIST były spełnione dla możliwie małego K.W naszym przypadku lokalizacja generatorów w strukturzeFPGA była przypadkowa. Jedynym stosowanym kryterium byłwarunek f H, k> 300 MHz, k = 1,2,...,K. Wyniki testów NIST dlageneratora TRNG złożonego z 40 generatorów źródłowychzawiera tabela 1. Metodologia postępowania była identycznado opisanej w pracy [11]. Najpierw określana jest proporcjaciągów R t, które zdają dany test. Następnie sprawdza się,czy rozkład tzw. P-wartości otrzymanych dla różnych ciągówjest rozkładem równomiernym w przedziale [0, 1]. W tym celuprogram opracowany przez NIST wykonuje test χ 2 Pearsona.<strong>Elektronika</strong> <strong>12</strong>/<strong>2010</strong>

Tab. 1. Wyniki testów statystycznych NIST 800-22 dla generatora łączonego(K = 40)Tab. 1. The results of NIST 800-22 statistical for the combined generator(K = 40)Rodzaj testuPojedynczygeneratorGeneratorłączonyR βP TR βP TTest częstości 0,0010 0,00000 0,9870 0,34085Blokowy test częstości 1,0000 0,00000 0,9910 0,37110Test skumulowanych sum* 0,0270 0,00000 0,9860 0,20607Test ciągów 0,0000 0,00000 0,9930 0,49929Test na najdłuższy ciągjedynek w blokuTest stopnia macierzybinarnej0,0000 0,00000 0,9885 0,964690,0000 0,00000 0,9895 0,66313Test spektralny DFT 0,0000 0,00000 0,9910 0,79156Test dopasowania nienakładającychsię wzorców*Test dopasowanianakładających się wzorców0,0000 0,00000 0,9835 0,018220,0000 0,00000 0,9865 0,38382Test uniwersalny Maurera 0,0000 0,00000 0,9835 0,0<strong>12</strong>60Test przybliżonej entropii 0,0000 0,00000 0,9920 0,08276Test błądzenia losowego* – – 0,9836 0,00053Test wariancji błądzenialosowego**0,1782 0,00000 0,9853 0,02044Test serii* 0,0000 0,00008 0,9860 0,34404Dla testu oblicza się P-wartość, oznaczaną jako P T. Jeżeli R tjest większe od R min= 0,98332542, a P Tjest nie mniejsze od0,0001, to przyjmuje się, że badany ciąg spełnia dany test.Liczbę R min= 0,98332542 otrzymujemy dla poziomu istotnościtestów β = 0,01 oraz dla 2000 badanych ciągów, każdy o długości10 6 bitów [5], [11]. Symbol „*” oznacza, że test składasię z kilku testów szczegółowych, a w tabeli pokazano wyniknajgorszy. Zapis „**” wskazuje, że najmniejsza wartość potrzebnado zaliczenia tego testu, złożonego z kilku testówszczegółowych, wynosi 0,9815 (w tabeli pokazano wyniknajgorszy).Rozróżnianie losowości i pseudolosowościw generatorach TRNGW pracy [9] zauważono, że sygnał wyjściowy generatorapierścieniowego zawiera zarówno fluktuacje fazy o charakterzeniedeterministycznym, co jest pożądane dla zastosowańw kryptografii oraz deterministycznym. Ponieważ testy statystycznemogą spełnić ciągi wytwarzane przez źródła niedeterministycznelub deterministyczne, istotne jest dysponowanienarzędziem, które rozróżni oba źródła. Jeżeli testy są spełnionedla źródeł wytwarzających wyłącznie fluktuacje fazy o charakterzedeterministycznym, to mówimy o pseudolosowościgeneratora. Jeżeli zdają je ciągi wytwarzane dzięki obecnościwyłącznie fluktuacji fazy o charakterze niedeterministycznym,to mówimy o tzw. prawdziwej losowości, lub krócej, o losowościgeneratora [9]. W przypadku generatora z rysunku 1losowość od pseudolosowości możemy odróżnić za pomocąmechanizmu restartów zaproponowanego w pracy [9]. W tymcelu startujemy wielokrotnie generator z tymi samymi warunkamipoczątkowymi. W przypadku generatora pierścieniowegowystarczy zamienić negator z rysunku 1 na bramkę NANDwyzwalaną sygnałem zewnętrznym. Jeżeli spełnienie testówzawdzięczamy pseudolosowości, to po każdym restarcie powinniśmyotrzymać ten sam ciąg. W przeciwnym przypadkuciągi będą się różnić. Autorzy pracy [9] zapamiętywali przebiegiwytwarzane przez generator pierścieniowy dla 1000restartów. Ilość losowości obecna w ciągach była mierzonapoprzez obliczenie odchylenia standardowego dla 1000 krzywych(po zbiorze) w funkcji czasu. Jeżeli wartość odchyleniastandardowego była duża, to twierdzono, że w danej chwiliza generację bitu odpowiadają przede wszystkim fluktuacjefazy o charakterze niedeterministycznym. W przeciwnym raziedominujące znaczenie mają fluktuacje fazy o charakterzedeterministycznym [9].Opisane podejście zajmuje dużo czasu, wymaga dysponowaniadrogim sprzętem pomiarowym i nie dostarcza ostregokryterium, które pozwoliłoby na stwierdzenie, czy dany bitjest produktem zjawisk niedeterministycznych czy też deterministycznych.Nasza propozycja rozróżnienia losowości odpseudolosowości polega na wykonaniu M testów χ 2 zgodnościrozkładu dla N-bitowych ciągów wyjściowych generatorałączonego, gdzie N jest liczbą restartów, a M jest liczbą bitówwytwarzanych dla jednego restartu. Jeżeli dla danej chwiliczasowej m = 1,2,...,M test χ 2 jest spełniony, to uważamy, żedla danego poziomu istotności testu nie ma podstaw do odrzuceniahipotezy, iż m-ty bit otrzymano w wyniku obecnościw sygnałach generatorów pierścieniowych szybkozmiennychfluktuacji fazy o charakterze niedeterministycznym. Wartośćstatystyki χ 2 obliczano ze wzoru:( )nN2i− N ⋅ Pi χ = ∑ ,(1)i N ⋅ Pgdzie n jest liczbą rozłącznych podzbiorów zawierającychpróbki [<strong>12</strong>]. Liczba jest liczbą elementów w i-tym podzbiorze,a jest oczekiwaną liczbą elementów w tym podzbiorze. Jeżelihipoteza o zadanym rozkładzie jest prawdziwa, to statystyka(1) dąży asymptotycznie do rozkładu chi-kwadrat z n-r-1 stopniamiswobody, gdzie r jest liczbą estymowanych parametrów[<strong>12</strong>]. Wartość statystyki obliczona ze wzoru (1) jest porównywanaz wartością krytyczną odczytaną z tablic rozkładu χ 2 cz n-r-1 stopniami swobody. W naszym przypadku jest r = 0.Dla ciągu binarnego mamy n = 2, co daje jeden stopień swobody.Przyjmując poziom istności testu β = 0,01 otrzymujemywartość krytyczną statystyki równą 6,635. Jeżeli wartośćstatystyki (1) jest mniejsza od 6,635, to nie ma powodów doodrzucenia hipotezy (na poziomie istotności β = 0,01), że zerai jedynki w m-tym, N-elementowym ciągu występują z tą samączęstością. Jeżeli hipoteza o akumulowaniu ze wzrostem Kfluktuacji fazy o charakterze niedeterministycznym jest prawdziwa,to test χ 2 powinien być spełniony dla coraz mniejszychm. Tabela 2 zawiera wyniki otrzymane dla 2048 restartów generatoraz rysunku 3. Za każdym razem długość generowanegociągu wynosiła 20000 bitów. Pierwsza i czwarta kolumnazawierają liczbę generatorów źródłowych użytych do konstrukcjigeneratora łączonego. W drugiej i w piątej kolumniepodano najmniejszą wartość m (m min), dla której wartość statystykijest mniejsza od wartości krytycznej dla wszystkich chwilrównych lub większych od m. W trzeciej i w szóstej kolumniezamieszczono wartość statystyki χ 2 otrzymaną dla m min.W wyniku badań okazało się, że czas trwania wypowiedzima bardzo istotny wpływ na poziom błędów identyfikacji.Dalsze (powyżej 60s) wydłużenie tego czasu powinno skutkowaćosiągnięciem jeszcze lepszych wyników rozpoznawania.Niektóre wyniki identyfikacji prawdopodobnie zostałyzaburzone poprze nieodpowiedni dobór zbioru wypowiedzitestowych.i2<strong>Elektronika</strong> <strong>12</strong>/<strong>2010</strong> 49