Aufgabe 1_Parallelmultiplizierer

Aufgabe 1_Parallelmultiplizierer

Aufgabe 1_Parallelmultiplizierer

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

FH Giessen-Friedberg MIK-Praktikum Dipl.-Ing. (FH) M. Beuler<br />

<strong>Parallelmultiplizierer</strong><br />

<strong>Aufgabe</strong> 1<br />

<strong>Aufgabe</strong> 1: Aufbau und Simulation eines parallelen 4×4-Bit-Multiplizierers mit<br />

VHDL und ModelSim<br />

Allgemein ergibt die Multiplikation zweier nicht vorzeichenbehafteter Dualzahlen A[n]<br />

und B[m] ein (n+m)-stelliges Produkt, wobei hier n = m = 4 gewählt wird:<br />

P[2 n] = A[ n] ⋅ B[ n] mit: n = 4<br />

(1)<br />

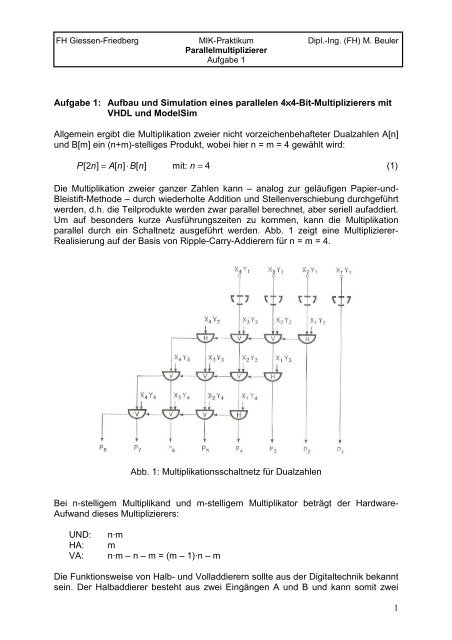

Die Multiplikation zweier ganzer Zahlen kann – analog zur geläufigen Papier-und-<br />

Bleistift-Methode – durch wiederholte Addition und Stellenverschiebung durchgeführt<br />

werden, d.h. die Teilprodukte werden zwar parallel berechnet, aber seriell aufaddiert.<br />

Um auf besonders kurze Ausführungszeiten zu kommen, kann die Multiplikation<br />

parallel durch ein Schaltnetz ausgeführt werden. Abb. 1 zeigt eine Multiplizierer-<br />

Realisierung auf der Basis von Ripple-Carry-Addierern für n = m = 4.<br />

Abb. 1: Multiplikationsschaltnetz für Dualzahlen<br />

Bei n-stelligem Multiplikand und m-stelligem Multiplikator beträgt der Hardware-<br />

Aufwand dieses Multiplizierers:<br />

UND: n·m<br />

HA: m<br />

VA: n·m – n – m = (m – 1)·n – m<br />

Die Funktionsweise von Halb- und Volladdierern sollte aus der Digitaltechnik bekannt<br />

sein. Der Halbaddierer besteht aus zwei Eingängen A und B und kann somit zwei<br />

1

FH Giessen-Friedberg MIK-Praktikum Dipl.-Ing. (FH) M. Beuler<br />

<strong>Parallelmultiplizierer</strong><br />

<strong>Aufgabe</strong> 1<br />

einstellige Binärzahlen addieren. Er besitzt zwei Ausgänge, einen für die Summe S<br />

und einen für den Übertrag Cout. Der Halbaddierer lässt sich vollständig aus NAND-<br />

Gattern aufbauen, wobei hier für die Summenbildung 3 und für die Übertragsbildung<br />

2 Gatterstufen erforderlich sind. Im Package-File wird eine Verzögerungszeit eines<br />

NAND-Gatters von 3ns eingestellt:<br />

library IEEE;<br />

use IEEE.STD_LOGIC_1164.ALL;<br />

use IEEE.STD_LOGIC_ARITH.ALL;<br />

use IEEE.STD_LOGIC_UNSIGNED.ALL;<br />

package PACK_FILE is<br />

constant N_MULT : integer := 4;<br />

constant NAND_DELAY : time := 3 ns;<br />

end PACK_FILE;<br />

Der entsprechende VHDL-Quellcode des Halbaddierers lautet:<br />

library IEEE;<br />

use IEEE.STD_LOGIC_1164.ALL;<br />

use IEEE.STD_LOGIC_ARITH.ALL;<br />

use IEEE.STD_LOGIC_UNSIGNED.ALL;<br />

use WORK.PACK_FILE.ALL;<br />

entity HALBADDER is<br />

port (A,B: in std_logic;<br />

S,Cout: out std_logic := '0'<br />

);<br />

end HALBADDER;<br />

architecture VERHALTEN of HALBADDER is<br />

begin<br />

S

FH Giessen-Friedberg MIK-Praktikum Dipl.-Ing. (FH) M. Beuler<br />

<strong>Parallelmultiplizierer</strong><br />

<strong>Aufgabe</strong> 1<br />

library IEEE;<br />

use IEEE.STD_LOGIC_1164.ALL;<br />

use IEEE.STD_LOGIC_ARITH.ALL;<br />

use IEEE.STD_LOGIC_UNSIGNED.ALL;<br />

use WORK.PACK_FILE.ALL;<br />

entity VOLLADDER is<br />

port (A,B,Cin: in std_logic;<br />

S,Cout: out std_logic := '0'<br />

);<br />

end VOLLADDER;<br />

architecture VERHALTEN of VOLLADDER is<br />

begin<br />

S

FH Giessen-Friedberg MIK-Praktikum Dipl.-Ing. (FH) M. Beuler<br />

<strong>Parallelmultiplizierer</strong><br />

<strong>Aufgabe</strong> 1<br />

Sin A B<br />

HA<br />

&<br />

Cout Sout<br />

Sin A B Cin<br />

VA<br />

&<br />

Cout Sout<br />

Abb. 2: Struktur der Module MULT_ZELLE_HA und MULT_ZELLE_VA<br />

Kalkulation der max. Rechenzeit des 4×4-Bit-Multiplizierers (Laufzeit der UND-<br />

Verknüpfung wird vernachlässigt):<br />

T = ( m −1) ⋅ T + [( n − 1) + ( m − 2)] ⋅T<br />

(2)<br />

ges HA VA<br />

<strong>Aufgabe</strong>nanleitung:<br />

1. Erstellen Sie die VHDL-Quellcodedateien HALBADDER, VOLLADDER sowie<br />

AND_2 und tragen Sie jeweils den angegebenen Quellcode ein. Das noch<br />

erforderliche Package-File ist unter ModelSim ebenfalls eine zum Projekt<br />

gehörende VHDL-Datei.<br />

2. Für die Basiszellen des Multiplizierers nach Abb. 2 sind die beiden VHDL-<br />

Dateien MULT_ZELLE_HA und MULT_ZELLE_VA mit Hilfe der unter (1)<br />

erstellten Dateien zu programmieren.<br />

3. Erstellen Sie eine VHDL-Quellcodedatei mit dem Namen MULT_MODUL. Hier<br />

erfolgen die Komponentendeklaration sowie die Komponenteninstanziierung<br />

der Multiplikations-Basiszellen nach Abb. 1, d.h. deren Verschaltung.<br />

4. Programmieren Sie ein do-File, das nach 20ns die Eingangsvektoren A[3:0]<br />

und B[3:0] setzt. Die Simulationsdauer soll insgesamt 100ns betragen.<br />

5. Folgende Simulationen sind durchzuführen und das Ergebnis dezimal und<br />

binär sowie die notwendige Rechenzeit in die Tabelle einzutragen:<br />

A (dez) B (dez) P (dez) P(bin) Rechenzeit (in ns)<br />

15 15<br />

13 9<br />

5 7<br />

9 13<br />

8 4<br />

8 8<br />

4