Das Magazin für Funk Elektronik · Computer - FTP Directory Listing

Das Magazin für Funk Elektronik · Computer - FTP Directory Listing

Das Magazin für Funk Elektronik · Computer - FTP Directory Listing

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

186 FA 2/95 SCHWARZ CYAN MAGENTA GELB<br />

Amateurfunktechnik<br />

■ Der Trick mit dem FSK-Modem<br />

Beim PC verbleibt also nur noch die Centronics-Schnittstelle.<br />

Die ist aber von Haus<br />

aus nur <strong>für</strong> die Datenausgabe geeignet<br />

(also unidirektional) und arbeitet eigentlich<br />

byteweise. Trotzdem können wir sie<br />

auch <strong>für</strong> den Datenempfang verwenden:<br />

Man kann eine der vorhandenen Hilfsleitungen<br />

<strong>für</strong> den Druckerzustand als Eingabeleitung<br />

benutzen und über eine andere<br />

Leitung auch einen Interrupt auslösen. Die<br />

Startbit/Stopbit-Problematik gibt es hier<br />

nicht; die ankommenden Signale werden<br />

(wie sie eintreffen) dem Prozessorbus<br />

übergeben. <strong>Das</strong> einzige Problem, das nun<br />

noch gelöst werden muß, ist das der zu<br />

häufigen Interrupts. Die Lösung besteht<br />

hier in einem kleinen Puffer auf dem Modem,<br />

das einige Bit (in unserem Fall boten<br />

sich 16 Bit an) zwischenspeichert.<br />

Wenn der Zwischenspeicher gefüllt ist,<br />

wird ein Interrupt ausgelöst und die 16 Bit<br />

können während dieses einen Interrupts<br />

seriell in einem „Datenburst“ auf der<br />

Hilfsleitung zum PC gelangen: Schon ist<br />

die Interruptrate auf 1/16 reduziert – und<br />

das macht 9600- oder sogar 19200-Baud-<br />

Betrieb mit dem Modem möglich, ohne<br />

daß die Interruptrate <strong>für</strong> den PC höher<br />

liegt als bei 1200 Baud. Der Sendebetrieb<br />

kann in ähnlicher Weise abgewickelt werden.<br />

Andererseits bedeutet der Puffer<br />

natürlich zusätzlichen Aufwand – und den<br />

wollten wir ja eigentlich vermeiden. Doch<br />

kann man aber einige Modemfunktionen<br />

in die Software verlagern, wie das nach<br />

dem G3RUH-Standard vorgesehene Verwürfeln<br />

(Scrambeln) der Daten und die<br />

aufwendige Signalerkennungsschaltung<br />

(DCD), so daß der Mehraufwand <strong>für</strong> den<br />

Puffer wieder ausgeglichen wird.<br />

■ Übersichtsschaltplan<br />

Bild 1 zeigt den Übersichtsschaltplan des<br />

Modems. Es ist mit insgesamt sechs Signalleitungen<br />

an die Centronics-Schnittstelle<br />

des PCs angebunden. Die Übertragung der<br />

Sende- und Empfangsdaten erfolgt dabei<br />

seriell, da die Centronics-Schnittstelle nur<br />

vier Eingangsleitungen besitzt. Die Anordnung<br />

der übrigen Blöcke entspricht dem<br />

Standard-G3RUH-Modem in der Version<br />

von DF9IC [2].<br />

Die Sende- und Empfangsdaten laufen,<br />

wie bereits erwähnt, in Bursts von jeweils<br />

16 Bit über die Schnittstelle. Im Sendefall<br />

werden diese 16 Daten über TXD mit<br />

Hilfe der BURST-Steuerleitung in den<br />

Sendepuffer des Modems eingeschrieben.<br />

Es folgen das Auslesen im Modem-Sendetakt<br />

und das Filtern mit dem in einem<br />

EPROM kodierten digitalen FIR-Filter.<br />

Ein nachfolgendes Analogfilter beseitigt<br />

störende Abtastsignale des digitalen Fil-<br />

186 • FA 2/95<br />

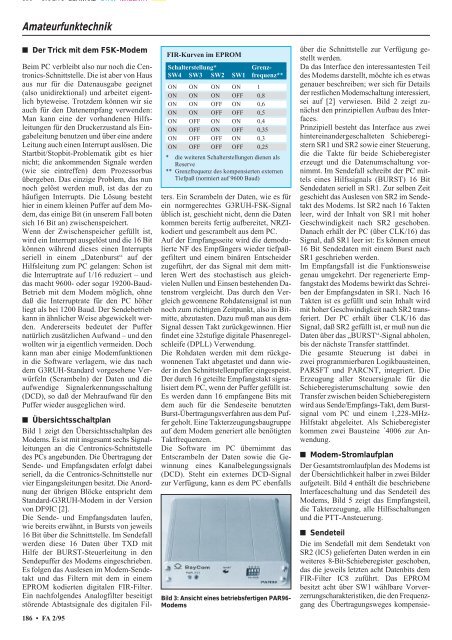

FIR-Kurven im EPROM<br />

Schalterstellung* Grenz-<br />

SW4 SW3 SW2 SW1 frequenz**<br />

ON ON ON ON 1<br />

ON ON ON OFF 0,8<br />

ON ON OFF ON 0,6<br />

ON ON OFF OFF 0,5<br />

ON OFF ON ON 0,4<br />

ON OFF ON OFF 0,35<br />

ON OFF OFF ON 0,3<br />

ON OFF OFF OFF 0,25<br />

* die weiteren Schalterstellungen dienen als<br />

Reserve<br />

** Grenzfrequenz des kompensierten externen<br />

Tiefpaß (normiert auf 9600 Baud)<br />

ters. Ein Scrambeln der Daten, wie es <strong>für</strong><br />

ein normgerechtes G3RUH-FSK-Signal<br />

üblich ist, geschieht nicht, denn die Daten<br />

kommen bereits fertig aufbereitet, NRZIkodiert<br />

und gescrambelt aus dem PC.<br />

Auf der Empfangsseite wird die demodulierte<br />

NF des Empfängers wieder tiefpaßgefiltert<br />

und einem binären Entscheider<br />

zugeführt, der das Signal mit dem mittleren<br />

Wert des stochastisch aus gleichvielen<br />

Nullen und Einsen bestehenden Datenstrom<br />

vergleicht. <strong>Das</strong> durch den Vergleich<br />

gewonnene Rohdatensignal ist nun<br />

noch zum richtigen Zeitpunkt, also in Bitmitte,<br />

abzutasten. Dazu muß man aus dem<br />

Signal dessen Takt zurückgewinnen. Hier<br />

findet eine 32stufige digitale Phasenregelschleife<br />

(DPLL) Verwendung.<br />

Die Rohdaten werden mit dem rückgewonnenen<br />

Takt abgetastet und dann wieder<br />

in den Schnittstellenpuffer eingespeist.<br />

Der durch 16 geteilte Empfangstakt signalisiert<br />

dem PC, wenn der Puffer gefüllt ist.<br />

Es werden dann 16 empfangene Bits mit<br />

dem auch <strong>für</strong> die Sendeseite benutzten<br />

Burst-Übertragungsverfahren aus dem Puffer<br />

geholt. Eine Takterzeugungsbaugruppe<br />

auf dem Modem generiert alle benötigten<br />

Taktfrequenzen.<br />

Die Software im PC übernimmt das<br />

Entscrambeln der Daten sowie die Gewinnung<br />

eines Kanalbelegungssignals<br />

(DCD). Steht ein externes DCD-Signal<br />

zur Verfügung, kann es dem PC ebenfalls<br />

Bild 3: Ansicht eines betriebsfertigen PAR96-<br />

Modems<br />

über die Schnittstelle zur Verfügung gestellt<br />

werden.<br />

Da das Interface den interessantesten Teil<br />

des Modems darstellt, möchte ich es etwas<br />

genauer beschreiben; wer sich <strong>für</strong> Details<br />

der restlichen Modemschaltung interessiert,<br />

sei auf [2] verwiesen. Bild 2 zeigt zunächst<br />

den prinzipiellen Aufbau des Interfaces.<br />

Prinzipiell besteht das Interface aus zwei<br />

hintereinandergeschalteten Schieberegistern<br />

SR1 und SR2 sowie einer Steuerung,<br />

die die Takte <strong>für</strong> beide Schieberegister<br />

erzeugt und die Datenumschaltung vornimmt.<br />

Im Sendefall schreibt der PC mittels<br />

eines Hilfssignals (BURST) 16 Bit<br />

Sendedaten seriell in SR1. Zur selben Zeit<br />

geschieht das Auslesen von SR2 im Sendetakt<br />

des Modems. Ist SR2 nach 16 Takten<br />

leer, wird der Inhalt von SR1 mit hoher<br />

Geschwindigkeit nach SR2 geschoben.<br />

Danach erhält der PC (über CLK/16) das<br />

Signal, daß SR1 leer ist: Es können erneut<br />

16 Bit Sendedaten mit einem Burst nach<br />

SR1 geschrieben werden.<br />

Im Empfangsfall ist die <strong>Funk</strong>tionsweise<br />

genau umgekehrt. Der regenerierte Empfangstakt<br />

des Modems bewirkt das Schreiben<br />

der Empfangsdaten in SR1. Nach 16<br />

Takten ist es gefüllt und sein Inhalt wird<br />

mit hoher Geschwindigkeit nach SR2 transferiert.<br />

Der PC erhält über CLK/16 das<br />

Signal, daß SR2 gefüllt ist, er muß nun die<br />

Daten über das „BURST“-Signal abholen,<br />

bis der nächste Transfer stattfindet.<br />

Die gesamte Steuerung ist dabei in<br />

zwei programmierbaren Logikbausteinen,<br />

PARSFT und PARCNT, integriert. Die<br />

Erzeugung aller Steuersignale <strong>für</strong> die<br />

Schieberegisterumschaltung sowie den<br />

Transfer zwischen beiden Schieberegistern<br />

wird aus Sende/Empfangs-Takt, dem Burstsignal<br />

vom PC und einem 1,228-MHz-<br />

Hilfstakt abgeleitet. Als Schieberegister<br />

kommen zwei Bausteine ´4006 zur Anwendung.<br />

■ Modem-Stromlaufplan<br />

Der Gesamtstromlaufplan des Modems ist<br />

der Übersichtlichkeit halber in zwei Bilder<br />

aufgeteilt. Bild 4 enthält die beschriebene<br />

Interfaceschaltung und das Sendeteil des<br />

Modems, Bild 5 zeigt das Empfangsteil,<br />

die Takterzeugung, alle Hilfsschaltungen<br />

und die PTT-Ansteuerung.<br />

■ Sendeteil<br />

Die im Sendefall mit dem Sendetakt von<br />

SR2 (IC5) gelieferten Daten werden in ein<br />

weiteres 8-Bit-Schieberegister geschoben,<br />

das die jeweils letzten acht Datenbits dem<br />

FIR-Filter IC8 zuführt. <strong>Das</strong> EPROM<br />

besitzt acht über SW1 wählbare Vorverzerrungscharakteristiken,<br />

die den Frequenzgang<br />

des Übertragungsweges kompensie-