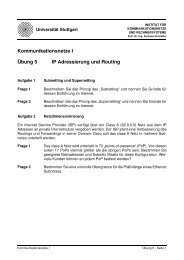

Übung 3 - Institut für Kommunikationsnetze und Rechnersysteme ...

Übung 3 - Institut für Kommunikationsnetze und Rechnersysteme ...

Übung 3 - Institut für Kommunikationsnetze und Rechnersysteme ...

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Aufgabe 1<br />

Erste Schritte<br />

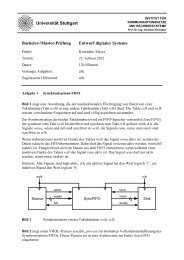

Im Folgenden soll zunächst die vorgegebene Fassung der Testbench mit dem korrekt funktionierenden<br />

Speicher simuliert werden. In den folgenden Aufgabenteilen werden Sie die Testbench<br />

dann schrittweise erweitern.<br />

Öffnen Sie das ModelSim-Projekt ex3.mpf <strong>und</strong> compilieren Sie dieses anschließend:<br />

• Entpacken Sie das Archiv eds-ex3-files.zip<br />

• Starten Sie ModelSim<br />

• File >> Open >> Files of Type: Project Files (*.mpf) >> ex3.mpf auswählen >> Open<br />

• Compile >> Compile Order >> Auto Generate<br />

Simulieren Sie die nun die Architecture struct von memory_tb. Vergewissern Sie sich, dass<br />

sich Tester <strong>und</strong> Speicher wie zuvor beschrieben verhalten.<br />

Wählen Sie dazu im Workspace-Fenster den Tab Library aus <strong>und</strong> klicken Sie mit der rechten<br />

Maustaste auf den Eintrag work >> memory_tb >> struct. Wählen Sie im erscheinenden Kontext-Menü<br />

den Punkt Simulate aus. Fügen Sie die Testbench-Signale einem Wave-Window<br />

hinzu <strong>und</strong> simulieren Sie eine Zeitspanne von 10µs.<br />

Im Folgenden soll der Tester erweitert werden.<br />

Frage 1<br />

Frage 2<br />

Frage 3<br />

Ändern Sie den Prozess tester_p in memory_tester(behav) so ab, dass er zunächst<br />

alle Speicherzellen nacheinander einmal mit beliebigen Werten beschreibt<br />

<strong>und</strong> die Speicherzellen dann nacheinander wieder ausliest.<br />

Überprüfen Sie die korrekte Funktion im Wave-Window.<br />

Hinweis: Benutzen Sie Funktionen aus dem Package ieee.numeric_std.<br />

Erweitern Sie den Tester so, dass er im Fehlerfall eine Meldung ausgibt<br />

(Adresse, gelesener Wert, erwarteter Wert). Benutzen Sie dazu eine assertoder<br />

report-Anweisung.<br />

Hinweis:<br />

Auf Gr<strong>und</strong> der Simulationsmethodik von VHDL ändert sich der Ausgang<br />

rdata des Speichers erst nach einem (infinitesimal) kleinen Zeitraum nachdem<br />

seine Eingangssignale gesetzt wurden. In der Testbench müssen Sie daher<br />

ein wait-statement zwischen dem Setzen von wena/address/wdata <strong>und</strong><br />

dem Lesen von rdata einfügen. Beispielsweise könnten Sie bis zur nächsten<br />

negativen Taktflanke warten.<br />

Simulieren Sie nun memory_tb(struct_faulty).<br />

An welchen Adressen meldet Ihr Tester Fehler? Stellen Sie eine Vermutung<br />

an, wie ein solches Fehlermuster zustande kommen kann.<br />

Entwurf digitaler Systeme <strong>Übung</strong> 3: Testbench-Modellierung <strong>und</strong> Fehleranalyse - Bl. 3