Vorlesung Rechnerarchitektur - Fachbereich Informatik

Vorlesung Rechnerarchitektur - Fachbereich Informatik

Vorlesung Rechnerarchitektur - Fachbereich Informatik

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

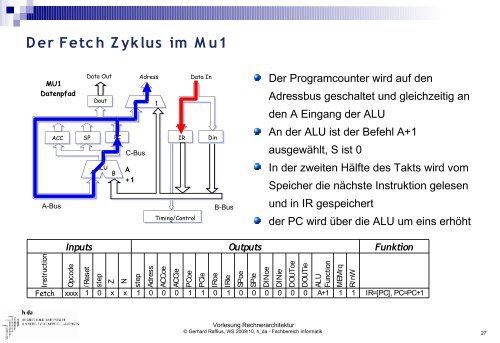

D er Fetc h Z yklus im M u1<br />

MU1<br />

Datenpfad<br />

ACC<br />

A<br />

A-Bus<br />

Data Out<br />

SP<br />

SP<br />

Dout<br />

Dout<br />

ALU<br />

A ALUB<br />

PC<br />

PC<br />

Adress<br />

0 1<br />

C-Bus<br />

A<br />

+1<br />

IR IR<br />

Timing/Control<br />

Data In<br />

Din Din<br />

B-Bus<br />

Der Programcounter wird auf den<br />

Adressbus geschaltet und gleichzeitig an<br />

den A Eingang der ALU<br />

An der ALU ist der Befehl A+1<br />

ausgewählt, S ist 0<br />

In der zweiten Hälfte des Takts wird vom<br />

Speicher die nächste Instruktion gelesen<br />

und in IR gespeichert<br />

der PC wird über die ALU um eins erhöht<br />

Instruction<br />

Fetch<br />

Inputs Outputs Funktion<br />

Opcode<br />

xxxx<br />

/Reset<br />

step<br />

Z<br />

N<br />

step<br />

Adress<br />

ACCoe<br />

ACCie<br />

PCoe<br />

PCie<br />

IRoe<br />

IRie<br />

SPoe<br />

SPie<br />

1 0 x x 1 0 0 0 1 1 0 1 0 0 0 0 0 0 A+1 1 1 IR=[PC], PC=PC+1<br />

DINoe<br />

DINie<br />

DOUToe<br />

DOUTie<br />

ALU<br />

Function<br />

MEMrq<br />

R/nW<br />

<strong>Vorlesung</strong> <strong>Rechnerarchitektur</strong><br />

© Gerhard Raffius, WS 2009/10, h_da - <strong>Fachbereich</strong> <strong>Informatik</strong><br />

27