VHDL-Grundlagen - Technische Informatik an der Universität Frankfurt

VHDL-Grundlagen - Technische Informatik an der Universität Frankfurt

VHDL-Grundlagen - Technische Informatik an der Universität Frankfurt

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

KAPITEL 2. GRUNDLAGEN 5<br />

bestückenden IC-Gehäusetyp dar, <strong>der</strong> durch die Anzahl, die Eigenschaften und die Bezeichnung<br />

<strong>der</strong> Anschlüsse definiert ist. Die Deklaration <strong>der</strong> Anschlüsse innerhalb <strong>der</strong> Entity erfolgt<br />

mit Hilfe <strong>der</strong> Port-Anweisung. Dabei beschreibt jedes Element <strong>der</strong> Port-Anweisung einen<br />

o<strong>der</strong> mehrere Anschlüsse.<br />

Entity-Syntax<br />

entity is<br />

port ();<br />

end ;<br />

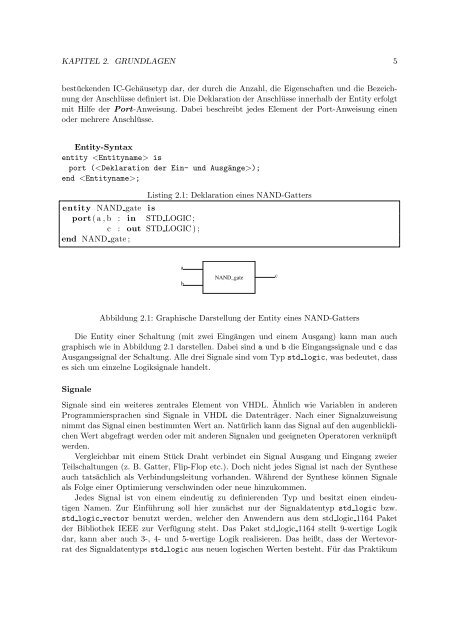

entity NAND gate i s<br />

port ( a , b : in STD LOGIC ;<br />

c : out STD LOGIC ) ;<br />

end NAND gate ;<br />

Listing 2.1: Deklaration eines NAND-Gatters<br />

a<br />

b<br />

NAND_gate<br />

c<br />

Abbildung 2.1: Graphische Darstellung <strong>der</strong> Entity eines NAND-Gatters<br />

Die Entity einer Schaltung (mit zwei Eingängen und einem Ausg<strong>an</strong>g) k<strong>an</strong>n m<strong>an</strong> auch<br />

graphisch wie in Abbildung 2.1 darstellen. Dabei sind a und b die Eing<strong>an</strong>gssignale und c das<br />

Ausg<strong>an</strong>gssignal <strong>der</strong> Schaltung. Alle drei Signale sind vom Typ std logic, was bedeutet, dass<br />

es sich um einzelne Logiksignale h<strong>an</strong>delt.<br />

Signale<br />

Signale sind ein weiteres zentrales Element von <strong>VHDL</strong>. Ähnlich wie Variablen in <strong>an</strong><strong>der</strong>en<br />

Programmiersprachen sind Signale in <strong>VHDL</strong> die Datenträger. Nach einer Signalzuweisung<br />

nimmt das Signal einen bestimmten Wert <strong>an</strong>. Natürlich k<strong>an</strong>n das Signal auf den augenblicklichen<br />

Wert abgefragt werden o<strong>der</strong> mit <strong>an</strong><strong>der</strong>en Signalen und geeigneten Operatoren verknüpft<br />

werden.<br />

Vergleichbar mit einem Stück Draht verbindet ein Signal Ausg<strong>an</strong>g und Eing<strong>an</strong>g zweier<br />

Teilschaltungen (z. B. Gatter, Flip-Flop etc.). Doch nicht jedes Signal ist nach <strong>der</strong> Synthese<br />

auch tatsächlich als Verbindungsleitung vorh<strong>an</strong>den. Während <strong>der</strong> Synthese können Signale<br />

als Folge einer Optimierung verschwinden o<strong>der</strong> neue hinzukommen.<br />

Jedes Signal ist von einem eindeutig zu definierenden Typ und besitzt einen eindeutigen<br />

Namen. Zur Einführung soll hier zunächst nur <strong>der</strong> Signaldatentyp std logic bzw.<br />

std logic vector benutzt werden, welcher den Anwen<strong>der</strong>n aus dem std logic 1164 Paket<br />

<strong>der</strong> Bibliothek IEEE zur Verfügung steht. Das Paket std logic 1164 stellt 9-wertige Logik<br />

dar, k<strong>an</strong>n aber auch 3-, 4- und 5-wertige Logik realisieren. Das heißt, dass <strong>der</strong> Wertevorrat<br />

des Signaldatentyps std logic aus neuen logischen Werten besteht. Für das Praktikum