ELA5-FET.PDF (1.4MB)

ELA5-FET.PDF (1.4MB)

ELA5-FET.PDF (1.4MB)

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

HTI Burgdorf 5-1Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5 Feldeffekt-TransistorenFeldeffekttransistoren (<strong>FET</strong>) sind Unipolartransistoren. Die Steuerung und der Stromfluss erfolgt nurmit Majoritätsträgern. Die Leitfähigkeit im Transistor wird durch ein elektrisches Feld gesteuert. Esbeeinflusst den Querschnitt des Leitungskanals oder die Leitfähigkeit des Halbleitermaterials. Beidessind grundsätzliche verschiedene Wirkungsmechanismen.Die Entwicklung des <strong>FET</strong> geht auf Patente von O. Heil und J. Lilienthal in den Jahren 1928-1939zurück. Mit der damals zur Verfügung stehenden Technologie konnten die <strong>FET</strong>s aber nicht realisiertwerden.<strong>FET</strong> sind spannungsgesteuerte Elemente und sind daher im Prinzip leistungslos steuerbar.Kennzeichnend für alle <strong>FET</strong> ist der sehr hohe Eingangswiderstand im Bereich 10MΩ bis GΩ. DieBasismaterialien sind vorwiegend Si und GaAs, jedoch auch Ge und SiC.Man unterscheidet je nach Technologie folgende <strong>FET</strong>:<strong>FET</strong>J<strong>FET</strong>IG<strong>FET</strong> (MOS<strong>FET</strong>)PN-<strong>FET</strong>MES<strong>FET</strong>N-KanalP-KanalN-KanalVerarmungstypP-KanalVerarmungstypAnreicherungstypBild 5-1: Übersicht über die verschiedenen Arten vonFeldeffekt-Transistoren.Die Aufzählung der Technologien ist nicht vollständig, zeigtaber die meist verwendeten Arten.J<strong>FET</strong>:Junction-<strong>FET</strong> oder auch PN-<strong>FET</strong> genannt. Das Gate wird durch in Sperrrichtung betriebene Gatediodedargestellt. Je nach Technologie des Gate unterscheidet man zwischen einem PN-Übergang (PN-<strong>FET</strong>)oder einem Metall-Halbleiter-Kontakt (MES<strong>FET</strong>). Anreicherungstypen sind mit den klassischenHalbleitermaterialien nicht möglich. Neuerdings sind auf der Basis SiC J<strong>FET</strong>-Anreicherungstypen alsLabormuster erhältlich.IG<strong>FET</strong>:Sie werden auch Isolated Gate <strong>FET</strong> oder MOS<strong>FET</strong> (Metal Oxide Semiconductor <strong>FET</strong>) genannt. DasGate wird durch eine sehr dünne Isolationsschicht vom Kanal isoliert. IG<strong>FET</strong> werden sowohl fürKleinsignalanwendungen wie auch für Leistungsstufen verwendet.Als Basismaterial wird hauptsächlich Silizium verwendet. Germanium wurde in der Anfangszeit auchverwendet. Wegen der schlechten Reststromeigenschaften wurde es aber vollständig durch Siliziumabgelöst. Für Hochfrequenzanwendungen werden oft MES<strong>FET</strong> in Gallium-Arsenid Technologieverwendet. Anfänglich war der Herstellungsprozess problematisch und sehr teuer. Mittlerweile sindaber GaAs-<strong>FET</strong> nicht viel teurer als Si-<strong>FET</strong>.Als Spezialfall sind die sog. IGBT (Isolated Gate Bipolar Transistor) zu sehen. Sie verkörpern eineKombination von IG<strong>FET</strong> und Bipolartransistor. Sie werden vor allem als Schalterelemente in derLeistungselektronik verwendet. Sie vereinen einige der Vorteile beider Transistortechnologien.<strong>FET</strong> werden praktisch in allen Bereichen eingesetzt, die auch Bipolartransistoren abdecken können:Verstärker, Konstantstromquellen und Schalter. Trotzdem sind <strong>FET</strong> nicht als Ersatz fürBipolartransistoren anzusehen.Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-2Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.1 Junction-<strong>FET</strong> (J<strong>FET</strong>)J<strong>FET</strong> werden als Verstärker, Konstantstromquellen, elektrisch steuerbare Widerstände oder Schaltereingesetzt. Sie werden vor allem für Kleinsignalanwendungen eingesetzt. Der Einsatzbereich erstrecktsich von Gleichstromanwendungen bis in den GHz-Bereich.Wegen des hohen Eingangswiderstandes werden J<strong>FET</strong> dort eingesetzt, wo schaltungsmässig ein grosserEingangswiderstand erwünscht ist. Ferner haben sie unter bestimmten Betriebsbedingungen eingünstigeres Rauschverhalten.5.1.1 Aufbau und SchaltplansymboleJe nach Dotierung des Kanals wird zwischen N-Kanal- oder P-Kanal <strong>FET</strong> unterschieden, wobei jedochder grösste Teil die Silizium J<strong>FET</strong> N-Kanal Typen sind. Vom Prinzip her kann der Aufbau eines J<strong>FET</strong>nach Bild 5 gezeigt werden:KanalGateDrainN-SiliziumP-SiliziumSourceN-Kanal <strong>FET</strong>+-0P-Kanal <strong>FET</strong>-+0Notation der Spannungenund StrömeU DGGU GSI DDSI SU DSBild 5-2: Vereinfachter Aufbau eines N-Kanal J<strong>FET</strong>,Schaltplansymbole, und Notationen.Die Polaritäten beziehen sich auf den Betrieb als Verstärker,bezogen auf den Sourceanschluss.Der Übergang in Bild 5 zwischen dem P-dotierten Ring und dem N-dotierten Kanal bildet eineSperrschicht, die Gatediode. Beim Betrieb des <strong>FET</strong> ist diese Diode immer gesperrt. Es fliesst lediglichein sehr kleiner Sperrstrom in der Grössenordnung pA bis nA.Im Gegensatz zu den Bipolartransistoren sind J<strong>FET</strong>s in der Regel symmetrisch aufbaut. Das heisst, dieAnschlüsse Drain und Source können vertauscht werden.5.1.2 ArbeitsweiseWird bei einem <strong>FET</strong> Gate und Source verbunden (U GS=0V, Bild 5 a.) fliesst der maximal möglicheKanalstrom I DSS. Typische Werte liegen bei Kleinsignal-<strong>FET</strong>s im Bereich von mA bis einige 10mA.Wird bei einem N-Kanal <strong>FET</strong> eine negative Spannung am Gate bezüglich Source angelegt, wächst dieladungsträgerfreie Zone in den Kanal hinein (Bild 5 b.). Der Leitungskanal wird durch das Wachsender Verarmungszone verkleinert und der Stromfluss nimmt ab. Der Kanalwiderstand wird somit überdie Gatespannung steuerbar. Beim P-Kanal <strong>FET</strong> wird dies mit einem positiven U GSerreicht.a.) V CCb.) V CCc.)GDSI DSSGDU GSSI DVerarmungszoneGDV CCU GS=U PSI D≈0Bild 5-3:Kanalform für den Stromfluss im J<strong>FET</strong>bei verschiedenen Gatespannungen U GS.Beim Erreichen der sog. Abschnürspannung U P(Pinch Off Voltage) wird der Kanal gänzlich gesperrtund es fliesst praktisch kein Drainstrom I D. (Bild 5 c.) mehr. Für die Praxis definieren die Hersteller dieSpannung U Pals Spannungswert, bei dem der Drainstrom auf einen bestimmten Wert abgesunken ist,z.B. 1uA.Das Zuwachsen des Kanals erfolgt wegen den unterschiedlichen Potenzialen nicht symmetrisch. DerKanal nimmt für ein wachsendes U GSimmer mehr eine Keilform an.Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-3Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.1.3 KennlinienFür die Kleinsignaldimensionierung im niederen Frequenzbereich können alle benötigten Grössen ausI DSSund U Pbestimmt werden. Das Grosssignalverhalten wird meist mit Kennlinien beschrieben. Hierzugehören die Übertragungskennlinie I D(U GS) und die Ausgangskennlinie I D(U DS).Die Übertragungskennlinie zeigt näherungsweise ein quadratisches Verhalten. HerauszuhebendePunkte sind der Sättigungsstrom I DSSbei U GS=0V und die Abschnürspannung U Pwo I D≈0A wird.I D [mA]I DSS7I D [mA]Ohmscher BereichU GS =0V⎛ U ⎞GSID= IDSS⎜1−⎟⎝ UP ⎠265AbschnürbereichU GS =-1V43U GS =-2V2U GS =-3V[V] U GS-8U P-6-4-21U GS =-4V5 10 15 20 25U PU DS [V]Bild 5-2:Typischer Verlauf derÜbertragungs- und Ausgangskennlinienbeim J<strong>FET</strong>, hier ein N-Kanal-Typ.Im I D(U GS) -Kennlinienfeld unterscheidet man den ohmschen Bereich und den Abschnürbereich. Imohmschen Bereich verhält sich der <strong>FET</strong> wie ein elektrisch steuerbarer Widerstand. Im Abschnürbereichwird der <strong>FET</strong> als spannungsgesteuerte Stromquelle für den Einsatz als Verstärker betrieben.Der näherungsweise quadratische Verlauf ist vom Verlauf der Dotierung abhängig. Formal gilt:IIDD2⎛ U ⎞GS= IDSS⎜1−⎟Spikesförmig dotierter Kanal⎝ UP ⎠3⎡⎤⎛U⎞ ⎛ 2GSU ⎞GS= I ⎢DSS1− 3 + 2 ⎥ Gleichmässig dotierter Kanal⎢ ⎜ ⎟ ⎜ ⎟⎝ UP⎠ ⎝ U ⎥P⎢⎠⎣⎥⎦(5.1)(5.2)Beide Gleichungen unterscheiden sich in der Auswertung nur geringfügig. Trotz der Einfachheit derGleichung (5.1) stellt sie eine brauchbare Näherung für beliebige <strong>FET</strong> dar. Die Herleitung derGleichungen sind in [TEX77], Kap.1 gezeigt.Die Eingangskennlinie I G(U GS) ist weniger von Interesse. Die Gatediode sperrt bei Si-<strong>FET</strong> nach[TEX77, S.90] bis zum Erreichen einer maximalen Sperrspannung in der Grössenordnung von 25V-30Vbei U GS=0V. Bei höherer Spannung erfolgt ein Avalanche-Durchbruch. Wird U GSbeim N-Kanal <strong>FET</strong>positiv, fliesst ein Gatestrom. Die Gatediode ist vom Verhalten her eine Si-Diode mit gutenSperreigenschaften.Durch einfache Umstellung von (5.1) findet man U GS(I D,I DSS):UGS⎛= UP⎜−⎝II1DDSS⎞⎟⎠(5.3)Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-4Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenDie „Verstärkung“ des <strong>FET</strong> wird mit der Steilheit y21y21S=2 ID ⋅ IDSSUPSdID= gm= beschrieben:dUGS(5.4)Alle <strong>FET</strong> haben daher bei I D=I DSSdie grösste Steilheit. Dies lässt sich aus (5.4) bestimmen oder direktaus dem Verlauf der I D/U GS-Kennlinie: Die Steigung der Parabel steigt streng monoton. EineStromverstärkung kann beim <strong>FET</strong> wegen I G=0 nicht formuliert werden.Die Begründung der Gleichung (5.4) wird aus (5.1) entwickelt:22⎛ U ⎞ ⎛ ⎞GSUGS UGSD=DSS ⎜1− ⎟ =DSS ⎜1− 2 +2 ⎟UP UP UPI I I⎝ ⎠ ⎝ ⎠ydI ⎛ −22U ⎞ −2I ⎛ U ⎞= = I ⎜ + ⎟= ⎜1−⎟⎝ ⎠ ⎝ ⎠DGS DSS GS21SDSS2dUGS UPUPUPUP(5.5)Mit Einsetzen von Gl. (5.3) erhalten wir:⎛ ⎛ I ⎞⎞⎛DI ⎞2 1D⎜ UP ⎜ − ⎟⎟ ⎜−2⎟⎜ −2IDSS⎟IDSSy21S = I⎝ ⎠DSSI ⎜ ⎟⎜+2DSSUP U ⎟=⎜PU ⎟P⎜⎜⎟⎟⎝⎠ ⎝ ⎠(5.6)5.1.4 TemperatureinflüsseBeim J<strong>FET</strong> ist die Temperaturabhängigkeit des Kanalstromes I Dhauptsächlich durch dieDiffusionsspannung und der Beweglichkeit der Ladungsträger bestimmt. Die Beweglichkeit nimmtnach [TOB, S.61] um etwa 0.7% pro Grad ab. In Folge nimmt der Drainstrom bei zunehmenderTemperatur ab. Die Diffusionsspannung hat einen negativen Temperaturkoeffizienten. Deshalb nimmtdie Abschnürspannung U P(betragsmässig) um etwa 2mV pro Grad Temperaturanstieg zu. Einthermisches Hochlaufen ist, anders als bei den Bipolartransistoren, nicht möglich.50°C25°C100°C-U GSI DI DZBild 5-3:: Typischer Verlauf des Drainstromesbei verschiedenen Temperaturen.U GSZAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-5Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenAlle Kurven in Bild 5-3 schneiden sich im Punkt (U GSZ, I DZ). In diesem Schnittpunkt wird derTemperaturkoeffizient des Kanalstromes I Dnahezu null und der <strong>FET</strong> arbeitet temperaturstabil. DieserPunkt wird ungefähr erreicht bei2 2⎛0.63V⎞ 0.4VIIDZ≈ IDSS⎜⎟≈⎝ UP⎠ UPU ≈U −0.63VGSZPDSS(5.7)(5.8)Bei MOS<strong>FET</strong> ist das Temperaturverhalten ähnlich.Begründung der Formeln (5.7), (5.8)Die Drift der Diffusionsspannung U Diffbeträgt bei Zimmertemperatur ca. -2.2mV pro ºC und die Driftder Mobilität µ der Ladungsträger ca. 0.7% pro ºC. Mit diesen Werten kann nach [GRA71, S.61] dieTemperaturabhängigkeit der Spannung U GSbeschrieben werden:dU dU I IdT dT dT y C C yGS=Diff dµ D −3 V−31+ =−2.2⋅ 10 + 7⋅10D21S21S(5.9)dU GSFür den Fall der Temperaturunabhängigkeit setzt mandT= 0 und erhält:−3 V −312.2⋅10 ⋅21= 7⋅10⋅ ySZ IDZCCIDZy= 0.315V21SZ(5.10)Setzt man für I Dund I DSSdie Gleichungen (5.1) und (5.5) ein, erhält man:⎛ U ⎞GSZ UGSZIDSS ⎜1−⎟ 1−I0.315⎝ UDZ⎠ UPU −UV = = = =y 221SZ I ⎛ ⎞2DSSUGSZ2 ⎜1−⎟UP⎝ UP⎠UPU = U −2⋅ 0.315V = U −0.63VGSZ P P2P P GSZ(5.11)Das erhaltene U GSZliegt in der Praxis beim N-Kanal <strong>FET</strong> in der Grössenordnung von -1.5 ..-3.5V2IDZ IDZ IDZUP= 0.315V= =y 2I⎛ U ⎞ 2I U − 2I U⎜1−⎟UP⎝ UP⎠21SZ DSS GSZ DSS P DSS GSZ2IDZUP0.315V=2I U − 2I UDSS P DSS GSZ2⋅0.315V ⋅I U −2⋅0.315V ⋅ I U = I U2DSS P DSS GSZ DZ P0.63V ⋅I U −0.63 V ⋅I ( U − 0.63 V)= I U2DSS P DSS P DZ P0.63V ⋅ I U −0.63V ⋅IDSSUPDSSP0.3969V22 2DSS+ 0.3969V IDSS = IDZUP → IDZ=2UP⋅ I(5.12)Das erhaltene I DZliegt in der Praxis beim N-Kanal <strong>FET</strong> in der Grössenordnung von 200uA..600uA.Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-6Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenFür den Punkt (U GSZ, I GSZ) lässt sich ferner auch die Steilheit bestimmen y 21SZ:y1.2649V ⋅ IDSS=21SZ2UP(5.13)Die Steilheit für den temperaturunabhängigen Arbeitspunkt liegt in der Praxis im Bereich bei600uS..2mS.Begründung der Formel (5.13):Wir verwenden (5.4) und setzen für I Ddie Gleichung für I DZnach (5.7) ein und vereinfachen denAusdruck:y0.4V ⋅ I 0.4V I2 2 2DSS⋅DSS2 ⋅ I 22 22=DSSI ⋅IDIDZDIDSS UP UP 2V ⋅ 0.4 ⋅IDSS 1.2649V ⋅IDSS21S= = = = =2 2UP UP UP UPUP5.1.5 BegriffeI DSSDrainstrom, wenn U GS=0V. Dies ist der maximal zulässige Drainstrom. Dieser Wert ist hauptsächlichvon der Kanaldicke und der Kanaldotierung abhängig.U PPinch-Off-Spannung (Abschnürspannung). Dies ist diejenige Gatespannung U GS, die notwendig ist, umden Drainstrom I Dauf einen bestimmten Wert zu vermindern (z.B. I D=1uA bei U D=10V). Dieser Wertist herstellerspezifisch definiert. U Pist hauptsächlich von der Kanallänge und Kanaldotierung abhängig.y 21SKleinsignal Vorwärtssteilheit in A/V.AbschnürbereichLiegt der Arbeitspunkt im Abschnürbereich, wird der <strong>FET</strong> als Verstärker betrieben. Er arbeitet alsspannungsgesteuerte Stromquelle mit einem grossen r DS, erkennbar an den fast waagrechten Kurven fürI Dbei grösseren U DS. Der Abschnürbereich beginnt allgemein bei -U P+U GS.Ohmscher BereichFür kleine U DSverhält sich der <strong>FET</strong> wie ein elektrisch steuerbarer Widerstand. Dieses Verhalten wirdausgenutzt, um z.B. elektrisch steuerbare Spannungsteiler zu realisieren.U DSmaxMaximale Drain-Sourcespannung. Diese ist von der Dotierung abhängig und liegt in derGrössenordnung von etwa 30V.Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-7Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.1.6 ErsatzschaltbilderDas Ersatzschaltbild modelliert den <strong>FET</strong> als nicht ideale spannungsgesteuerte Stromquelle mitparasitären Widerständen und Kapazitäten. Für den Kleinsignalbetrieb bei niedrigen Frequenzen (bisca. 30MHz) definiert man das Ersatzschaltbild:C DGDy DGr DBGg m·U GSy DSy SGC SGr SBSBild 5-4: Ersatzschaltbild des J<strong>FET</strong> für niedrigeFrequenzen nach [TEX77].Die Bahnwiderstände r SB, r DBsind abhängig vom Herstellungsprozess und der Geometrie. Sie liegen inder Grössenordnung < 100Ω. Die Leitwerte y SG, y DG, wie auch die Kapazitäten C SG, C DGsind sehr kleinund können für tiefe Frequenzen in den meisten Fällen vernachlässigt werden.Aus dem Modell nach Bild 5-4 kann ein vereinfachtes Vierpolmodell mit Y-Parameter gemäss Bild 5-5definiert werden. Für den Einsatz im DC- oder NF-Bereich ist es hinreichend.GDI 1=0 I 2Bild 5-5:Vereinfachtes Vierpol-Ersatzschaltbild.U 1 y 21S·U 1y 22S U 2SS5.1.7 Ohmscher BereichIm ohmschen Bereich arbeitet der <strong>FET</strong> als elektrisch steuerbarer Widerstand r DS Ω. Dieser Bereich wirdauch „Triodenbereich“ genannt, weil der Kennlinienverlauf einer Triodenröhre ähnelt.Im I D(U GS) Kennlinienfeld verkörpert der ohmsche Bereich, wo bei kleinen U DSdie I Dsteil ansteigen.Für kleine U DSkönnen daher ohne grossen Fehler die Kennlinien linearisiert werden. Der Widerstandergibt sich aus den Steigungen ∆U D/∆I Dwie in Bild 5-6 gezeigt.I DOhmscher BereichU GS=Param.U DSU PLinearisierte DarstellungI DU GS=Param.∆I D∆U DSU DSrDSΩ∆U= ∆ IDSDBild 5-6:Ohmscher Bereich des <strong>FET</strong>.Der Widerstandsverlauf r DS Ω(U GS) ist nichtlinear von der Steuerspannung U GSabhängig.rDSΩ−UP=⎛ U2IDSS ⎜1−⎝ UGSP⎞⎟⎠(5.14)Elektrisch steuerbare Spannungsteiler für kleinere Spannungen werden oft mit <strong>FET</strong> realisiert.Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-8Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenBeispiel 5-1: Elektrisch steuerbarer Widerstand.In welchem Bereich variiert der ohmsche Widerstand für kleine U DSwenn der <strong>FET</strong> folgende Datenaufweist: U P=-3.1V, I DSS=2.4mA.Lösung: Aufzeichnen des Graphen r DS Ω(U GS) mit (5.14).Vorgaben:U P := −3.1VI DSS := 2.4mABerechnungen:−U Pr DSΩ ( U GS ) := UGS:=linrange( 0, −3,100)⎛ U GS ⎞2⋅ I DSS ⋅ ⎜ 1 −⎝ U P ⎠2 . 10 41.5 .10 4r DSΩ ( UGS)1 .10 4500003 2.5 2 1.5 1 0.5 0UGSBild 5-7:Widerstandsverlauf des Ohmschen Bereichdes <strong>FET</strong> nach Beispiel 5-1Man erkennt den näherungsweise linearen Verlauf für U GSbis etwa U P/3. Dann steigt der Widerstandnicht linear an, bis bei U Ptheoretisch unendlich gross wird.Begründung der Formel (5.14):Nach [HOE85, S.121] gelten für den J<strong>FET</strong> die SPICE-Modellgleichungen :( ( ) )I = β ⋅U 2 U −U −UWiderstandsbereichD DS GS TO DS( ) 2I = β U −UD GS TOAbschnürbereich(5.15)(5.16)Mit U P=U TOund Gleichsetzen von (5.16) mit (5.1) kann der Parameter β bestimmt werden:2 22 22 β ⎛U⎞DSβ ⎛ U ⎞GSID = β ( UGS − UP)= 1 12 ⎜ − ⎟ =2 ⎜ − ⎟UP ⎝ UP ⎠ UP ⎝ UP⎠ID⎛ U ⎞ β ⎛ U ⎞I= IDSS⎜1− ⎟ = ⎜1− ⎟→ β =⎝ U ⎠ U ⎝ U ⎠ UPGS GS DSS2 2P P P(5.17)Das Resultat wird nun in (5.15) eingesetzt und der Widerstand r DS Ω bestimmt. Wir unterstellen für dieseBetrachtung Linearität. Das quadratische Glied wird nicht berücksichtigt und wir erhalten:I I I II U U U U U U U U UrDSS DSS DSS DSS 2 DSS= ( 2( − ) − ) = 2 −2− = 2 UDS ( UGS −UP)D 2 DS GS P DS 2 DS GS 2 DS P 2 DSUP UP UP UPDSΩ2UDSUP UP −UP= = = =ID 2IDSS ( UGS −UP)⎛U ⎞ ⎛GSU ⎞GS2IDSS⎜ −1⎟ 2IDSS⎜1−⎟⎝ UP⎠ ⎝ UP⎠IU2PAusgabe: 28.4.2005, G. Krucker

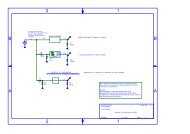

HTI Burgdorf 5-9Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.2 Arbeitspunkteinstellung<strong>FET</strong> zeigen für die Parameter U Pund I DSSwesentlich grössere Exemplarstreuungen als Bipolartransistoren.Für Labormuster kann es vorteilhaft sein die <strong>FET</strong>s auszumessen.Die Arbeitspunktstabilisierung bezweckt bei der <strong>FET</strong>-Schaltung die Abmilderung von Exemplarstreuungen,vor allem bei U Pund I DSS. Temperaturstabilisierung steht hier nicht im Vordergrund, weilbei <strong>FET</strong>s kein thermisches Hochlaufen des Drainstromes möglich ist.Die beiden Standardschaltungen für den einstufigen <strong>FET</strong>-Verstärker sind:r 1a.)U DDR 1I QR 3I DG DSr 1R 2AU R2 R 2R 4b.)U R2R 3I DG DSR 2R 4U DDBild 5-8: Arbeitspunkteinstellung beim einstufigen <strong>FET</strong>-Verstärker.a.) Einstellung mit Gatespannungsteiler.b.) Arbeitspunkteinstellung über Sourcewiderstand R 4.5.2.1 Arbeitspunkteinstellung über den SourcewiderstandDie einfache Form der Arbeitspunkteinstellung erfolgt nach Bild 3-10 b.).Die Dimensionierungs-vorgaben sind I DSS, U P, I D. Wird vom Hersteller ein Streubereich für U P, I DSSdefiniert, werden die Mittelwerte verwendet. Beste Resultate erhält man aber immer dann, wenn zuvorder <strong>FET</strong> in seinen Kenngrössen ausgemessen wird.RRRR4DD D 43=DS=2ID32−U⎛PI= 1I ⎜−D ⎝ IU −I ⋅RDD D 4 DS= wählbarDDDSS⎞⎟⎠U −I ⋅R −U=I( U U )R3( U : Vorgegeben)DS(5.18)(5.19)(5.20)Der Gatewiderstand R 2ist frei wählbar. Er beeinflusst direkt den Eingangswiderstand der Schaltung.Meist ist ein hoher Eingangswiderstand erwünscht, deshalb wird R 2gross gewählt. Praxiswerte liegen imBereich 100kΩ..33MΩ.Schaltungen mit extrem hohen Eingangswiderständen sind empfindlich gegenüber elektrischenStörungen, Kriechströmen und anderen Effekten. Es ist deshalb sinnvoll R 2nur so gross wie notwendigzu wählen.Der Drainwiderstand wird für Source- und Gateschaltung ohne Vorgabe für U DSmit (5.19) sodimensioniert, dass die verbleibende Spannung U CC-i DR 4hälftig über R 3und dem <strong>FET</strong> aufgeteilt wird.Wird ein U DSvorgegeben, wird nach (5.20) dimensioniert. Bei der Drainschaltung entfällt R 3.Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-10Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenBeispiel 5-2: Einfache Arbeitspunkteinstellung für eine <strong>FET</strong>-Stufe.Zu dimensionieren ist eine Schaltung mit einem P-Kanal <strong>FET</strong> für ein I D=-2mA. Der <strong>FET</strong> wurde zuvorausgemessen mit I DSS=-4.6mA und U P=3.2V. Die Speisespannung beträgt -15V. U DSsoll die halbeSpeisespannung betragen. Wie gross wird I Dund U DSmit E12-Normwerten?I DR 3T 1R 2R 4U DDVorgaben:U DD =-15VI DSS =-4.6mAU P =3.2VI D=-2mALösung:Da keine Einschränkung für den Eingangswiderstand vorliegt, wird R 2mit 1MΩ gewählt. Die weiterenBerechnungen erfolgen mit (5.18)-(5.20). Die Arbeitspunktberechnung erfolgt mit einem Knotenansatzund führt zu (5.25), wobei hier U R2=0V ist.Vorgaben:U DDU DD := −15VBerechnungen:−U P ⎛R 4 := ⋅ ⎜ 1 −I D ⎝U P := 3.2VI D ⎞I DSS ⎠U DD − I D ⋅ R 4 − U DSR 3 :=I DI DSS := −4.6mAI D := −2mAR 4 = 544.991ΩU DDU DS :=2R 3 = 3.205× 10 3 ΩI DT 1R 4R 2R 3Normwerte:R 3 :=R 4 :=normE( R 3 , E12)normE( R 4 , E12)R 3 = 3.3× 10 3 ΩR 4 = 560ΩBild 5-9:Berechnung und Schaltung zu Beispiel 5-2.Kontrollrechnung Arbeitspunkt:22U P − 2⋅ I DSS ⋅ R 4 ⋅ U P + U P ⋅ U P − 4⋅ I DSS ⋅ R 4 ⋅ U PI D1 :=22⋅ I DSS ⋅ R 422U P − 2⋅ I DSS ⋅ R 4 ⋅ U P − U P ⋅ U P − 4⋅ I DSS ⋅ R 4 ⋅ U PI D2 :=22⋅ I DSS ⋅ R 4I D1 = −0.017AI D2 = −1.972× 10 − 3 AI D := I D2( )U DS := U DD − I D ⋅ R 3 + R 4U DS = −7.386VAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-11Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.2.2 Arbeitspunkteinstellung über einen GatespannungsteilerDie Arbeitspunkteinstellung über einen Gatespannungsteiler nach Bild 5-8 a.) bietet eine Wahl von U Sohne grosse Rücksicht auf U GS. Ferner erlaubt diese Beschaltung eine bessere Stabilisierung bezüglichTemperaturschwankungen und Exemplarstreuungen.Da der Eingangswiderstand beim <strong>FET</strong> sehr gross ist (ca. 10 9 Ω) kann der Spannungsteiler R 1/R 2alsideale Spannungsquelle angesehen werden. R 2Adient zur Erhöhung des Eingangswiderstandes derSchaltung r 1. R 1und R 2sind normalerweise viel kleiner als der Eingangswiderstand des <strong>FET</strong> undwürden bei direkter Beschaltung den gesamten Eingangswiderstand r 1stark reduzieren. Mit R 2Akannder Eingangswiderstand r 1erhöht werden. Da kein Gatestrom fliesst, hat R 2Akeinen Einfluss auf denArbeitspunkt.U DDr 1U R2R 1I QR 3I DG DSR 2AR 2R 4Bild 5-10: Arbeitspunkteinstellung mit Gatespannungsteilerund Sourcewiderstand R 4.Die Parameter U Pund I DSSwerden normalerweise vom Hersteller im Datenblatt mit Minimal- undMaximalwerten angegeben. Typische Werte sind eher selten. Unter Berücksichtigung der Streuungwird R 4:R4=UPmax⎛ I ⎞ ⎛D max⎜1− ⎟−UPmin⎜1−⎝ IDSSmax ⎠ ⎝I − IDmaxDminIIDminDSS min⎞⎟⎠(5.21)Beim Spannungsteiler kann der Querstrom I Qoder ein Widerstand frei gewählt werden, z.B. R 2. Mitdiesen Vorgaben ergeben sich die Dimensionierungsgleichungen für R 1und R 2:UR =−U ⎛U = R⎞− 1U = U + I RU=⋅R⎝ ⎠RUwählbar, z.B.1uARDD R2 DD DD 21 2⎜⎟R2 GS D 4IQUR2 R1+R2R22= IQ=IQ2 A= wählbar(5.22)(5.23)Da kein Gatestrom fliesst, kann der Querstrom I Qsehr klein gewählt werden, ohne dass dieSchaltungseigenschaften negativ beeinflusst werden. Praktikable Werte für I Qliegen im uA-Bereich.Praxiswerte liegen im Bereich von 100kΩ..33MΩ.Bei der Dimensionierung mit Minimal- und Maximalwerten werden bei der Wechselstromdimensionierungimmer die Maximalwerte eingesetzt.Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-12Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenDer Drainwiderstand wird für Source- und Gateschaltung mit (5.19) oder (5.20) wie bei der einfachenArbeitspunkteinstellung dimensioniert.Ist der Arbeitspunkt mit dem Drainstrom I Dnicht vorgegeben, ist die Wahl von I DI =DIDSS min2(5.24)meist eine vernünftige Ausgangslage.Der Arbeitspunkt bei gegebener Beschaltung und Transistordaten ist:ID( − )U + 2 I R ( U − U ) ± U U + 4I R U U=2IR2 2P DSS 4 R2 P P P DSS 4 R2PDSS24(5.25)U R2bezeichnet die Spannung von Masse zum Gate der <strong>FET</strong>. Für die einfache Schaltung nach Bild 5-8b.)wird U R2=0 gesetzt. Für die Einstellung mit einem Gatespannungsteiler nach Bild 5-10 wird U R2über dieSpannungsteilerformel bestimmt.Beispiel 5-3: Arbeitspunkteinstellung mit Gatespannungsteiler.Man bestimme die Widerstandswerte R 1,..,R 4sowie wechselstrommässige Ein- undAusgangswiderstände r’ 1und r’ 2. Die zulässige Toleranz ∆I Dsoll ±0.1mA betragen.I DU DDKatalogdaten für den Transistor BC264B (N-Kanal J<strong>FET</strong>)R 1R 3U DGmax=30VBC264BU DSmax=±30VC 1I QP Dmax=300mWI DSS =3.5...6.5mAT C r'1 22 U P =-0.8..-2.5Vr' 1U DD=30Vr DS=100kΩR 2AU R2 R 2R 4 C 3Bild 5-11: Vorgaben für DC-Dimensionierung inBeispiel 5-3.Lösung:Der Drainstrom I Dwird nach (5.24) berechnet und gewählt. Die aus der Toleranz hervorgehendenMinimal- und Maximalwerte werden:I 3.5mA1.75 Wahl: 1.82 2I = I +∆ I = 1.8mA+ 0.1mA=1.9mADSS minID= = = mA ID= mADmaxD DI = I −∆ I = 1.8mA− 0.1mA=1.7mADminD DAusgabe: 28.4.2005, G. KruckerBild 5-12: Berechnung und Schaltung mit Komponentenwerten nach Berechnung zu Beispiel 5-1.

HTI Burgdorf 5-13Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenVorgaben:U DD := 30VU Pmin := −0.8VU Pmax := −2.5V∆I D := 0.1mAr DS := 100kΩI DSSmin := 3.5mAI DSSmax := 6.5mABerechnungen:⎛ I Dmax ⎞ ⎛U Pmax ⋅ ⎜ 1 −− U Pmin ⋅ ⎜ 1 −⎝ I DSSmax ⎠ ⎝R 4 :=I Dmax − I Dmin⎛ I Dmax ⎞U R2 := U Pmax ⋅ ⎜ 1 −+ I Dmax ⋅ R 4⎝ I DSSmax ⎠I Dmin ⎞I DSSmin ⎠R 4 = 4.578× 10 3 ΩU R2 = 7.303VWahl:I Q := 1µAU R2R 2 :=I QR 2 = 7.303× 10 6 Ω⎛ U DD ⎞R 1 := R 2 ⋅ ⎜ − 1⎝ U R2 ⎠Wahl:R 2A := 10MΩR 1 = 2.27× 10 7 ΩU DDC 2RR2A2I D=1.75±0.1mAR 1 R 322.7M5.819kC 1BC264BI Q=1uAr' 2=5.499kU DD − I Dmax ⋅ R 4R 3 :=2⋅I DmaxR 3 = 5.819× 10 3 Ω10MT 1R 1 ⋅ R 2r´1 := R 2A +R 1 + R 2r´2 :=r DS ⋅ R 3r DS + R 3r´1 = 1.552× 10 7 Ωr´2 = 5.499× 10 3 Ωr' 1 =15.52MU R27.303MR 44.578kC 3Herleitung der Gleichungen:Die Herleitung von (5.18),.., (5.20)und die Gleichungen (5.22),..,(5.23) sind elementar und werden hiernicht weiter gezeigt.Für die Gleichung (5.21) wird nach Bild 5-13 zur Bestimmung verwendet. Vorbereitend wird dieSpannung U 2bestimmt:U ⋅ RU = U + I R = I = I( )DD 22 GS D 4D SR1+R2(5.26)Will man einen Bereich für den Arbeitspunkt garantieren muss R 4über den Streubereich (5.27)U Pmin..U Pmaxund I DSSmin..I DSSmaxbestimmt werden. Mit einem grafischen Ansatz nach für R 4ergibt sich ausder Steigung Gl. (5.27):I D [mA]1/R 4U R21210I DSSmaxR'4=UGS maxIDmax− U− IGS minDmin1/R' 48642I DSSminI DmaxI Dmin[V] U GS-8 -6 -4 -2U Pmax U Pmin U GSmax U GSminBild 5-13: Grafischer Ansatz zur Bestimmung des Wertes für R 4unterBerücksichtigung der Streuungen von U Pund I DSS.Es macht Sinn, den kleineren Wert für U Pmit U Pmaxzu definieren, obwohl dies aus mathematischer Sichtnicht korrekt ist. Wir erhalten dafür aber eine Formel, die für N-Kanal und P-Kanal <strong>FET</strong> gültig ist.Mit Gl. (5.3) erhalten wir anschliessend:Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-14Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenR⎛ I ⎞ ⎛ I ⎞D maxD minUPmax⎜1− ⎟−UPmin⎜1−⎟IDSSmaxIDSSmin4=⎝ ⎠ ⎝ ⎠min

HTI Burgdorf 5-15Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenBeispiel 5-4: DC-Analyse einer Verstärkerstufe in Sourceschaltung.Gegeben sei die Verstärkerstufe nach Bild 5-15. Zu bestimmen sind:a.) I Db.) U DSU DD=12VGegeben:R 3I DSS =10mA1kU P=-3VC 2 u 2u 1 C 1Bild 5-15: Schaltbild zur DC-Analyse in Beispiel 5-4.R 2 R 41M 350 C 3Lösung:Der Drainstrom kann direkt mit (5.25) bestimmt werden. Die Spannung U R2beträgt 0V. Anschliessendkann über I Ddas U DSberechnet werden.Vorgaben:U DD := 12V U P := −3VI DSS := 10mAR 4 := 350ΩR 3 := 1kΩBerechnungen:22U P − 2⋅I DSS ⋅ U P ⋅ R 4 + U P U P − 4⋅ I DSS ⋅ R 4 ⋅ U PI D1 := I D1 = 3.5 × 10 − 3 A22⋅ I DSS ⋅ R 422U P − 2⋅R 4 ⋅ I DSS ⋅ U P − U P ⋅ U P − 4⋅R 4 ⋅ I DSS ⋅ U PI D2 := I D2 = 0.021A22⋅R 4 ⋅ I DSSI D := I D1( )U DS := U DD − I D ⋅ R 3 + R 4U DS = 7.275VAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-16Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.2.3 Der AbschnürbereichLiegt der Arbeitspunkt im Abschnürbereich, wird der <strong>FET</strong> als Verstärker betrieben. Per Definitionbeginnt der Abschnürbeiteich bei U DS>-U P+U GS. In diesem Bereich arbeitet der <strong>FET</strong> alsspannungsgesteuerte Stromquelle mit einem grossen r DS, erkennbar an den fast waagrechten Kurven fürI Dbei grösseren U DS.I DU GS =0VAbschnürbereichU GS =Param.U DSBild 5-16: Abschnürbereich des <strong>FET</strong>.-U PFür den Betrieb als Verstärker gelten für den <strong>FET</strong> folgende einfache Zusammenhänge:rDSDS= ≈→∞∆IDIyD21S∆U⎛ U= IDSS⎜1−⎝ UGSP⎞⎟⎠2dID2= = ID⋅IDSSdUUGS UDS= Konst.P(5.33)(5.34)(5.35)Die Steilheit y 21Sdes <strong>FET</strong> kann allgemein gültig durch (5.35) beschrieben werden. Die maximaleSteilheit y 21Smaxwird offensichtlich bei U GS=0V erreicht:y21Smax2 I DSS−= (5.36)UPAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-17Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.3 KoppelkondensatorenDie Koppelkondensatoren C 1und C 2definieren neben dem Sourcekondensator C Sdie untere Grenzfrequenzder Verstärkerschaltung. Sie werden vom Ansatz her genau gleich bestimmt wie bei einerStufe mit Bipolartransistoren.U DDR Gu GR 1r 2SR 3r' 2Sr' r 1S1Su 2u 1 C 1R 2AR 2C 2R LR 4C SBild 5-17: Koppel- und Überbrückungskondensatoren beimeinstufigen <strong>FET</strong>-Verstärker in Sourceschaltung.Für die Kondensatoren C 1,..,C 3nach Bild 5-17 gelten die Dimensionierungsgleichungen:1gudngud=gu⋅ −gu( G+1 )1 '2πfgudR r( L+2 )2 '2πfgudR r: Dimensionierungsgrenzfrequenzf f 2 1 f : Untere Grenzfrequenz der StufeCC==11fn: Anzahl wirksame Kondensatoren bei f'2 '2R4( rDS+ RL)( 1+ 21S DS ) + ⎡⎣4 ( 1+ 21S DS ) ⎤⎦− ( DS+L )CS='2πfgud R4( rDS + RL)'( RL= RLR3)y r R y r r R y≈2πf221Sgugud(5.37)(5.38)(5.39)(5.40)Die Kondensatoren C 1, C 2werden als Koppelkondensatoren in allen Grundschaltungen genau gleichdimensioniert.Der Kondensator C Szur wechselstrommässigen Überbrückung wird nur bei der Sourceschaltungverwendet.Die Herleitung der Gleichung (5.40) wird im entsprechenden Kapitel gezeigt. Für die Herleitung derGleichungen für C 1, C 2wird auf das Kapitel Bipolartransistoren im Skript verwiesen.Soll ein Koppelkondensator nicht frequenzbestimmend sein, wird sein Wert mit dem Faktor 10multipliziert. Damit ist sichergestellt, dass der Kondensator bei f gunicht wirksam ist.Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-18Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenBeispiel 5-5: Berechnung der Koppel- und Überbrückungskondensatoren.Zu dimensionieren sind alle Kondensatoren in der Schaltung nach Bild 5-18 für eine untereGrenzfrequenz von 30Hz. Alle Kondensatoren sind frequenzbestimmend.Gegeben:U DD=12V2.5mAI DSS=5mAU P =-3VR 3r DS =50kΩ1kR GCR L2u 26004.7kC 1u 1R 2 R 41M 350C 3Bild 5-18:Schaltung für die Berechnung der Kondensatoren inBeispiel 5-5.Lösung:Zuerst wird die Steilheit y 21Sfür Arbeitspunkt I D=2.5mA bestimmt. Anschliessend werden Ein- undAusgangswiderstände der Schaltung berechnet. Sie bilden die Grundlage für Dimensionierung derKondensatoren. Da alle Kondensatoren gemäss Aufgabenstellung frequenzbestimmend sind, wird miteiner Dimensionierungsgrenzfrequenz nach (5.37) gearbeitet.Vorgaben:R 2 := 1MΩ R 3 := 1kΩ R 4 := 350Ω R G := 600Ω R L := 4.7kΩU P := −3VI DSS := 5mA r DS := 100kΩ I D := 2.5mA f gu := 30Hzn := 3Berechnungen:2y 21S := ⋅ I D ⋅ I DSSU Py 21S = 2.357× 10 − 3 SR 3 ⋅ R LR' L :=R 3 + R Lr 1S := INFr' 1S := R 2r' 1S = 1× 10 6 Ωr 2S := r DSr 2S = 100× 10 3 Ωr DS ⋅ R 3r' 2S :=r DS + R 3r' 2S = 990.099× 10 0 Ωf gud := f gu ⋅1n2 − 1f gud = 15.295× 10 0 Hz1C 1 := C2π ⋅ f gud ⋅ ( R G + r' 1S )1 = 10.4× 10 − 9 F1C 2 := C2π ⋅ f gud ⋅ ( R L + r' 2S )2 = 1.829× 10 − 6 F( )( )( )( ) 22⋅ R 4 ⋅ r DS + R' L ⋅ 1 + y 21S ⋅ r DS + ⎡⎣ R 4 ⋅ 1 + y 21S ⋅ r DS ⎤⎦ 2 − r DS + R' LC 3 := C2π ⋅ f gud ⋅ R 4 ⋅ ( r DS + R' L )3 = 34.139× 10 − 6 Fy 21SC 3 :=2π ⋅ f gud(Näherung) C 3 = 24.527× 10 − 6 FAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-19Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.4 SourceschaltungDie Sourceschaltung hat charakteristisch eine hohe Spannungsverstärkung v US. Der Eingangswiderstandwird bei tiefen Frequenzen nur durch den Gatespannungsteiler bestimmt. AlleDimensionierungsformeln und Kenngrössen können ohne Aufwand aus dem vereinfachtenErsatzschaltbild hergeleitet werden.U DDR 1r 2Sr 1SC 2R 4 C 3r' 1Su 1u 2r' 2SC 1R 2R 2AR 3R LBild 5-19:Einstufiger <strong>FET</strong>-Verstärker inSourceschaltung.5.4.1 Kenngrössen der Sourceschaltungu r ⋅ Rv y R Rr'2DS L'US= =−21S ='L LR3u1rDS+ RL1S( )'1S 1S 2A1 22S=∞r = r R + R Rr= rDSr = r R'2SDS 3(5.41)(5.42)(5.43)(5.45)(5.44)Für die Herleitung der Gleichung sei auf die Kapitel 5.4.3, 5.4.4 verwiesen.Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-20Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.4.2 Wechselstrommässiges Ersatzschaltbild der SourceschaltungDas wechselstrommässige Kleinsignalersatzschaltbild mit dem <strong>FET</strong> als Y-Parameterblock wird für diegesamte Schaltung:GD(R 1||R 2)u y y 21S·u 1y+R 11Sy112S·u2 22S2AR 3u 2R Lr' 1Sr 1SSSr 2Sr' 2SBild 5-20: WechselstrommässigesErsatzschaltbild für die Verstärkerschaltung nachBild 5-19 .Zur Vereinfachung setzen wirangenommen werden.rDS1= . In NF-Bereich kann ohne weiteres y 11S=0 und y 12S=0y22SGD(R 1||R 2)u y 21S·u 1r1 +R DS2AR u R3 2LSSr' 1Sr 1Sr 2Sr' 2SBild 5-21: Vereinfachtes Ersatzschaltbild für dieVerstärkerschaltung nach Bild 5-19 .Aus dem Ersatzschaltbild ersieht man direkt die Zusammenhänge für r 1, r’ 1, r 2, r’ 2. DieSpannungsverstärkung v USwird ebenfalls sehr einfach bestimmt:R = R R'L3Luu y u r R v y r R y'' 2'DS L2=−21S ⋅1⋅DS L→US= =21S ⋅DS L=21 S'u1rDS+ RLr⋅ R(5.46)Bemerkung:-y 21S, weil i 2nach Definition in den Vierpol hinein fliesst.Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-21Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.4.3 Kenngrössen bei nicht überbrücktem SourcewiderstandWird der Sourcewiderstand nicht mit einem Kondensator wechselstrommässig überbrückt wirkt R SalsSerie-Serie-Gegenkopplung. Die maximal mögliche Stufenverstärkung wird dadurch herabgesetzt.Anders als bei den Bipolartransistoren erfolgt hier in der Regel keine Aufteilung des Sourcewiderstandesin einen wechselstrommässig aktiven Teil und inaktiven Teil, um so die Stufenverstärkunggezielt zu dimensionieren. Der Hauptgrund dafür ist in der kleineren maximal erreichbarenSpannungsverstärkung begründet.Der nicht überbrückte Sourcewiderstand wirkt auf die Spannungsverstärkung v Uund auf den Ausgangswiderstandr 2S. Es erfolgt ein starker Anstieg von r 2S. Für den Ausgangswiderstand r’ 2Sder gesamtenSchaltung wirkt sich dies aber eher wenig aus da r’ 2Smassgeblich vom Drainwiderstand R 3bestimmtwird.U DDR Gu GR 1r 2Sr' 2Sr'r 1S 1SC 2 u 2u 1C 1R SR 2R 2AR 3R LBild 5-22: Schaltbild mit Bezeichnungen für die Einstellungder Verstärkung über den Sourcewiderstand R S.Für den Sourcewiderstand nach Bild 5-22 gilt R S=R 4. Wobei R 4den Widerstandswert darstellt, der beider DC-Dimensionierung errechnet wurde.Die Kenngrössen für die Schaltung nach Bild 5-22 sind:'− y21S rDS RL'vUS = R'L= RLR3RL + rDS + RS + RSy21SrDSr2S = RS ( 1+ y21SrDS)+ rDSR'3⎡RS ( 1+ y21SrDS ) + rDS⎤r2S= R3 r2=⎣⎦R3+ RS ( 1+ y21SrDS ) + rDSr = R ( rDS→∞)'2S3(5.47)(5.48)(5.49)(5.50)Der Sourcewiderstand R Shat für den Eingangswiderstand der Schaltung keinen Einfluss. Er wirdgemäss (5.42), (5.43) bestimmt.Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-22Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenBeispiel 5-6: Ausgangswiderstand bei Sourceschaltung mit nicht überbrücktem R S.Man berechne die Ausgangswiderstände r 2und r’ 2der Schaltung nach Bild 5-23. Die Kenngrössen des<strong>FET</strong> sind y 21S=2.6mS, r DS=45kΩ.U DDR 33.3kr' 2C 2C 1R 2 R 410M 1kr 2Bild 5-23: Schaltung für die Berechnung derAusgangswiderstände in Beispiel 5-6.Lösung:Unter Verwendungen von (5.48), (5.49) findet man direkt:Vorgaben:y 21S := 2.6mS r DS := 45kΩ R S := 1kΩ R 3 := 3.3kΩBerechnungen:( )r 2 := R S ⋅ 1 + y 21S ⋅ r DS + r DSr 2 = 1.63× 10 5 Ωr 2 ⋅ R 3r´2 := r´2 = 3.235× 10 3 Ωr 2 + R 3Herleitung der Gleichung (5.47):Die Spannungsverstärkung wird über einen klassischen Knoten-Maschenansatz bestimmt. DieRechnung ist an sich nicht kompliziert, aber mit einem gewissen Aufwand verbunden.Wir zeichnen das Ersatzschaltbild mit den Knoten und Flussrichtungen der Spannungen und Ströme:i 1=0 A i 2GDu' 1y 21S·u' 1r DSBu 1Su 2R' LR Su RSu rDSBild 5-24:Schaltbild mit Bezeichnungen zur Bestimmung derVerstärkung bei nicht wechselstrommässig überbrücktemSourcewiderstand R S.Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-23Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenDie weitere Rechnung erfolgt mit Knoten/ Maschen nach Kirchhoff. In den Knoten A und B gilt:−uuA:= y21S( u1− uRS)+R2'L( 21 ) 21 1 2 (''y21Su1RLrDS + u2( RL + rDS)( )2' ' ''2 DS 21S 1 L DS 21S RS L DS 2 L RS L' ' ' 'RS S L DS L S L DS L DSRSB:y u u''21S L DS L2 RS21S1−RS+ =rDS21S 1 DS S 21S− ur− ur = y uRr − y u Rr + uR −u Ru y R r + R = y u R r + u R + ru=y R r + Ry ur R − y uDSu − u uRRSRSSRf DS S 2 S RS S RS DS( )21S 1 DS S 2 S RS DS S 21S DS SRSDS S 21S DS Sr R + u R − u R = u ry ur R + u R = u r + R + y r Ruy21Sur 1 DSRS + u2RS=r + R + y r R)Vorbereitende Zusammenhänge:i−u=22 'RLu = u + u u = u + u'2 rDS RS 1 1 RS' uA:i2 = y21Su1+rB:yu'21S1urrDSDSrDS+ =DSuRRSfZur Lösung nach v U=u 2/u 1werden beide Gleichungen gleichgesetzt:A=B:vU'( )y u R r + u R + r y ur R + u R'21S 1 L DS 2 L DS 21S 1 DS S 2 f=''y21SRLrDS + RL rDS + RS + y21SrDSRS( ) ⎤( ) ( )( )⎡⎣y u R r + u R + r⎦r + R + y r R = y u R r + u R y R r + R' ' ' '21S 1 L DS 2 L DS DS S 21S DS S 21S 1 S DS 2 S 21S L DS Ly u R r + y u R R r' 2 '21S 1 L DS 21S 1 S L DSyR R r2 ' 221S S L DS+y+yu R R r'21S 1 S L DSu R R r2 ' 221S 1 L S DS+'( )y+ uRr + uRRu R R r'21S 2 S L DS' 2 ' 2 221S 1 L rDS 2 L DS 2 DS 2 S DS 21S 2 S DS''21S 1 L DS 2 L 2 DS 2 S 21S 2 S DS'21S 1 L DS 2 L DS S 21S S DS''221S L DS 21S L DS''1 L DS S 21S S DS L DS 21S DS''2 L DS 2 S Ly uRr + uRr + ur + uRr + y uRr = 0y uRr + uR + ur + uR + y uRr = 0− y u R r = u R + r + R + y R ru −y R r −y R r= = =u R + r + R + y R r R + r + ( 1+ y r ) RS'+ uRR2 S L+yu R R r'21S 2 S L DS+ ur + uRr + y uRr =2 22 DS 2 S DS 21S 2 S DSAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-24Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenHerleitung der Gleichungen (5.48), (5.49):Für die Bestimmung der Ausgangswiderstände r 2, r’ 2wird Das Modell nach Bild 5-25 benutzt. DerAusgangswiderstand wird nach r’ 2=u Test/i Testberechnet.i 1R 2AGDu' 1y 21S·u' 1r DSBi Testu rDSu TestR 3u RSR SSVorbereitende Zusammenhänge:u = u + uTest rDS RSu = u + u u = 0 (weil i =0)u'R2 RS 1 R2 1RS=−u'1Bild 5-25: Schaltbild mit Bezeichnungen für die Bestimmungdes Ausgangswiderstandes bei nicht wechselstrommässigüberbrücktem Sourcewiderstand R S.Für die Knoten A und B gilt:u u u u − uA : i = + + y u = + − yB:y uTest RDS ' Test Test RSTest 21S 1 21S RSR3 rDSR3rDSRS'21S1( + ) −R ( 1+y r )u R r i R r→ u =urTest 3 DS Test 3 DSRDS+ =DSDS3 21S DSRSSTest RS RSDSuR' u − u u− y21Su1+ =r RuTestRS→ uRS=r y r( 1+)21S DSSuDie Gleichungen für u RSwerden gleichgesetzt und nach i Testaufgelöst. Anschliessend wird nach r’ 2umgeformt:'2'2 3( 3+ ) −3=R3( 1+ y21SrDS) rDS( 1+y21SrDS)i R3⎡R ( 1+ y21r ) + r→ uTest=⎣R3+ R ( 1+ y21r ) + ru R3⎡RS ( 1 y21SrDS ) rTest ⎣ + +DS⎤⎦i R + R ( 1+ y r ) + ru R r i R r u RrTest DS Test DS Test S= =Test S S DS DSTest 3 S 21S DS DSr = R ( r →∞)( 1 )( 1 )S S DS DSR3 RS + y21SrDS + rDSr2= lim⎡⎣⎤⎦ = R ( 1 + y21r ) + rR3→∞ R + R + y r + r3 S 21S DS DS⎤⎦DSS S DS DS(5.51)(5.52)Der Ausgangswiderstand r 2ohne Drainwiderstand R 3nach (5.52) lässt sich direkt aus (5.51) durchGrenzwertbildung bestimmen.Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-25Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.4.4 Der SourcekondensatorDer Sourcekondensator wird mit dem Ersatzschaltbild nach Bild 5 bestimmt. Von Interesse istdie Frequenz, bei der die Verstärkung v Ubei f gubetragsmässig um 3.01dB gegenüber der Maximalverstärkungv Umaxabgesunken ist.i 1=0 i 2GDdb[vu]u' 1y 21S·u' 1r DS u rDS2010Su u 2R' L10ZR SS C -10Su RS-2020dB/Dekv Umin0.1 1 10 100fgu2 fguv Umaxf [Hz]Bild 5-26: Schaltbild mit Bezeichnungen zur Herleitung der Dimensionierungsgleichung für den Sourcekondensator CSund typischer Amplitudengang. Die Grenzfrequenz fgu im Graphen wird durch den Sourcekondensator bestimmt.Für den Sourcekondensator gilt:C'2'( + )( + ) + ⎡⎣( + ) ⎤⎦− ( + )'2πfguRS ( rDS + RL)2R r R 1 y r R 1 y r r R2( R R R3)S DS L 21S DS S 21 S DS DS L'S=L=LCSy≈2πf21Sgu(5.53)(5.54)Die vereinfachte Formel (5.54) ist für die Praxis in Anbetracht der Bauteiletoleranzen meist genügendgenau. Der Fehler liegt je nach Wert für R Sim Bereich 5%..30%.Herleitungen der Gleichungen (5.53), (5.54):Mathematisch ist der Wert für C Sfür f gunach dem Amplitudengang in Bild 5-26 zu bestimmen:12=vvUfguUmax(5.55)Dies erfolgt unter Verwendung von (5.47), wobei R Sgegen den komplexen Widerstand Z S=R S||C Sersetzt wird. Die Maximalverstärkung v Umaxnach (5.41) ist ein Spezialfall von (5.47). Sie wird erreichtwenn Z S=0 gesetzt wird:1212−yR rR r y r Z R= =='21SL DS'L+DS+ ( 1+21S DS)S SZ'S− y21SRLrDS 1+jωRSCS'RL+ rDS'( rDS + RL )( 1+jωRS CS)'( 1+ ω ) + ( 1+ ω ) + ( 1+)r j RC R j RC R y rDS S S L S S S 21S DS(5.56)Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-26Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenDie formale Lösung von (5.56) ist wegen der aus Betragsrechnung resultierenden quadratischenGleichung aufwendig. Bequem ist dies aber mit einem Mathematikprogramm, wie z.B. Maple zu lösen:Mit einfachen algebraischen Umformungen und Einsetzen von w= 2πfguerhalten wir dieGleichung (5.53).Die vereinfachte Formel nach (5.54) weist einen Fehler im Prozentbereich auf. Unter demGesichtspunkt, dass die Toleranzen für die Bauteile meist 20% betragen, ist der Fehler mit derNäherungsformel in der Regel vertretbar.Die Richtigkeit der Näherung (5.54) begründet sich in der Vorgabe dass r DS→∞:limrDS→∞2( + )( + ) + ⎣ ( + ) ⎦ − ( + )'2πgu S ( DS+L )' '22 2S DS L 21S DS S 21S DS DS L S 21S S 21S2R r R 1 y r ⎡R 1 y r ⎤ r R Ry + 2Ry−1=f R r R 2πf RguS(5.57)Werden Praxiswerte für R Sund y 21Seingesetzt, wird 2R Sy 21S≈1. Die Näherung (5.57) vereinfacht sichweiter zu:CS2 2RyS 21S + 1−1y21S≈ =2πf R 2πf(5.58)gu S guAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-27Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenBeispiel 5-7: Frequenzbestimmender Sourcekondensator.Man bestimme den Wert des Sourcekondensators für eine Grenzfrequenz von 100Hz. DieKondensatoren C 1, C 2sind nicht frequenzbestimmend.Kenndaten des <strong>FET</strong>:y 21S=2.6mSr DS=100ku 1R 33.3kR 210M 2.2kC 2U DDC 1R 4C 3R L10kBild 5-27: Schaltbild für die Berechnung desSourcekondensators in Beispiel 5-7.Lösung:Unter Verwendung von (5.57), (5.58) findet man direkt:Vorgaben:R 4 := 2.2kΩ R 3 := 3.3kΩR L := 10kΩ f gu := 100Hzy 21S := 2.8mS r DS := 100kΩBerechnungen:R 3 ⋅ R LR' L := R' L = 2.481× 10 3 ΩR 3 + R L( )( )( )( ) 22⋅ R 4 ⋅ r DS + R' L ⋅ 1 + y 21S ⋅ r DS + ⎡⎣ R 4 ⋅ 1 + y 21S ⋅ r DS ⎤⎦ 2 − r DS + R' LC 3 := C2π ⋅ f gu ⋅ R 4 ⋅ ( r DS + R' L )3 = 4.983× 10 − 6 Fy 21SC 3 := (Näherung) C 3 = 4.456× 10 − 6 F2π ⋅ f guBeispiel 5-8: Vollständige Dimensionierung einer Verstärkerstufe in Sourceschaltung.Zu realisieren ist die Dimensionierung einer Sourceschaltung nach Bild 5-28. Bei der unterenGrenzfrequenz soll der Amplitudengang mit 20dB/Dekade sinken.U DDu GR 1r 2Sr' 2Sr'r 1S1S C 2 u 2u 1C 1R 2R 2AR 3R 4R LR GR 3'Bild 5-28: Schaltbild der zu dimensionierendenVerstärkerstufe in Beispiel 5-8.Vorgaben:U = 24V U =−3 V... − 6V I = 12 mA..15mA I = 5 ± 1mADD P DSS Dr = 50kΩ R = 2kΩ R = 1MΩ r ≥2MΩDS L G 1SI = 10µA U = 10V f = 300HzQ DS guAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-28Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenLösung:Zuerst wird die DC-Dimensionierung vorgenommen:Vorgaben:U DD := 24VU Pmin := −3VU Pmax := −6VU DS := 10VI Dmin := 4mAI Dmax := 6mAI DSSmin := 12mAI DSSmax := 15mAr' 1Smin := 2MΩR G := 1MΩf gu := 300Hzr DS := 50kΩR L := 2kΩI Q := 10µABerechnung der Widerstände:⎛ I Dmax ⎞ ⎛U Pmax ⋅ ⎜ 1 −− U Pmin ⋅ ⎜ 1 −⎝ I DSSmax ⎠ ⎝R 4 :=I Dmax − I DminI Dmin ⎞I DSSmin ⎠R 4 = 468.659× 10 0 ΩU DD − U DS − I Dmax ⋅ R 4R 3 :=I DmaxR 3 = 1.865× 10 3 Ω⎛ I Dmax ⎞U R2 := U Pmax ⋅ ⎜ 1 −+ I Dmax ⋅ R 4⎝ I DSSmax ⎠U R2 = 606.686× 10 − 3 VU DD − U R2R 1 :=I QR 1 = 2.339× 10 6 ΩU R2R 2 :=I QR 1 ⋅ R 2R 12 :=R 1 + R 2R 2 = 60.669× 10 3 ΩR 12 = 59.135× 10 3 ΩR 2Amin := r' 1Smin − R 12( )R 2Amin = 1.941× 10 6 Ω( )R 2A := ceilNormE R 2Amin , E12 = 2.2 × 10 6 ΩAnschliessend erfolgt die Bestimmung der Ein- und Ausgangswiderstände. Sie bilden auch dieGrundlage für die Dimensionierung der Kondensatoren. Aus der Vorgabe der Amplitudensteilheitergibt sich, dass nur ein Kondensator frequenzbestimmend sein darf. Hier wählt man C 3, weil derSourcekondensator in der Regel den grössten Wert hat. Alle anderen Kondensatoren werden ebenfallsauf die Grenzfrequenz dimensioniert, aber nachher mit dem Faktor 10 multipliziert. So haben C 1, C 2keinen Einfluss mehr auf die untere Grenzfrequenz. Die Verstärkung der gesamten Stufe im mittlerenFrequenzbereich wo die Kondensatoren wechselstrommässig als Kurzschlüsse betrachten werden, wirdnach (5.41) bestimmt:Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-29Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenEin- und Ausgangswiderstände:r' 1S := R 12 + R 2Ar 2S := r DSr DS ⋅ R 3r' 2S :=r DS + R 3r' 1S = 2.259× 10 6 Ωr 2S = 50 × 10 3 Ωr' 2S = 1.798× 10 3 ΩKondensatoren:2y 21S := ⋅ I Dmax ⋅ I DSSmaxU Pmaxy 21S = 3.162× 10 − 3 Sy 21SC 4 :=2π ⋅ f guC 4 = 1.678× 10 − 6 F10C 1 :=2π ⋅ f gu ⋅ ( R G + r' 1S )10C 2 :=2π ⋅ f gu ⋅ ( R L + r' 2S )(Nicht frequenzbestimmend)(Nicht frequenzbestimmend)C 1 = 1.628× 10 − 9 FC 2 = 1.397× 10 − 6 FR L ⋅ R 3R' L :=R L + R 3R' L = 964.984× 10 0 ΩSpannungsverstärkung:−y 21S ⋅ r DS ⋅ R' Lv U :=r DS + R' Lv U = −2.994×10 0Beispiel 5-9: Analyse Verstärkerstufe in Sourceschaltung.Gegeben ist die Verstärkerstufe nach Bild 5-29. Zu bestimmen sind:a.) v Uim mittleren Frequenzbereichb.) ∆v U, wenn ∆I D=I D±0.5mA beträgt.U DD=12VGegeben:R 3I DSS =10mA1kU P=-3VC 2 u 2u 1 C 1R 2 R 41M 350 C 3Bild 5-29: Schaltbild für die Berechnung derSpannungsverstärkung in Beispiel 5-9.Lösung:Der Drainstrom I Dwurde bereits in Beispiel 5-4 mit I D=3.5mA bestimmt. Die restlichen Berechnungenwerden mit (5.4) und (5.41):Vorgaben:U DD := 12VU P := −3VI DSS := 10mAR 4 := 350ΩR 3 := 1kΩ∆I D := 0.5mAI D = 3.5 × 10 − 3 ABerechnungen:R' L := R 3(weil kein rds spezifiziert)a.) v U2y 21S := ⋅ I D ⋅ I DSSU Py 21S = 3.944× 10 − 3 Sv US := −y 21S ⋅ R' Lv US = −3.944b.) ∆v U2∆y 21S := ⋅ ( I D + ∆I D ) ⋅ I DSS − I D − ∆I D ⋅U⎡⎣ P∆v U := −∆y 21S ⋅ R' L( ) I DSS⎤ ⎦∆y 21S = 5.649× 10 − 4 S∆v U = 0.565Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-30Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.5 GateschaltungDie Gateschaltung hat eine hohe Spannungsverstärkung. Der Eingangswiderstand ist klein und liegttypisch im 100Ω bis kΩ-Bereich. Der Ausgangswiderstand ist hoch und wird primär durch denDrainwiderstand R 3bestimmt. Vom Verhalten her ist die Gateschaltung mit der Basisschaltung zuvergleichen, jedoch ist die erreichbare Stufenverstärkung in der Regel kleiner.U DDR Gu GR 1r 2GC 2 uC 21r 1Gur' 1G1R 4R 2R 3r' 2GR LBild 5-30: Einstufiger <strong>FET</strong>-Verstärker inGateschaltung.5.5.1 Kenngrössen der Gateschaltung:( + 1)'UG21 S DS L'= R'L=rDS+ RLLvr1Gr=yDS21S( 1 )'( L+DS)'41G=4 1 G='RL + rDS + R4 + y21SrDSr R r( 1 )''2G DS 4 21S DS 4 4 G'2G3 2Gy r R'+ RLr + 1DSR R rr = r + R + y r R = R Rr = R r =R R (5.59)3(5.60)(5.61)(5.62)(5.63)Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-31Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.5.2 Herleitung der Gleichungen für die Kenngrössen der GateschaltungAusgehend vom Bild 5-30 wird das wechselstrommässige Ersatzschaltbild gemäss Bild 5-31 abgeleitet.Es bildet die Grundlage für alle nachfolgenden Betrachtungen. Da das Gate an Masse liegt, erfolgt einVorzeichenwechsel bei der Eingangsspannung. Für die Stromquelle in Bild 5-31 gilt daher –y 21Su 1.u GR GGDi 2-y 21S·u 1r DSi SR 3u1 2u 1r' 1GR 4r 1Gr 2G r' 2GR LBild 5-31: Wechselstrommässiges Ersatzschaltbild für dieGateschaltung nach Bild 5-30.Eingangswiderstand r 1GDer Eingangswiderstand der Schaltung wird über den Eingangswiderstand r 1Gam Sourceanschlussbestimmt. In den Knoten A und B gilt für die Schaltung nach Bild 5-32:BD-y 21S·u 1 r DSi 1 Su 2Au 1r 1GR' Lu + u = u R = R R'1 rDS 2 L L 3uA: i + − y u = 0 → u = u 1+ y r −ir( )rDS1 21S 1 2 1 21S DS 1 DSrDS( 1+)'urDSu21 L 21S DS21S1− − = →'2='rDS RL rDS + RLB: y u 0 uuR y rBild 5-32: Ersatzschaltbild für die Bestimmung des Eingangswiderstandes der Gateschaltung nachBild 5-31.Beide Knoten werden nach u 2umgestellt und gleichgesetzt. Der Eingangswiderstand r 1Gwird nachherdirekt:( 1+)uR y ru y r ir u y r i r R'1 L 21 S DS'1( 1+ 21S DS ) −1 DS= →'11+ 21S DS=1 DS+LrDS+ RLuR+ r'1 L DS1G= =i1 1 + y21SrDSr( ) ( )(5.64)Der Schaltungseingangswiderstand wird durch Parallelschaltung mit R 4bestimmt. Bemerkenswert sindauch die Grenzwerte bei r DS→∞:r1G∞'RL+ rDS1= lim =rDS→∞ 1 + y r y21S DS 21S'( L+DS)R R r R' 441 G∞= lim=r'DS →∞L+DS+4( 1+ 21S DS)1+21SrR r R y r y R 4(5.65)(5.66)Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-32Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenAusgangswiderstand r 2GDer Ausgangswiderstand wird r 2wird über u 2/i 2bestimmt. Für diese Betrachtung wird dasErsatzschaltbild vereinfacht.BD i 2-y 21S·u 1r DSSu 2rA2Gu R'14u = u u + u = u R = R R''1 1 1 rDS 2 4 4'u1 ' urDSu2R4A:=− y' 21Su1 + → u1=''R4 rDSrDS+ R4+ y21SR4ru u − i rB:i =− y u + → u = +' rDS2 2 DS2 21S1 1rDS1 y21SrDSBild 5-33: Ersatzschaltbild für die Bestimmung des Ausgangswiderstandes der Gateschaltung nachBild 5-31.GDSMit dem Gleichsetzen der Knotengleichungen für A und B findet man direkt den Ausgangswiderstanddes <strong>FET</strong>:uR u − i rr R y R r y r'2 42 2 DS='DS+4+21S 4 DS1+21S DSur = = r + R + y r( 1 )2'2G DS 4 21S DSi2(5.67)Der Schaltungsausgangswiderstand wird durch Parallelschaltung mit R 3bestimmt.Wird die Schaltung von einer idealen Spannungsquelle angesteuert, ist R G=0. Damit vereinfacht sich derAusgangswiderstand zu r 2G=r DS.Spannungsverstärkung v UGZur Herleitung der Spannungsverstärkung wird das Ersatzschaltbild nach Bild 5-31 angepasst. Es wirdwie in den vorhergehenden Fällen vorgegangen. Wie bei der Spannungsverstärkungsrechnung üblich,geht man davon aus, dass von einer Spannungsquelle eingespiesen wird. Daher ist nur der Drainknotenrelevant.BD-y 21S·u 1r DSSu 2u 1R' Lu + u = u R = R R'1 rDS 2 L 3 L'2urDSu2L' 21S1UGL DS 1DS( 1+)uR y rB: − + y u − = 0→ v =R r u r + R21S DS'LBild 5-34: Ersatzschaltbild für die Bestimmung der Spannungsverstärkung der Gateschaltung nachBild 5-31.Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-33Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenStromverstärkung v IGBei der Gateschaltung liegt wegen des endlichen Eingangswiderstandes keine leistungsloseAnsteuerung vor. Deshalb kann für diese Schaltung eine Stromverstärkung v IG=i 2/i 1definiert werden.' u2Bu1+ urDS= u2 u1 = u1 i2 =−'Ru 1i 2-y 21S·u 1r DSui 1S2R 4ADBild 5-35: Ersatzschaltbild für die Bestimmung derStromverstärkung der Gateschaltung nach Bild 5-31.R' Lu uiR rA:i − y u + = → u =' rDS 11 4 DS 2 41 21S1 1rDSR4 rDS+ y21SR4rDS' rDS2 21S1 1rDSZur Lösung werden die Knotengleichungen gleich gesetzt und u 2mit i 2beschrieben:'( DS+L )uu2r RB:i =− y u + → u =1+y rL+ u R21S DSu=−i R2 2'L'( ) ( 1 )vIG''( )'uiRr21 4 DS+ uR − iR2 4 2 LrDS + RL i − R24+ y21SrDS= → = =r + y R r 1+ y r i R r + R + y R r + R'( )DS 21S 4 DS 21S DS 1 L DS L 21S 4 DS L(5.68)Für den Fall r DS→∞ vereinfacht sich die Formel zu:vIG∞( 1 )− R + y r −y R= lim=rDS→∞R r R y R r R4 21S DS21S4'( + + ( )) R ( 121 4 )21 4+L+ ySR' ' 'L DS L S DS L(5.69)Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-34Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.6 DrainschaltungSie wird meist als Entkopplungsstufe oder Impedanzwandler verwendet und ist von den Eigenschaftenher ähnlich der Emitterfolgerschaltung bei den Bipolartransistoren.U DDR 1C 1C 2Bild 5-36:Einstufiger <strong>FET</strong>-Verstärker inr 1Du 2u 1r 2DR LR 2Au 2R 2R 4Drainschaltung.5.6.1 Kenngrössen der Drainschaltung:Für die Drainschaltung gelten die Dimensionierungsformeln:'21SL DS'UD= R'L=rDS + RL (1 + y21SrDS)4 Lvr1Dr2D=∞yrDS1= =1+ y r y + yr = r R'2D2D4R r21S DS 21S 22SR R (5.70)(5.71)(5.72)(5.73)5.6.2 Herleitung der Gleichungen für die DrainschaltungFür die Herleitungen wird das vereinfachte Ersatzschaltbild nach Bild 5-37 verwendet:GDu 1 u 2(R 1||R 2)y 21S·u 1r DS+R 2AR 4 R LSSr 2Dr' 2Dr'1Dr 1Di 2Bild 5-37: Vereinfachtes wechselstrommässigesErsatzschaltbild der Drainschaltung nach Bild 5-36.Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-35Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenEingangswiderstand r 1DDer Eingangswiderstand ist sofort ersichtlich und bedarf keiner weiteren Erläuterungen.Ausgangswiderstand r 2DDer Ansatz zur Bestimmung des Ausgangswiderstandes wird aus dem Ersatzschaltbild nach Bild 5-37abgeleitet.u 1 =0GDR' 2u'1 y 21S·u' 1r DSSAR 4r' 2Du2R Lu = 0 = u + u → u =−u''1 1 2 1 2u = u R = R RrDS'2 4 4L' urDSrDSA: i2 + y21Su1+ = 0 → r2D=rDS1 + y rDS21Sr 2DBild 5-38: Ersatzschaltbild für die Bestimmung des Ausgangswiderstandes der Drainschaltung nachBild 5-36.Für r DS→∞ strebt der Ausgangswiderstand nach:r2D∞rDS1= lim =r DS ←∞ 1 + y r y21S DS 21S(5.74)Spannungsverstärkung v UDFür den Ansatz zur Herleitung der Spannungsverstärkung v UDwird das Ersatzschalbild nach Bild 5-38verwendet.u = u + u u + u = 0 R = R R''1 1 2 2 rDS L 4 LA:y uu u+ =' rDS 221S1 'rDSRL−u u uy u u vR r(1 )'2 2 221SL DS21S( 1−2 ) + = →' UD= ='rDS RL u1 rDS + RL + y21SrDSy(5.75)Für grosse r DS(r DS→∞) strebt der Ausgangswiderstand nach:vUD∞y R r y R= lim=rDS→∞ r R y r y R''21S L DS 21S L''DS+L(1 +21S DS) 1+ 21SL(5.76)Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-36Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.7 IG<strong>FET</strong>Bei diesen <strong>FET</strong> ist das Gate mit einer dünnen Isolationsschicht vom Leitungskanal isoliert. Synonymwerden diese <strong>FET</strong> auch als MOS<strong>FET</strong> (Metal Oxide Semiconductor <strong>FET</strong>) bezeichnet.Die Steuerung des Stromflusses erfolgt durch Influenz. Das elektrische Verhalten des Kanals istpraktisch gleich wie beim J<strong>FET</strong>. IG<strong>FET</strong> werden heute grösstenteils für Leistungsanwendungeneingesetzt. Sie erlauben die praktisch leistungslose Steuerung von grossen Strömen.Für Kleinsignalanwendungen werden IG<strong>FET</strong> ebenfalls eingesetzt, bis in den HF-Bereich.Besonderheiten sind sog. Dual-Gate MOS<strong>FET</strong>. Sie verfügen über zwei Gateanschlüsse. Das zweiteGate dient zur Steuerung der Steilheit.Durch die Gateisolation sind IG<strong>FET</strong> sowohl selbstleitende Typen DMOS<strong>FET</strong> (bei U GS=0V) wie auchselbstsperrende Typen EMOS<strong>FET</strong> (bei U GS=0V) möglich. Umgangssprachlich werden selbstleitendeIG<strong>FET</strong> auch als Verarmungstypen bezeichnet und selbstsperrende Typen als Anreicherungstypen,obwohl das nicht ganz korrekt ist.I DI DU GS =+1VN-Kanal IG<strong>FET</strong>Verarmungstyp(Depletion, DMOS<strong>FET</strong>)AnreicherungsbereichVerarmungsbereichI DSSU GS =0VU GS=-1VU PU TO0U GS0U DS0U PU GS0U DSP-Kanal IG<strong>FET</strong>Verarmungstyp(Depletion, DMOS<strong>FET</strong>)I DSSVerarmungsbereichU GS =+1VU GS =0VAnreicherungsbereichI DU GS =-1VI DI DI DN-Kanal IG<strong>FET</strong>Anreicherungstyp(Enhancement, EMOS<strong>FET</strong>)AnreicherungsbereichU GS =+4VU GS =+3VU GS =+2V0U GS0U DSBild 5-39: Schaltsymbole undKennlinien der IG<strong>FET</strong>.U TO0U GS0U DSP-Kanal IG<strong>FET</strong>Anreicherungstyp(Enhancement, EMOS<strong>FET</strong>)AnreicherungsbereichU GS =-2VU GS =-3VU GS =-4VI DI DIG<strong>FET</strong> haben oft einen zusätzlichen Anschluss, das sog. Substrat-Gate auch Back-Gate genannt. Eswird im Regelfall mit dem Sourceanschluss verbunden. Über das Substrat-Gate kann die Steilheitbeeinflusst werden. Weiterführende Informationen zur Steuerungsfunktion des Substrat-Gate sind in[TEX76, S.113ff] zu finden.Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-37Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.7.1 Selbstleitende IG<strong>FET</strong>Sie sind vom Verhalten her genau gleich wie J<strong>FET</strong>s. Da aber IG<strong>FET</strong> keine Gate-Diode besitzen,können sie auch im Anreicherungsbereich (U GS>0V bei einem N-Kanal <strong>FET</strong>) betrieben werden.Die DC-Kenngrössen sind auch U Pund I DSS. Die formalen Zusammenhänge für U GS(I D) und I D(U GS)IUyD21S⎛ U= IDSS⎜1−⎝ UGS⎛= UP⎜1−⎝2=IDU⋅ IPGSPIIDSS⎞⎟⎠DDSS2⎞⎟⎠(5.77)(5.78)(5.79)5.7.2 Selbstsperrende IG<strong>FET</strong>Selbstsperrende IG<strong>FET</strong> arbeiten nur im Anreicherungsbereich. Man definiert hier eine Spannung U TO(Turn On Voltage). Sie definiert die Schwelle, bei der ein signifikanter Stromfluss einsetzt, ähnlich U Pbeim J<strong>FET</strong>. Die I D(U GS)-Kennlinie hat ebenfalls einen quadratischen Verlauf.( U −U ) II k U U U Uk2DGS TO DX 2= = ( − ) ∀2 P GS TO TO≤( UGSX−UTO)GSPIDX=( U −U)GSXTOU = U + ( U −U)GS TO GSX TO2IIDDXI DXI D0IDU TOU GSU GSXUGSBild 5-40: I D(U GS)-Kennlinie desselbstsperrenden IG<strong>FET</strong>.(5.80)(5.81)(5.82)Das Wertepaar (I D, U GSX) stellt einen beliebigen Punkt der in der I D(U GS)-Kennlinie dar. Der Parameterk Pist ein typspezifischer Parameter. Die Steilheit wird anlog zum J<strong>FET</strong>:y=2( U −U)21S D DXGSX TO2 I ( U −U)= = 2 kP( UGS −UTO)( )DX GS TO2UGSX−UTOI I(5.83)(5.84)Für Leistungsanwendungen verwendet man selbstsperrende IG<strong>FET</strong>. Sie können meist direkt mitLogikpegel angesteuert werden. Leistungs-IG<strong>FET</strong> haben aber in der Regel recht grosseGatekapazitäten (im nF Bereich). Die Ansteuerungsstufe muss bei Schaltvorgängen in der Lage seindiese Kapazitäten schnell umzuladen. Aus diesem Grunde ist die Steuerung nicht ganz leistungslos.Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-38Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenBegründung der Kennlinie und SteilheitDie Kennlinie nach muss als quadratische Funktion folgende Bedingungen erfüllen:f( U ) = 0GSf( U )GSUGS = UTOUGS = UGSXDXf( U ) = min f(U )GSUGS = UTO= IGSAus der ersten und dritten Forderung erkennt man, dass nur eine Parabel mit einer doppeltenNullstelle bei U TOdiese Bedingung erfüllt. Dies wird mit dem Binom im Zähler von (5.85) erfüllt. Diezweite Bedingung wird durch die Skalierung mit dem Nennerbinom und der Multiplikation mit I DXerfüllt. Das Nennerbinom setzt den Funktionswert bei U GSXauf 1. Mit I DXmultipliziert wird die zweiteBedingung erfüllt.ID2( UGS−UTO)=( U −U)GSXTO2IDX(5.85)Aus der Darstellung (5.85) kann durch Differenziation die Steilheit beim selbstsperrenden IG<strong>FET</strong>bestimmt werden und wir erhalten die Formel (5.84):I ( U −U)Iy I U2∂D∂GS TODX∂ 2 221S = = = ( − 2 +2 DX 2GSUGSUTO UTO ∂UGS ∂UGS ( UGSX −UTO ) ( UGSX −UTO ) ∂U)GS2=IDX ( UGS −UTO)2( U −U)GSXTOWird nun für U GSdie Beziehung (5.82) eingesetzt erhält man die Gleichung (5.83):y⎛I ⎞D2 IDX ⎜UTO + ( UGSX −UTO ) −UTO ⎟ 2 IDX ( UGSX −UTO)= =⎝IDXg⎠=21Sm2( U −U )( U −U ) 2 ( UGSX−UTO)GSXTOGleichung (5.82) lässt sich direkt durch algebraische Umformung aus (5.80)ableiten:GSXTOIIDDX=2I IDDXID( U −U ) I=( U )2GS TO DX2GSX−UTO2ID( UGS−UTO)=I ( U −U)DX GSX TO2ID( UGS−UTO)I= → UGS = UTO + ( UGSX −UTO)I ( U −U )IDX GSX TO DXD(5.86)Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-39Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.7.3 DC-DimensionierungSie erfolgt beim Verarmungstyp vom Vorgehen genau gleich wie bei einer J<strong>FET</strong>-Stufe. Es werdendieselben Parameter verwendet.Beim Anreicherungstyp ist das Vorgehen ähnlich. Als Besonderheit kann beim Anreicherungstyp eineStabilisierung des Arbeitspunktes gegenüber Exemplarstreuungen des <strong>FET</strong> mit einem Rückführwiderstandnach Bild 5-41c erfolgen.a.)U DDb.) c.)R DU DDU DDR DR G1R DR GR GU GGR G2Bild 5-41: Die Arbeitspunkteinstellung beim selbstsperrendenIG<strong>FET</strong> ist auf drei Arten üblich:a.) Arbeitspunkteinstellung mit fester Quelle UGG.b.) Einstellung mit Spannungsteiler.c.) Einstellung mit Rückführwiderstand.Der Rückführwiderstand stellt eine Parallel-Parallel-Gegenkopplung dar. Sie wirkt DC-mässig, wieauch im AC-Bereich. Dadurch sinken die Ein- und Ausgangswiderstände, sowie die Verstärkung derStufe. In vielen Fällen sind diese Folgen unerwünscht.Durch eine Beschaltung nach Bild 5-42 können diese Folgen im AC-Bereich eliminiert werden. DieWiderstände R G1, R G2sind typischerweise im MΩ-Bereich.U DDR DR G1R G2CBild 5-42: Durch die Aufteilung des RückführwiderstandesRG nach Bild 5-41c und Abblockkondensator C wirkt dieParallel-Parallel Gegenkopplung nur noch DC-mässig.Unterstellt man für die Schaltung nach Bild 5-42, dass die Spannung über dem <strong>FET</strong> und R Dhälftigaufgeteilt wird, wird der Wert für R D:RU⎛UDD⎞= ⎜U= U = ⎟(5.87)2 ⎠⎜2⎟⎝ ⎠DDD 2DS RD⎛UDD⎞⎝2 kP−UTOAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-40Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenBegründung der Gleichung (5.87)Für den Drainstrom gilt nach (5.81):I k U U U U2D=P( GS−TO)TO≤GS(5.88)Für eine maximal symmetrische Aussteuerbarkeit der Stufe wird U DS=U DD/2 gewählt.Da U GS=U DSwird(5.88)⎛UDD ⎞ID= kP⎜−UTO⎟UTO≤ U⎝ 2 ⎠2GS(5.89)Daraus folgt direkt der Wert für R D:RUU⎛U= = U = U =RD DD DDD 2⎜ DS RDID⎛U2DD ⎞⎝2 kP−UTO⎜⎝2⎟⎠⎞⎟⎠(5.90)Beispiel 5-10: DC Dimensionierung einer Stufe EMOS<strong>FET</strong>.Gegeben sei die Verstärkerstufe nach Bild 5-43. Zu bestimmen ist R Dfür maximale Aussteuerbarkeit:R G1=R G2=5MΩk P=0.0003A/V 2U TO=2.8VU DD=15VU DDR DR G1R G2u 1u 2CBild 5-43: Schaltbild für die Dimensionierung desDrainwiderstandes in Beispiel 5-10.Lösung:R Dwird direkt mit (5.87) bestimmt:Vorgaben:U DD := 15VU TO := 3Vk P := 0.0003⋅A V 2Berechnung:R D :=2⋅k PU DD⎛ U DD⋅ ⎜⎝ 2− U TO2⎞⎠R D = 1.235× 10 3 ΩAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-41Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.7.4 ArbeitspunktanalyseDie Analyse des Arbeitspunktes bei gegebener Beschaltung kann auf verschiedenartige Weise erfolgen.Grundsätzlich ist es möglich, aus den Kenngrössen U TOund I DX(U GSX) durch Verschiebung der Kennlinieein zugehöriges U Pund I DSSzu bestimmen und dann mit der bereits bekannten Arbeitspunktformel(5.25) zu rechnen.Alternativ kann ein direkter Ansatz erfolgen. U GSXund I DXverkörpern einen beliebigen Messwert in derKennlinie für ein U GS>U TObeim N-Kanal IG<strong>FET</strong>.I DU DDR 1R 3I QU DSU GSR 2 R 4Bild 5-44: Schaltbild zur DC-Analyse beimIG<strong>FET</strong>.( )U − I R = U = U + U −UR2 D 4 GS TO GSX TO( )U −I R − U = U −UR2 D 4 TO GSX TO( U −I R − U ) = ( U −U)2 2R2 D 4 TO GSX TOIIDDXIIDDXIIDDXDie quadratische Gleichung kann mit etwas Aufwand formal gelöst werden und man erhält dasResultat:( )D GSX TO2( ) 4 ( )U − U ± U − U + I R U −U U −UOI = U − U+ (5.91)GSX TO GSX TO DX 4 R2 TO R2T22IDXR4 R4Ausgabe: 28.4.2005, G. Krucker

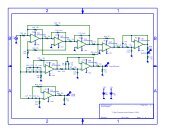

HTI Burgdorf 5-42Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenBeispiel 5-11: Analyse des Arbeitspunktes beim IG<strong>FET</strong>.Man bestimme I D, U GSund U DSder Verstärkerstufe in Bild 5-45:U DD =24VR 36.4kGegeben:I Dbei U GS=6V=40mA R 1R 2R 4U TO =1.8V40.5M1.1u100Mu 1 C 1 R 2A 100MR G80pU C 2 DSu 212.8M2.2kC 36.7uI DR L12kBild 5-45: Schaltbild für Arbeitspunktanalyse beim IG<strong>FET</strong>nach Beispiel 5-11 .Lösung:Zuerst wird I Dmit (5.91) bestimmt. Anschliessend wird U GSmit (5.86) berechnet. Aus I D, U DDund denWiderständen R 3,R 5ergibt sich aus der Maschengleichung direkt U DS.Vorgaben:U DD := 24VR 1 := 40.5MΩR 2 := 12.8MΩU TO := 1.8VR 4 := 2.2kΩR 3 := 6.4kΩI DX := 40mAU GSX := 6VBerechnungen:U DD ⋅ R 2U R2 :=R 1 + R 2U R2 = 5.764VUI D1 ( U GSX − U TO )GSX − U TO +:=⋅UI D2 ( U GSX − U TO )GSX − U TO −:=⋅I D := I D2( ) ( U GSX − U TO ) 2 + 4 I DX22⋅ I DX ⋅ R 4( ) ( U GSX − U TO ) 2 + 4 I DX22⋅ I DX ⋅ R 4( )⋅ ⋅ R 4 ⋅ U R2 − U TO( )⋅ ⋅ R 4 ⋅ U R2 − U TOU R2 − U TO+R 4U R2 − U TO+R 4I D1 = 2.255× 10 − 3 AI D2 = 1.439× 10 − 3 A(Richtige Lösung)( )U GS := U TO + U GSX − U TO ⋅I DI DXU GS = 2.597V( )U DS := U DD − I D ⋅ R 3 + R 4U DS = 11.62VAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-43Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenBeispiel 5-12: Analyse des Arbeitspunktes beim IG<strong>FET</strong> mit U Pund I DSS.Dieselbe Aufgabe wie Beispiel 5-11, jedoch soll mit der bereits bekannten Arbeitspunktgleichung fürJ<strong>FET</strong> gearbeitet werden.Lösung:Zuerst wird die I D(U GS)-Kennlinie um –U TOnach links verschoben. Nun definiert man U Pals –U TOundein fiktives I DSSwird nach (5.1) berechnet.U =− U =−1.8VIPDSSTOIDX= = 7.347mA⎛ U ⎞GSX⎜1−⎟⎝ UTO⎠I DI DXI D1U PEI DSSE0U' GSU TOU GSXU GSUGSVorbereitende Zusammenhänge:U ⋅ RU = U = I R +DD 2R2 DD D 3R1⋅R2Bild 5-46: Kennlinie und Umrechnung derKenngrössen vom IG<strong>FET</strong> zum J<strong>FET</strong> inBeispiel 5-12.( R )+ U4 DSNun wird die am Gate aktive Spannung U R2bestimmt. Für diese ist wegen des Vorzeichenwechsels vonU Pauch U R2negativ zu definieren.U−U R −24⋅12.8MDD 2R2= = =−R1+ R240.5M + 12.8M5.764VNun kann I Düber die Arbeitspunktformel (5.25) bestimmt werden. Es wird I D1verwendet, weil nurdieser Wert die Maschengleichung für U CCerfüllt.U R2 = −5.764VU P = −1.8VI DSS = 7.347× 10 − 3 A( )( )22U P − 2⋅ I DSS ⋅ R 4 ⋅ U R2 − U P + U P U P − 4⋅ I DSS ⋅ R 4 ⋅ U R2 − U PI D1 :=22⋅ I DSS ⋅ R 4( )( )22U P − 2⋅R 4 ⋅ I DSS ⋅ U R2 − U P − U P ⋅ U P − 4⋅R 4 ⋅ I DSS ⋅ U R2 − U PI D2 :=22⋅R 4 ⋅ I DSSI D1 = 1.439× 10 − 3 AI D2 = 2.255× 10 − 3 AI D := I D1( )U DS := U DD − I D ⋅ R 3 + R 4U DS = 11.62VU GS := −U R2 − I D ⋅ R 4U GS = 2.597V5.7.5 AC-Dimensionierung bei Schaltungen mit IG<strong>FET</strong>Die Wechselstromdimensionierung erfolgt genau gleich wie bei J<strong>FET</strong> Schaltungen. Aus diesem Grundwird auf die entsprechenden Kapitel und die weiterführenden Beispiele verwiesen.Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-44Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.8 Weiterführende BeispieleBeispiel 5-13: Analyse des Arbeitspunktes beim IG<strong>FET</strong> mit U Pund I DSS.Zu bestimmen sinda.) Alle Widerständeb.) Vu im mittleren Frequenzbereich.U DDR 2R 3R 1r 1EI QT 2C 1T 1U BT2u 1R 5R 4R 6T 1 : I DSS =30..40mAU P=-5..-7Vr DS =10kΩI D =(1±0.1)mAU DS =5Vu 2 RLVorgaben:T 2 : BC108CI C =4mAU CE=5VU DD = 24VI Q =1uAr' 1S=100MΩRR L =6kΩBild 5-47: Schaltbild zum Beispiel 5-13.Lösung:Zuerst werden die DC- und H-Parameter für den Transistor T2 aus dem Datenblatt gelesen:BC108C bei I =4mA und UCCE=5V:−4⎛5.5kΩ1.5⋅10⎞hE= ⎜⎟ UBE= 0.64VHFE= 560⎝ 620 100uS⎠Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-45Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenVorgaben :U DD := 24V I DSSmin := 30mA I DSSmax := 40mA U Pmin := −5VU Pmax := −7VI D := 1mA ∆I D := 0.1mA r DS := 10kΩ U DS := 5VU CE := 5V I Q := 1µAR L := 6kΩr´1S := 100MΩ I C := 4mAAus dem Datenblatt BC108C bei I C =4mA, U CE =5V:h 11e := 5.5kΩ h 12e := 1.5 ⋅ 10 − 4 h 21e := 620 h 22e := 100µSU BE := 0.64V H FE := 560Berechnungen <strong>FET</strong>-Stufe:I Dmin := I D − ∆I DI Dmin = 9× 10 − 4 AI Dmax := I D + ∆I DI Dmax = 1.1 × 10 − 3 A⎛ I Dmax ⎞ ⎛ I Dmin ⎞U Pmax ⋅ ⎜ 1 −− U Pmin ⋅ ⎜ 1 −⎝ I DSSmax ⎠ ⎝ I DSSmin ⎠R 6 := R 6 = 8.526× 10 3 ΩI Dmax − I Dmin⎛ I Dmax ⎞U GS := U Pmax ⋅ ⎜ 1 −⎝ I DSSmax ⎠U GS = −5.839VU R5 := U GS + I Dmax ⋅ R 6U R5 = 3.539VU DD − U R5R 1 := R 1 = 2.046× 10 7 ΩI QU R5R 5 := R 5 = 3.539× 10 6 ΩI QR 1 ⋅ R 5R1R5:= R1R5 = 3.017× 10 6 ΩR 1 + R 5R 4min := r´1S − R1R5R 4min = 9.698× 10 7 ΩR 4 := 100MΩ(Wahl)U DD − U DS − I Dmax ⋅ R 6R 2 := R 2 = 8.69× 10 3 ΩI CI Dmax +H FEDie Dimensionierung der Bipolarstufe erfolgt auf der bereits definierten Spannung U BT2:Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-46Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenBerechnungen Bipolar-Stufe:U BT2 := I Dmax ⋅ R 6 + U DSU BT2 − U BER 7 :=1I C ⋅ ⎛ 1 + ⎞⎜⎝ H FE ⎠1U DD − U CE − I ⎛ C ⋅ ⎜ 1 + ⎞ ⋅ R 7⎝ H FE ⎠R 3 :=I CU BT2 = 14.379VR 7 = 3.429× 10 3 ΩR 3 = 1.315× 10 3 ΩSpannungsverstärkungen:R L ⋅ R 3R´LT2 :=R L + R 3detHe := h 11e ⋅ h 22e − h 12e ⋅ h 21eR´LT2 = 1.079× 10 3 ΩdetHe = 0.457h 11e + detHe ⋅ R´LT2r 1E :=1 + h 22e ⋅ R´LT2r 1E = 5.409× 10 3 ΩR 2 ⋅ r 1ER´LT1 :=R 2 + r 1E(Last für Transistor T1)R´LT1 = 3.334× 10 3 Ω2y 21S :=U Pmax⋅I Dmax ⋅ I DSSmaxy 21S = 1.895× 10 − 3 S−y 21S ⋅ r DS ⋅ R´LT1v UT1 :=R´LT1 + r DSv UT2 :=−h 21ev Utot := v UT1 ⋅ v UT2⋅ R´LT2h 11e + detHe ⋅ R´LT2v UT1 = −4.739v UT2 = −111.609v Utot = 528.897Beispiel 5-14: Regelverstärker mit J-<strong>FET</strong>.Gesucht: V USbei U R=0V und U R=2V im mittleren Frequenzbereich der Schaltung nach Bild 5-48.U DDR 2C 3u T1:2I DSS = 25mAu 1 C 2 U P = -5VVorgaben:u 1 :

HTI Burgdorf 5-47Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren2 22 2UGS IDR3 −IDR3 IDR3D=DSS1− =DSS1− =DSS1− 2 +2UP UP UP UP⎛ ⎞ ⎛ ⎞ ⎛ ⎞I I ⎜ ⎟ I ⎜ ⎟ I ⎜ ⎟⎝ ⎠ ⎝ ⎠ ⎝ ⎠I I R I I R0= I + 2 − +DSS2 2D DSS 3 D DSS 3ID2UPUP( )0= U I + 2I I RU − I U + I I R = U I + I U 2I R − U + I I R2 2 2 2 2 2P DSS D DSS 3 P D P D DSS 3 P DSS D P DSS 3 P D DSS⎛0.00592237⎞→ ID= ⎜⎟mA⎝0.0225028⎠Die gesamte Rechnung wird mit MathCad:23Vorgaben:I DSST1 := 25mA U PT1 := −5VI DSST2 := −15mAU PT2 := 3VR 2 := 1.8kΩR 3 := 433ΩArbeitspunkt bestimmen:⎛ 5.9255×10 − 3 ⎞r := nullstellen( v) ⋅ Ar = ⎜A⎝ 0.0225 ⎠⎡21U PT1 ⋅ IDSST1 ⋅ ⎤⎢⎥⎥⎥⎥⎥⎢V 2⎢AUv PT1 ⋅ ( 2⋅ I DSST1 ⋅ R 3 − U PT1 ) ⋅:= ⎢⎢V 2⎢2 A 2 ⎥⎢I DSST1 ⋅ R 3 ⋅ ⎥⎥⎦⎢⎣V 2rI D := r 1I D = 0.0225A(1. Lösung wählen)rDSΩ bestimmen:U GS := 0Vr DSΩ0V :=U GS := 2V−U PT2⎛ U GS ⎞2⋅ I DSST2 ⋅ ⎜ 1 −⎝ U PT2 ⎠r DSΩ0V = 100Ω−U PT2r DSΩ2V := r DSΩ2V = 300Ω⎛ U GS ⎞2⋅ I DSST2 ⋅ ⎜ 1 −⎝ U PT2 ⎠R 3 ⋅ r DSΩ0VR S0V := R S0V = 81.2383ΩR 3 + r DSΩ0Va.)R 3C 2T 2u RR 3r 1DS (U R )b.)R 3 ⋅ r DSΩ2VR S2V := R S2V = 177.2169ΩR 3 + r DSΩ2VSteilheit im Arbeitspunkt:Bild 5-49: RS0V,RS2V bilden sich aus derParallelschaltung von R3 und dem rDS des<strong>FET</strong>.⎡ ⎛ I D ⎞⎢⎤−2⋅ ⎜ ⎥⎥⎥⎦⎢ ⎝ I DSST1 ⎠y 21ST1 := I DSST1 ⋅ ⎢y 21ST1 = 9.4874× 10 − 3 S⎣ U PT1Verstärkungen:R´L := R 2−y 21ST1 ⋅ R´Lv US0V := v US0V = −9.64421 + y 21ST1 ⋅ R S0V−y 21ST1 ⋅ R´Lv US2V := v US2V = −6.3691 + y 21ST1 ⋅ R S2VAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-48Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.9 Literaturverzeichnis[GRA71] Operational Amplifiers, Jerald Graeme/ Gene Tobey, McGraw-Hill 1971,ISBN 07-064917-0[HOE85]SPICE- Analyseprogramm für elektronische Schaltungen, E. Hoefer/ H. Nielinger,Springer Verlag 1985, ISBN 3-540-15160-5[KRU-ME98] Skript Mikroelektronik I, Kapitel Bipolartransistoren, Gerhard Krucker, 1998.[TEX77] Das <strong>FET</strong> Kochbuch, Texas Instruments Deutschland 1977, ISBN 3-88078-001-3[THO76] Bauelemente der Halbleiterelektronik, H.Tholl, Verlag Teubner 1976,ISBN 3-519-06418-9[TOB71] Operational Amplifiers, J. Graeme/ G. Tobey/ L. Huelsman, Mc Graw-Hill 1971,ISBN 07-064917-0Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-49Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.10 Datenblätter5.10.1 BF245Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-50Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-51Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-52Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-53Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-54Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-55Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-56Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-57Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-58Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.10.2 MPF102Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-59Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-60Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-61Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-62Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.10.3 2N5114, 2N5115, 2N5116Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-63Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-64Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-Transistoren5.10.4 BS170Ausgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-65Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-66Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-67Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-68Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenAusgabe: 28.4.2005, G. Krucker

HTI Burgdorf 5-69Analoge Systeme 2 (<strong>ELA5</strong>)Feldeffekt-TransistorenAusgabe: 28.4.2005, G. Krucker