Einführing in sequentielle Logik mit PLD - der HTL Steyr

Einführing in sequentielle Logik mit PLD - der HTL Steyr

Einführing in sequentielle Logik mit PLD - der HTL Steyr

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

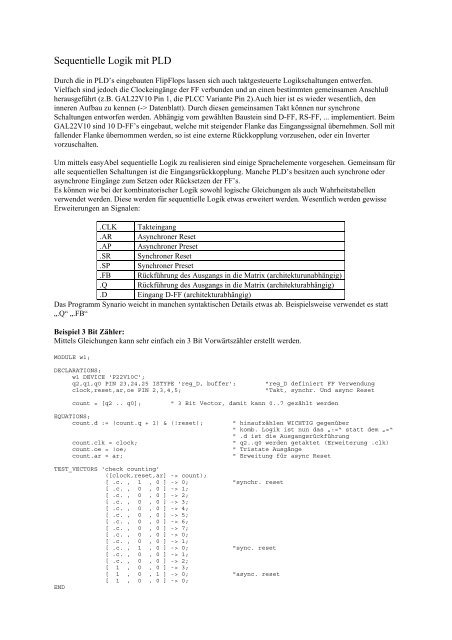

Sequentielle <strong>Logik</strong> <strong>mit</strong> <strong>PLD</strong><br />

Durch die <strong>in</strong> <strong>PLD</strong>’s e<strong>in</strong>gebauten FlipFlops lassen sich auch taktgesteuerte <strong>Logik</strong>schaltungen entwerfen.<br />

Vielfach s<strong>in</strong>d jedoch die Clocke<strong>in</strong>gänge <strong>der</strong> FF verbunden und an e<strong>in</strong>en bestimmten geme<strong>in</strong>samen Anschluß<br />

herausgeführt (z.B. GAL22V10 P<strong>in</strong> 1, die PLCC Variante P<strong>in</strong> 2).Auch hier ist es wie<strong>der</strong> wesentlich, den<br />

<strong>in</strong>neren Aufbau zu kennen (-> Datenblatt). Durch diesen geme<strong>in</strong>samen Takt können nur synchrone<br />

Schaltungen entworfen werden. Abhängig vom gewählten Bauste<strong>in</strong> s<strong>in</strong>d D-FF, RS-FF, ... implementiert. Beim<br />

GAL22V10 s<strong>in</strong>d 10 D-FF’s e<strong>in</strong>gebaut, welche <strong>mit</strong> steigen<strong>der</strong> Flanke das E<strong>in</strong>gangssignal übernehmen. Soll <strong>mit</strong><br />

fallen<strong>der</strong> Flanke übernommen werden, so ist e<strong>in</strong>e externe Rückkopplung vorzusehen, o<strong>der</strong> e<strong>in</strong> Inverter<br />

vorzuschalten.<br />

Um <strong>mit</strong>tels easyAbel <strong>sequentielle</strong> <strong>Logik</strong> zu realisieren s<strong>in</strong>d e<strong>in</strong>ige Sprachelemente vorgesehen. Geme<strong>in</strong>sam für<br />

alle <strong>sequentielle</strong>n Schaltungen ist die E<strong>in</strong>gangsrückkopplung. Manche <strong>PLD</strong>’s besitzen auch synchrone o<strong>der</strong><br />

asynchrone E<strong>in</strong>gänge zum Setzen o<strong>der</strong> Rücksetzen <strong>der</strong> FF’s.<br />

Es können wie bei <strong>der</strong> komb<strong>in</strong>atorischer <strong>Logik</strong> sowohl logische Gleichungen als auch Wahrheitstabellen<br />

verwendet werden. Diese werden für <strong>sequentielle</strong> <strong>Logik</strong> etwas erweitert werden. Wesentlich werden gewisse<br />

Erweiterungen an Signalen:<br />

.CLK Takte<strong>in</strong>gang<br />

.AR Asynchroner Reset<br />

.AP Asynchroner Preset<br />

.SR Synchroner Reset<br />

.SP Synchroner Preset<br />

.FB Rückführung des Ausgangs <strong>in</strong> die Matrix (architekturunabhängig)<br />

.Q Rückführung des Ausgangs <strong>in</strong> die Matrix (architekturabhängig)<br />

.D E<strong>in</strong>gang D-FF (architekturabhängig)<br />

Das Programm Synario weicht <strong>in</strong> manchen syntaktischen Details etwas ab. Beispielsweise verwendet es statt<br />

„.Q“ „.FB“<br />

Beispiel 3 Bit Zähler:<br />

Mittels Gleichungen kann sehr e<strong>in</strong>fach e<strong>in</strong> 3 Bit Vorwärtszähler erstellt werden.<br />

MODULE w1;<br />

DECLARATIONS;<br />

w1 DEVICE 'P22V10C';<br />

q2,q1,q0 PIN 23,24,25 ISTYPE 'reg_D, buffer'; "reg_D def<strong>in</strong>iert FF Verwendung<br />

clock,reset,ar,oe PIN 2,3,4,5; "Takt, synchr. Und async Reset<br />

count = [q2 .. q0]; " 3 Bit Vector, da<strong>mit</strong> kann 0..7 gezählt werden<br />

EQUATIONS;<br />

count.d := (count.q + 1) & (!reset); " h<strong>in</strong>aufzählen WICHTIG gegenüber<br />

" komb. <strong>Logik</strong> ist nun das „:=“ statt dem „=“<br />

" .d ist die Ausgangsrückführung<br />

count.clk = clock; " q2..q0 werden getaktet (Erweiterung .clk)<br />

count.oe = !oe; " Tristate Ausgänge<br />

count.ar = ar; " Erweitung für async Reset<br />

TEST_VECTORS 'check count<strong>in</strong>g'<br />

([clock,reset,ar] -> count);<br />

[ .c. , 1 , 0 ] -> 0; "synchr. reset<br />

[ .c. , 0 , 0 ] -> 1;<br />

[ .c. , 0 , 0 ] -> 2;<br />

[ .c. , 0 , 0 ] -> 3;<br />

[ .c. , 0 , 0 ] -> 4;<br />

[ .c. , 0 , 0 ] -> 5;<br />

[ .c. , 0 , 0 ] -> 6;<br />

[ .c. , 0 , 0 ] -> 7;<br />

[ .c. , 0 , 0 ] -> 0;<br />

[ .c. , 0 , 0 ] -> 1;<br />

[ .c. , 1 , 0 ] -> 0; "sync. reset<br />

[ .c. , 0 , 0 ] -> 1;<br />

[ .c. , 0 , 0 ] -> 2;<br />

[ 1 , 0 , 0 ] -> 3;<br />

[ 1 , 0 , 1 ] -> 0; "async. reset<br />

[ 1 , 0 , 0 ] -> 0;<br />

END

Beispiel 3 Bit synchrones Schieberegister <strong>mit</strong> parallel Load<br />

MODULE W9<br />

TITLE '3 Bit synchronous Schieberegister <strong>mit</strong> parallel load<br />

W.Reis<strong>in</strong>ger <strong>HTL</strong> <strong>Steyr</strong> 24 Jan. 1998'<br />

W9 DEVICE 'P22V10C';<br />

clk,load,reset PIN 2,12,13;<br />

i0,i1,i2, PIN 3,4,5;<br />

q0,q1,q2 PIN 17,18,19 ISTYPE 'BUFFER,REG_D';<br />

Out = [q2,q1,q0];<br />

Inp = [i2,i1,i0];<br />

EQUATIONS<br />

Out := load & [q1,q0,i0];<br />

Out := !load & [i2,i1,i0];<br />

Out.C = clk;<br />

Out.AR = !reset;<br />

TEST_VECTORS 'shiftregister'<br />

([clk, Inp, reset, load] -> [q2,q1,q0])<br />

[ 0, 0 , 0, 1] -> [ 0, 0, 0];<br />

[.C., 1 , 1, 1] -> [ 0, 0, 1];<br />

[.C., 0 , 1, 1] -> [ 0, 1, 0];<br />

[.C., 3 , 1, 0] -> [ 0, 1, 1];<br />

[.C., 0 , 1, 1] -> [ 1, 1, 0];<br />

[.C., 1 , 1, 1] -> [ 1, 0, 1];<br />

END<br />

Die Darstellung <strong>mit</strong>tels Wahrheitstabelle anstelle e<strong>in</strong>er Gleichung („EQUATIONS“)ist <strong>in</strong> vielen Fällen zu<br />

kompliziert.<br />

Pr<strong>in</strong>zipielle schreibweise:<br />

TRUTH_TABLE ([q1.fb, q0.fb, start]:> [q1, q0] -> [A, B])<br />

[ 1, 1, 1]:> [ 1, 1] -> [1, 1]);<br />

[ 1, 1, 0]:> [ 0, 0] -> [1, 1]);<br />

[ 0, 0, 1]:> [ 1, 1] -> [0, 1]);<br />

[ 0, 0, 0]:> [ 0, 0] -> [1, 0]);<br />

würde wie folgt gelesen:<br />

(1. Zeile) Ich bef<strong>in</strong>de mich im Zustand [1 1] und bleibe solange start==1 ist <strong>in</strong> diesem Zustand und gebe<br />

A=1 und B=1 aus.<br />

(2. Zeile) Wird start == 0 so gehe ich <strong>in</strong> den Zustand [ 0, 0] und gebe A=1 und B=1 aus.<br />

Wesentlich übersichtlicher s<strong>in</strong>d sogenannte Zustands Diagramme, welche pr<strong>in</strong>zipiell das selbe formulieren<br />

Beispiel RS-FF<br />

Set=0 &<br />

Reset=.X.<br />

Set=1 & Reset=0<br />

S1 S2<br />

Set=0 & Reset=1<br />

Set=.X. &<br />

Reset=0<br />

E<strong>in</strong> Diagramm <strong>mit</strong> solch e<strong>in</strong>em sussehen (vom Stil her) nennt man Moore Diagramm!

Als weitere Möglichkeit zusätzlich zu Wahrheitstabellen und Gleichungen gibt es weiters sogenannte<br />

Zustandsdiagramme („STATE_DIAGRAM“) die e<strong>in</strong> oben gezeigtes Diagramm abbilden.<br />

MODULE MOORE<br />

TITLE 'RS-FF als Moore Automat'<br />

CLOCK PIN;<br />

RESET PIN;<br />

SET PIN;<br />

QOUT PINISTYPE 'REG_D';<br />

NQOUT PIN; "<strong>in</strong>vertierter Ausgang als<br />

"komb<strong>in</strong>atorische Verknüpfung<br />

EQUATIONS<br />

QOUT.CLK = CLOCK;<br />

STATE_DIAGRAM QOUT<br />

STATE 0:<br />

NQOUT = !QOUT<br />

IF SET == 1 THEN 1; ELSE 0;<br />

STATE 1:<br />

NQOUT = !QOUT;<br />

IF RESET == 1 THEN 0; ELSE 1;<br />

END MOORE;<br />

Zu berücksichtigen ist hier, daß <strong>der</strong> Invertierte QOUT erst etwas später zur Verfügung steht als QOUT, da<br />

QOUT zuvor <strong>in</strong> die UND-Matrix zurückgeführt wird. Durch E<strong>in</strong>führung weiterer Zustände könnte NQOUT<br />

auch aus den Zuständen generiert werden.<br />

Beispiel: Vorwärts/Rückwärts Zähler bis 5 <strong>mit</strong>tels Zustandsdiagramm<br />

zu beachten ist <strong>in</strong> diesem Fall, daß dafür 3 Bit notwendig s<strong>in</strong>d und daher ungültige Zustände beim E<strong>in</strong>schalten<br />

auftreten können. Diese müssen geson<strong>der</strong>t auskodiert und. ev. auch getestet werden. In diesem Beispiel werden<br />

ke<strong>in</strong>e komb<strong>in</strong>atorischen Ausgänge verwendet.<br />

Dieses Beispiel zeigt auch wie Zähler simuliert werden und wie e<strong>in</strong> Zähler auf e<strong>in</strong>en gewissen Wert gesetzt<br />

werden kann.<br />

module W56<br />

title 'counter forward/backward 0 til 5 with clear<br />

Wolfgang Reis<strong>in</strong>ger 2.1.98'<br />

w56 device 'P22V10C';<br />

Clk,Clr,OE,Dir p<strong>in</strong> 2,3,4,5;<br />

Q2,Q1,Q0 p<strong>in</strong> 20,21,23 istype 'reg_D,buffer';<br />

Ck,X,Z,P = .C. , .X., .Z., .P.;<br />

equations<br />

[Q2,Q1,Q0].clk = Clk; "Takt<br />

[Q2,Q1,Q0].oe = !OE; "Outputanable kann man immer brauchen

state_diagram [Q2,Q1,Q0]<br />

State 0: IF Clr THEN 0 ELSE IF !Dir THEN 1 ELSE 5;<br />

" ich bef<strong>in</strong>de mich im Zustand 0 und bleibe bei Clr == 1 <strong>in</strong><br />

" diesem Zustand. Bei Clr == 0 wird <strong>in</strong> Abhängigkeit von Dir <strong>in</strong><br />

" den nächsten bzw. <strong>in</strong> den vorherigen Zustand gewechselt.<br />

State 1: IF Clr THEN 0 ELSE IF !Dir THEN 2 ELSE 0;<br />

State 2: IF Clr THEN 0 ELSE IF !Dir THEN 3 ELSE 1;<br />

State 3: IF Clr THEN 0 ELSE IF !Dir THEN 4 ELSE 2;<br />

State 4: IF Clr THEN 0 ELSE IF !Dir THEN 5 ELSE 3;<br />

State 5: IF Clr THEN 0 ELSE IF !Dir THEN 0 ELSE 4;<br />

"Ensure return from illegal state<br />

State 6: GOTO 0;<br />

State 7: GOTO 0;<br />

test_vectors 'Test Counter'<br />

( [Clk ,OE, Clr, Dir ] -> [Q2,Q1,Q0])<br />

[ Ck , 0, 1 , 0 ] -> 0;<br />

[ Ck , 0, 0 , 0 ] -> 1;<br />

[ Ck , 0, 0 , 0 ] -> 2;<br />

[ Ck , 0, 0 , 0 ] -> 3;<br />

[ Ck , 0, 0 , 0 ] -> 4;<br />

[ Ck , 0, 0 , 0 ] -> 5;<br />

[ Ck , 0, 0 , 0 ] -> 0;<br />

[ Ck , 0, 0 , 0 ] -> 1;<br />

[ Ck , 0, 0 , 1 ] -> 0;<br />

[ Ck , 0, 0 , 1 ] -> 5;<br />

[ 0 , 1, 0 , 0 ] -> Z;<br />

[ Ck , 0, 1 , 0 ] -> 0;<br />

test_vectors 'preload to illegal states'<br />

( [Clk ,OE, Clr,[Q2,Q1,Q0]] -> [Q2,Q1,Q0])<br />

"durch diese spezielle Anordnung können illegale Zustände simuliert werden.<br />

[ P , 1, 0 , !6 ] -> X;<br />

[ 0 , 0, 0 , X ] -> 6;<br />

[ Ck , 0, 0 , X ] -> 0;<br />

[ P , 1, 0 , !7 ] -> X;<br />

[ 0 , 0, 0 , X ] -> 7;<br />

[ Ck , 0, 0 , X ] -> 0;<br />

end<br />

Aufgaben<br />

1) Erweitern Sie den 3 bit Vorwärtszähler zu e<strong>in</strong>em 10 Bit Vorwärtszähler. Achten Sie auf richtige P<strong>in</strong>wahl -<br />

es könnte sich sonst <strong>mit</strong> den Produkttermen nicht ausgehen.<br />

2) Erweitern Sie das Schieberegister zu e<strong>in</strong>em 8 Bit Schieberegister <strong>mit</strong> parallelem Load.<br />

3) Erweitern Sie den 10Bit Zähler auch Aufgabe 1 zu e<strong>in</strong>em 10Bit Vorwärts/Rückwärts Zähler.<br />

4) Entwerfen Sie e<strong>in</strong> synchrones 4 Bit Schieberegister <strong>mit</strong> rechts- und l<strong>in</strong>ksschieben und parallelem load und<br />

Möglichkeit zur Kaskadierung.<br />

5) Entwerfen Sie e<strong>in</strong>e Schaltung (Handskizze) <strong>mit</strong> <strong>PLD</strong> GAL22V10 welche die Ausgabe e<strong>in</strong>es 8 Bit parallel<br />

A/D Wandlers <strong>in</strong> e<strong>in</strong> RS232 Signal konvertiert. Der dafür notwendige Takt ist vorhanden. E<strong>in</strong>e<br />

Pegelanpassung an RS232 Norm ist zu realisieren. Erstellen Sie auch die notwendigen<br />

Programmierunterlagen für die <strong>PLD</strong>'s.<br />

Beachten Sie, daß manche A/D Wandler e<strong>in</strong> "Start Conversion Signal" benötigen.