You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

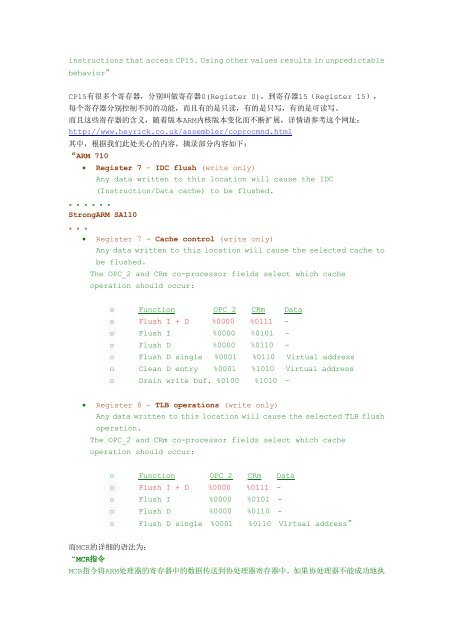

instructions that access CP15. Using other values results in unpredictable<br />

behavior”<br />

CP15有很多个寄存器,分别叫做寄存器0(Register 0),到寄存器15(Register 15),<br />

每个寄存器分别控制不同的功能,而且有的是只读,有的是只写,有的是可读写。<br />

而且这些寄存器的含义,随着版本ARM内核版本变化而不断扩展,详情请参考这个网址:<br />

http://www.heyrick.co.uk/assembler/coprocmnd.html<br />

其中,根据我们此处关心的内容,摘录部分内容如下:<br />

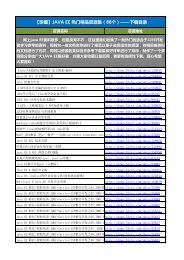

“ARM 710<br />

Register 7 - IDC flush (write only)<br />

。。。。。。<br />

Any data written to this location will cause the IDC<br />

(Instruction/Data cache) to be flushed.<br />

StrongARM SA110<br />

。。。<br />

Register 7 - Cache control (write only)<br />

Any data written to this location will cause the selected cache to<br />

be flushed.<br />

The OPC_2 and CRm co-processor fields select which cache<br />

operation should occur:<br />

o Function OPC_2 CRm Data<br />

o Flush I + D %0000 %0111 -<br />

o Flush I %0000 %0101 -<br />

o Flush D %0000 %0110 -<br />

o Flush D single %0001 %0110 Virtual address<br />

o Clean D entry %0001 %1010 Virtual address<br />

o Drain write buf. %0100 %1010 -<br />

Register 8 - TLB operations (write only)<br />

Any data written to this location will cause the selected TLB flush<br />

operation.<br />

The OPC_2 and CRm co-processor fields select which cache<br />

operation should occur:<br />

o Function OPC_2 CRm Data<br />

o Flush I + D %0000 %0111 -<br />

o Flush I %0000 %0101 -<br />

o Flush D %0000 %0110 -<br />

o Flush D single %0001 %0110 Virtual address”<br />

而MCR的详细的语法为:<br />

“MCR指令<br />

MCR指令将ARM处理器的寄存器中的数据传送到协处理器寄存器中。如果协处理器不能成功地执