You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

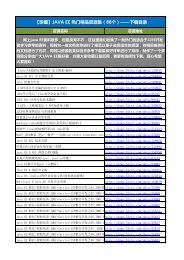

Table 2.10. Control register 1 bit functions<br />

Register<br />

bits<br />

31<br />

30<br />

图表 15 控制寄存器 1 的位域含义<br />

Name Function Value<br />

iA<br />

bit<br />

nF<br />

bit<br />

Asynchronous<br />

clock select<br />

29:15 - Reserved<br />

14<br />

RR<br />

bit<br />

13 V bit<br />

See Table 2.11.<br />

notFastBus select See Table 2.11.<br />

Round robin<br />

replacement<br />

Base location of<br />

exception<br />

registers<br />

12 I bit ICache enable<br />

11:10 - Reserved<br />

9 R bit ROM protection<br />

8 S bit System protection<br />

7 B bit Endianness<br />

6:3 - Reserved<br />

2 C bit DCache enable<br />

1 A bit<br />

Alignment fault<br />

enable<br />

Read = Unpredictable.<br />

Write = Should be zero.<br />

0 = Random replacement.<br />

1 = Round-robin replacement.<br />

0 = Low addresses = 0x00000000.<br />

1 = High addresses = 0xFFFF0000.<br />

0 = ICache disabled.<br />

1 = ICache enabled.<br />

Read = 00.<br />

Write = 00.<br />

This bit modifies the MMU protection<br />

system. See Domain access control.<br />

This bit modifies the MMU protection<br />

system. See Domain access control.<br />

0 = Little-endian operation.<br />

1 = Big-endian operation.<br />

Read = 1111.<br />

Write = 1111.<br />

0 = DCache disabled.<br />

1 = DCache enabled.<br />

Data address alignment fault<br />

checking.<br />

0 = Fault checking disabled.<br />

1 = Fault checking enabled.