Design of De-Emphasis and Equalization Circuits for Gigabit Serial ...

Design of De-Emphasis and Equalization Circuits for Gigabit Serial ...

Design of De-Emphasis and Equalization Circuits for Gigabit Serial ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Vss<br />

Vdd<br />

m=30<br />

w=1u<br />

l=10u<br />

ql<br />

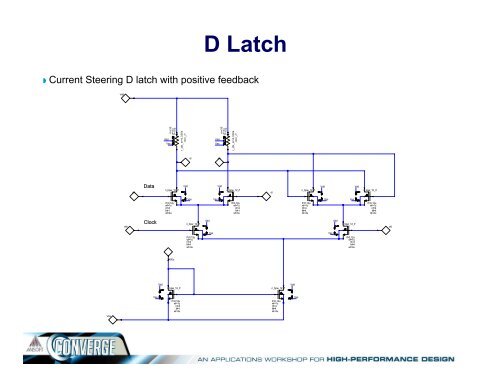

D Latch<br />

� Current Steering D latch with positive feedback<br />

Data<br />

Vdd<br />

Vdd<br />

dh<br />

n_bpw_12_rf<br />

n_bpw_12_rf<br />

dl<br />

Clock<br />

lf=0.12u<br />

wf=1u<br />

nf=4<br />

M=1<br />

wt=4u<br />

qh<br />

Vdd<br />

Vdd<br />

ckh<br />

n_bpw_12_rf<br />

n_bpw_12_rf<br />

ckl<br />

Vss<br />

Vdd<br />

i400u<br />

n_bpw_12_rf<br />

r_zbt_m=0.336k<br />

rnhr_rf<br />

Vdd Vdd<br />

Vss Vss<br />

lf=0.12u<br />

wf=1u<br />

nf=4<br />

M=1<br />

wt=4u<br />

Vss Vss<br />

lf=0.12u<br />

wf=1u<br />

nf=4<br />

M=4<br />

wt=4u<br />

Vss<br />

m=30<br />

w=1u<br />

l=10u<br />

r_zbt_m=0.336k<br />

rnhr_rf<br />

lf=0.12u<br />

wf=1u<br />

nf=4<br />

M=1<br />

wt=4u<br />

n_bpw_12_rf<br />

lf=0.12u<br />

wf=1u<br />

nf=4<br />

M=4<br />

wt=4u<br />

Vdd<br />

Vss<br />

n_bpw_12_rf<br />

lf=0.12u<br />

wf=1u<br />

nf=4<br />

M=4<br />

wt=4u<br />

Vdd<br />

Vss<br />

Vss<br />

Vss<br />

Vdd<br />

lf=0.12u<br />

wf=1u<br />

nf=4<br />

M=4<br />

wt=4u<br />

n_bpw_12_rf<br />

lf=0.12u<br />

wf=1u<br />

nf=4<br />

M=4<br />

wt=4u