Bluespec-6 Simple Pipelined Processor Instruction set - MIT

Bluespec-6 Simple Pipelined Processor Instruction set - MIT

Bluespec-6 Simple Pipelined Processor Instruction set - MIT

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

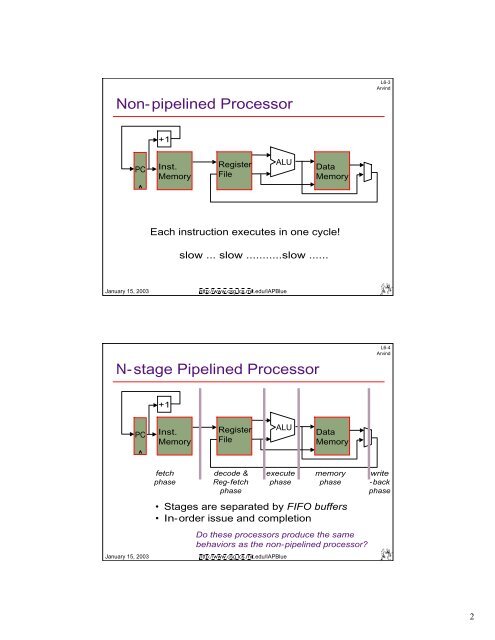

Non-pipelined <strong>Processor</strong><br />

PC<br />

+1<br />

Inst.<br />

Memory<br />

Register<br />

File<br />

ALU<br />

January 15, 2003 http://www.csg.lcs.mit.edu/IAPBlue<br />

Data<br />

Memory<br />

Each instruction executes in one cycle!<br />

slow ... slow ...........slow ......<br />

N-stage <strong>Pipelined</strong> <strong>Processor</strong><br />

PC<br />

+1<br />

Inst.<br />

Memory<br />

fetch<br />

phase<br />

Register<br />

File<br />

decode &<br />

Reg-fetch<br />

phase<br />

ALU<br />

execute<br />

phase<br />

Do these processors produce the same<br />

behaviors as the non-pipelined processor?<br />

January 15, 2003 http://www.csg.lcs.mit.edu/IAPBlue<br />

Data<br />

Memory<br />

memory<br />

phase<br />

• Stages are separated by FIFO buffers<br />

• In-order issue and completion<br />

L6-3<br />

Arvind<br />

L6-4<br />

Arvind<br />

write<br />

-back<br />

phase<br />

2