Power Management - 6-Channel DMX Dimmer - AN2302 - Farnell

Power Management - 6-Channel DMX Dimmer - AN2302 - Farnell

Power Management - 6-Channel DMX Dimmer - AN2302 - Farnell

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

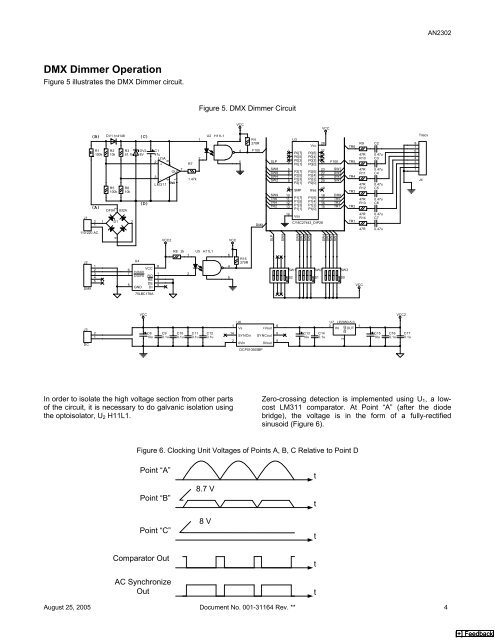

<strong>DMX</strong> <strong>Dimmer</strong> Operation<br />

Figure 5 illustrates the <strong>DMX</strong> <strong>Dimmer</strong> circuit.<br />

J1<br />

J2<br />

<strong>DMX</strong><br />

J3<br />

DC<br />

(B)<br />

R1<br />

100k<br />

(A)<br />

2<br />

1<br />

110-220 AC<br />

1<br />

2<br />

3<br />

4<br />

5<br />

2<br />

1<br />

1<br />

DV1 1n4148<br />

R2<br />

10k<br />

R5<br />

100k<br />

DF04 832A<br />

3<br />

4 - +<br />

D1<br />

R3<br />

51.1k<br />

R6<br />

10k<br />

2<br />

(C)<br />

DV2<br />

8V<br />

(D)<br />

VCC 8<br />

RO 1<br />

RE 2<br />

DE 3<br />

6<br />

7<br />

5<br />

U4<br />

DO/RI<br />

DO/RI<br />

GND DI<br />

75LBC176A<br />

4<br />

VCC<br />

C8<br />

10u<br />

C1<br />

47u<br />

2<br />

+<br />

OUT<br />

3<br />

-<br />

V-<br />

7<br />

U1A<br />

Gnd<br />

LM311<br />

V+ 8<br />

4<br />

1<br />

VCC2<br />

C9<br />

0.1u<br />

R8 2k<br />

1<br />

C10<br />

0.1u<br />

2<br />

C11<br />

0.1u<br />

Figure 5. <strong>DMX</strong> <strong>Dimmer</strong> Circuit<br />

1<br />

2<br />

U5 H11L1<br />

U2 H11L1<br />

C12<br />

0.1u<br />

In order to isolate the high voltage section from other parts<br />

of the circuit, it is necessary to do galvanic isolation using<br />

the optoisolator, U2 H11L1.<br />

R7<br />

1.47k<br />

6<br />

4<br />

5<br />

VCC<br />

VCC<br />

6<br />

4<br />

5<br />

R15<br />

270R<br />

<strong>AN2302</strong><br />

August 25, 2005 Document No. 001-31164 Rev. ** 4<br />

R4<br />

270R<br />

F100<br />

<strong>DMX</strong><br />

1<br />

U6<br />

Vs<br />

+Vout<br />

6<br />

14<br />

SYNCin SYNCout<br />

8<br />

2<br />

0Vin<br />

0Vout<br />

5<br />

DCP010505BP<br />

SW1<br />

S2<br />

C13<br />

10u<br />

SW2<br />

S1<br />

VCC<br />

U3<br />

Vcc<br />

28<br />

TR6<br />

R9 C2<br />

SLP<br />

1<br />

2<br />

3<br />

4<br />

P0[7]<br />

P0[5]<br />

P0[3]<br />

P0[1]<br />

P0[6]<br />

P0[4]<br />

P0[2]<br />

P0[0]<br />

27<br />

26<br />

25<br />

24 F100 TR5<br />

47R<br />

R10<br />

0.47u<br />

C3<br />

SW8<br />

SW6<br />

SW4<br />

SW2<br />

5<br />

6<br />

7<br />

8<br />

P2[7]<br />

P2[5]<br />

P2[3]<br />

P2[1]<br />

P2[6]<br />

P2[4]<br />

P2[2]<br />

P2[0]<br />

23<br />

22<br />

21<br />

20<br />

SW7<br />

SW5<br />

SW3<br />

SW1<br />

TR4<br />

47R<br />

R11<br />

47R<br />

0.47u<br />

C4<br />

0.47u<br />

9<br />

SMP Xres<br />

19<br />

TR3<br />

R12 C5<br />

SW9<br />

TR6<br />

TR4<br />

TR2<br />

10<br />

11<br />

12<br />

13<br />

P1[7]<br />

P1[5]<br />

P1[3]<br />

P1[1]<br />

P1[6]<br />

P1[4]<br />

P1[2]<br />

P1[0]<br />

18<br />

17<br />

16<br />

15<br />

<strong>DMX</strong><br />

TR5<br />

TR3<br />

TR1 TR2<br />

47R<br />

R13<br />

0.47u<br />

C6<br />

14<br />

Vss<br />

CY8C27443_DIP28<br />

TR1<br />

47R<br />

R14<br />

0.47u<br />

C7<br />

SLP<br />

SW9<br />

SW8<br />

SW7<br />

SW6<br />

SW5<br />

SW4<br />

SW3<br />

SW2<br />

SW1<br />

C14<br />

0.1u<br />

SW3<br />

S0<br />

47R<br />

VCC<br />

U7 LP2950-5.0<br />

3<br />

IN OUT<br />

1<br />

GND<br />

2<br />

0.47u<br />

C15<br />

10u<br />

C16<br />

0.1u<br />

VCC2<br />

C17<br />

0.1u<br />

Zero-crossing detection is implemented using U1, a lowcost<br />

LM311 comparator. At Point “A” (after the diode<br />

bridge), the voltage is in the form of a fully-rectified<br />

sinusoid (Figure 6).<br />

Figure 6. Clocking Unit Voltages of Points A, B, C Relative to Point D<br />

Point “A”<br />

Point “B”<br />

Point “C”<br />

Comparator Out<br />

8.7 V<br />

8 V<br />

AC Synchronize<br />

Out t<br />

t<br />

t<br />

t<br />

t<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

Triacs<br />

J4<br />

[+] Feedback

![Microchip Signal Chain Design Guide [pdf] - Farnell](https://img.yumpu.com/19262401/1/190x245/microchip-signal-chain-design-guide-pdf-farnell.jpg?quality=85)