DDR4 Design Considerations - EEWeb

DDR4 Design Considerations - EEWeb

DDR4 Design Considerations - EEWeb

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Dan Kinzer<br />

CTO of Fairchild<br />

Analysis of TDC Converters—Pt. 2<br />

<strong>DDR4</strong> <strong>Design</strong><br />

<strong>Considerations</strong><br />

SL Series by<br />

Magna-Power<br />

Electrical Engineering Community<br />

EEweb.com

<strong>EEWeb</strong> PULSE TABLE OF CONTENTS<br />

Dan Kinzer<br />

CTO OF FAIRCHILD SEMICONDUCTOR<br />

A conversation about the company credited with starting the Information Age.<br />

Featured Products<br />

SL Series by Magna-Power: Pushing the Limits<br />

of Programmable Power<br />

How Magna-Power’s unique approach to manufacturing yields a diverse line of programmable<br />

DC power supplies.<br />

<strong>DDR4</strong> <strong>Design</strong> <strong>Considerations</strong><br />

BY MIKE MICHELETTI WITH TELEDYNE LECROY<br />

Why more double data rate (DDR) developers are targeting <strong>DDR4</strong> technology for a variety of<br />

applications—from high density blade servers to high performance workstations.<br />

<strong>Design</strong> & Analysis of TDC Converter<br />

Architectures - Part 2<br />

BY UMANATH KAMATH WITH CYPRESS<br />

This installment goes through the transistor-level implementation of a TDC in an 80nm process.<br />

RTZ - Return to Zero Comic<br />

Visit www.eeweb.com<br />

4<br />

11<br />

14<br />

20<br />

26<br />

36<br />

3

<strong>EEWeb</strong> PULSE INTERVIEW<br />

4 <strong>EEWeb</strong> | Electrical Engineering Community<br />

Visit www.eeweb.com<br />

5

<strong>EEWeb</strong> PULSE INTERVIEW<br />

How did you get into<br />

engineering?<br />

I always loved math and science, even<br />

as a young boy. I applied to several<br />

of the top science and engineering<br />

schools, because I wanted to be<br />

involved in something related to<br />

science. I chose engineering at<br />

Princeton over CalTech and MIT, and<br />

I joined the Department of Aerospace<br />

and Mechanical Sciences. In that<br />

department, I studied a large variety<br />

of engineering and science courses,<br />

and found them all very interesting. I<br />

took a program in engineering physics<br />

because I found physics especially<br />

fascinating. It is so fundamental to<br />

understanding the way the universe<br />

operates. That actually led me into<br />

solid-state technology and eventually<br />

into power semiconductors.<br />

In 1978, I joined International Rectifier,<br />

which was my first permanent<br />

position, and worked on the<br />

development of their first family of<br />

power MOSFETs. From there I moved<br />

into solid-state optocoupled relays<br />

and high-voltage and high-power ICs,<br />

where I was involved in process and<br />

From there I came to Fairchild, where<br />

I was able to continue to work in<br />

the power area with a world-class<br />

company. I was also able to get<br />

involved with the mobile business and<br />

began working with the technology<br />

development team to improve the<br />

integrated circuit processes. Since<br />

I’ve been here at Fairchild, I’ve put a<br />

lot of focus on improving the power<br />

device technology across the range<br />

of power and high-density power<br />

packages and modules.<br />

Could you give us a little<br />

history of Fairchild?<br />

Fairchild’s history goes back to 1957.<br />

Many credit the origins of Silicon<br />

Valley to the founders of Fairchild.<br />

Many believe that Robert Noyce’s<br />

silicon integrated circuit launched<br />

the Information Age. From our origins<br />

until now, we continue to be thought<br />

of as leaders and innovators in the<br />

industry.<br />

From the original Fairchild, our<br />

leadership spun-off into other<br />

companies, including National<br />

“Our IP is inside virtually<br />

every smart phone in the<br />

world, and we ship more than<br />

3 billion units per year to<br />

handset and tablet OEMs.”<br />

technology development as well as<br />

product design. In addition to power<br />

devices, I was spending a lot of time<br />

creating package technologies and<br />

IC designs. I eventually became the<br />

Vice President of R&D at International<br />

Rectifier and held that position from<br />

1989 until 2007.<br />

Semiconductor, Intel, AMD, LSI<br />

Logic and many others. In the<br />

1980’s, Fairchild was acquired by<br />

Schlumberger, and then National in<br />

the early 1990s. Then, in 1997, Fairchild<br />

was spun back out from National as<br />

a stand-alone brand and company.<br />

At that time, Fairchild’s offerings<br />

included the rapidly growing power<br />

MOSFET business, standard logic,<br />

standard linear, analog switches, and<br />

a variety of other analog and discrete<br />

product lines.<br />

The re-formed company went on to<br />

acquire the power semiconductor<br />

businesses of Harris and Samsung,<br />

which added factory locations in<br />

Pennsylvania and Korea. This brought<br />

high voltage power discretes and<br />

high voltage analog ICs, as well as<br />

automotive products into the portfolio.<br />

Fairchild has its headquarters<br />

in San Jose, a major IC fab and<br />

administrative office in Portland,<br />

Maine, with other fab locations in<br />

Pennsylvania, Utah, and South Korea.<br />

Our internal assembly sites are in<br />

China, Malaysia and the Philippines.<br />

In addition, we have several major<br />

wafer fab foundry and assembly<br />

subcontractor relationships. Our<br />

factory in Suzhou, China is a worldclass<br />

power packaging and power<br />

module manufacturing center. We<br />

continue to push the state of the art in<br />

power and mobile applications and<br />

technologies.<br />

What are of some of Fairchild’s<br />

main products?<br />

In broad terms, our offerings fall<br />

into two main categories - power<br />

semiconductor solutions and mobile<br />

semiconductor solutions. In mobile,<br />

Fairchild is a mobile technology leader,<br />

offering an unmatched portfolio of<br />

analog and power technologies<br />

in both standard and customized<br />

semiconductor products for mobile<br />

applications. These include ICs that<br />

offer combinations of analog switches,<br />

load sensing, power management,<br />

audio, lighting, communication, and<br />

sensors, among other functions.<br />

Our IP is inside virtually every smart<br />

phone in the world, and we ship more<br />

than 3 billion units per year to handset<br />

and tablet OEMs. We are also adding<br />

MEMS inertial sensors to our portfolio<br />

of mobile offerings.<br />

In our power portfolio, we have<br />

devices that start at about 12-volts<br />

and go to about 1400-volts. This<br />

includes one of the main families, our<br />

PowerTrench(R) MOSFETs, which<br />

are lower voltage devices in the under<br />

200-volt range. We have a MOSFET<br />

technology that few other companies<br />

have, called shielded-gate technology,<br />

which greatly improves the power<br />

density, switching performance, and<br />

efficiency of trench power MOSFETs.<br />

That’s definitely an area of a lot of<br />

interest. In higher voltage areas, we<br />

have a strong lineup of super junction<br />

MOSFETs in the 600-650V range.<br />

In addition, we have some leading<br />

technologies in AC to DC converters<br />

up to 1 kilowatt, and motor drives<br />

up to 5 kilowatts. For higher power<br />

levels, we have our IGBTs. We’ve got<br />

a variety of technologies there—our<br />

latest technology is called field stop<br />

technology. We have leading edge<br />

performance in 600- to 1200-volt<br />

IGBTs for motor drives, renewable<br />

energy, and industrial and automotive<br />

power train applications.<br />

We are a leading supplier of power<br />

modules that use direct bonded<br />

copper on ceramic and transfer<br />

molded packaging technology. This<br />

technology allows us to manufacture<br />

SPM® smart power modules that<br />

include drive, sense, and protection<br />

features as well as power—with<br />

highly robust cycling performance<br />

and excellent thermal characteristics.<br />

Recently, we announced our newest<br />

technology, silicon carbide. Silicon<br />

carbide technology will be part of the<br />

next generation of power systems,<br />

allowing more power in less space<br />

and the ability to deliver more<br />

performance per unit cost.<br />

For more than 50 years Fairchild<br />

Semiconductor has focused on<br />

“Our largest core mission<br />

concerning energy efficiency<br />

is something that we get very<br />

excited about and we value<br />

the contribution that makes<br />

to society in general.”<br />

customer success. Our commitment<br />

to their success drives us to design,<br />

manufacture, and supply power and<br />

mobile semiconductor technologies<br />

to make home appliances more<br />

energy efficient, enable mobile<br />

device manufacturers to deliver<br />

innovative new features, and boost<br />

the efficiency of industrial products.<br />

Our semiconductor solutions for<br />

automotive, mobile, LED lighting,<br />

and power management applications<br />

help our customers achieve success<br />

every day.<br />

What kinds of products are<br />

you targeting for your silicon<br />

carbide technology?<br />

The device that we led with is a 1200volt<br />

bipolar transistor. We selected<br />

the bipolar transistor to start with<br />

because it has the lowest conduction<br />

loss of any technology, so we can<br />

get the most current out of a given<br />

chip size. It switches extremely<br />

fast—as fast as any device currently<br />

can—so it can also operate at a<br />

relatively high frequency for highpower<br />

applications. Normally, these<br />

applications may run at 5 or 10 KHz,<br />

but with these silicon carbide bipolar<br />

transistors, we can actually take that<br />

up to 30, 40, 50, even 100 KHz in some<br />

applications. We will offer diodes that<br />

complement these transistors, and<br />

we package them in plastic, high<br />

temperature discrete, and power<br />

module packages.<br />

Is there additional drive<br />

circuitry required to implement<br />

this new technology?<br />

Yes. Most designers are not used to<br />

driving bipolar transistors because<br />

they require an input current. One<br />

of the good things about this silicon<br />

carbide technology, compared to<br />

what people remember in silicon<br />

bipolar technology, is that the current<br />

gain is very high, so you don’t have to<br />

put that much current into the base<br />

to get what you want out—the gains<br />

are in the range of 100, typically. The<br />

power loss is not a very big factor—<br />

it’s about a tenth of a percent of the<br />

output power. People do need to<br />

remember how to drive the base of<br />

a power transistor because many are<br />

used to drive MOSFETs and IGBTs,<br />

which are voltage-controlled.<br />

Do you have app notes<br />

or other resources to help<br />

engineers who aren’t familiar<br />

with using these transistors?<br />

Specific to silicon carbide technology,<br />

we have resources from applications<br />

notes, reference designs, evaluation<br />

boards and starter kits, to field<br />

6 <strong>EEWeb</strong> | Electrical Engineering Community<br />

Visit www.eeweb.com<br />

7

<strong>EEWeb</strong> PULSE INTERVIEW<br />

application engineers who are<br />

available to work with our customers.<br />

In high-power applications, a lot of<br />

people use pretty powerful bipolar<br />

power supplies in driving IGBTs.<br />

Those same supplies can be used<br />

in driving the BJT with a specialized<br />

drive circuit. We are also working on a<br />

specially optimized integrated circuit<br />

for driving these devices as well.<br />

What are some of the other<br />

design tools and resources<br />

Fairchild offers?<br />

Fairchild’s design support extends<br />

to all our product lines, not just the<br />

new silicon carbide technology.<br />

First, our application engineers<br />

are available to customers, both in<br />

the factory and field. We have an<br />

online design center that is part of<br />

our Global Power ResourceSM - a<br />

worldwide network of power design<br />

centers, power seminars, and a suite<br />

of online design and educational<br />

tools to help designers solve their<br />

design challenges and speed timeto-market.<br />

We are well known for our<br />

travelling Fairchild Power Seminar<br />

series which brings design support<br />

right to the customer. Our application<br />

notes and product usage guides are<br />

available online. You can also easily<br />

get samples through our on-line<br />

sample program. We also have online<br />

design tools as well that you can use<br />

for some power supply applications.<br />

Could you tell us a little about<br />

your super junction devices?<br />

Fairchild’s super junction MOSFETs<br />

range from resistances of around 40<br />

milliohms up to a couple of ohms<br />

and currents in the 5- to 75-amp<br />

range. We also have both 600- and<br />

650-volt devices, as well as devices<br />

optimized for fast recovery of the<br />

internal diode, and fast recovery-type<br />

devices in different speeds. We have<br />

versions that are optimized for the<br />

fastest possible switching, therefore<br />

highest efficiency, and others that are<br />

optimized to be a little easier to drive<br />

with a little bit slower transitions and<br />

less EMI.<br />

People can choose which kinds of<br />

devices they want out of those families.<br />

We’re also perhaps the only company<br />

that offers two main types—in both<br />

cases, you have super junctions that<br />

consist of p- and n-type columns<br />

arranged in alternating fashion to<br />

form the high voltage blocking layer.<br />

There are different ways to form that.<br />

One of those ways is a deep trench<br />

etching and refill and the other way<br />

is with multiple p-type buried layers<br />

stacked up on each other, which is a<br />

more conventional approach.<br />

What are some of the<br />

exciting developments<br />

you are working on in the<br />

upcoming year?<br />

Fairchild is always innovating and<br />

developing next generation solutions<br />

that will help our customers succeed.<br />

We see the three megatrends being<br />

energy, mobility, and the cloud. We<br />

want to be leaders in all these areas.<br />

In mobile, our products are in virtually<br />

every smart phone device. We’re in<br />

battery charging circuits, we’re in<br />

core power, we’re in powering RF<br />

amplifiers, we’re in USB ports, audio,<br />

and many more. We’re developing<br />

MEMS for inertial sensing as well.<br />

We’re very excited about all these<br />

contributions we’re making in<br />

handheld devices.<br />

In the past year or two, my focus<br />

has been on system-wide energy<br />

efficiency, from the smart-grid and<br />

renewable energy to distributed<br />

power and point of load converters.<br />

The things we are doing in that space<br />

are helping across the board. We are<br />

also closely following the growth of<br />

hybrid vehicles. Our automotive<br />

business is focused on power train<br />

applications, so we have a strong<br />

position in ignition and steering and<br />

we also deliver automotive power<br />

modules. We’re looking at ways to<br />

use our technology to help make cars<br />

more efficient—hybrid and electric<br />

cars as well as conventional cars.<br />

How would you describe the<br />

culture at Fairchild?<br />

Innovative. Steeped in history yet<br />

providing next generation solutions;<br />

innovation that will help our customers.<br />

I would say, as a company, we are<br />

very committed and care deeply<br />

about what we do. We have a strong<br />

desire to excel, both technically and<br />

financially, and we care a lot about our<br />

people. That includes our employees<br />

and our customers.<br />

We are a highly collaborative company<br />

and we are very focused on<br />

meeting the needs of our customers<br />

and offering them great value in<br />

the products that we sell them. We<br />

are also very multicultural—we have<br />

employees from every corner of the<br />

world and locations all over the world.<br />

The interaction leads to diverse thinking,<br />

which we also value very highly.<br />

We value that because innovation and<br />

creativity are very important to us.<br />

Fairchild is a leader in our industry<br />

and our goal is to remain a leader.<br />

Everyone at Fairchild is committed<br />

to the highest ethical standards and<br />

environmentally responsible behavior.<br />

Our largest core mission concerning<br />

energy efficiency is something that we<br />

get very excited about, and we value<br />

the contribution that makes to society<br />

in general. ■<br />

Online Circuit<br />

Simulator<br />

PartSim includes a full SPICE<br />

simulation engine, web-based<br />

schematic capture tool, and a<br />

graphical waveform viewer.<br />

Some Features include:<br />

• Simulate in a standard Web Browser<br />

• AC/DC and Transient Simulations<br />

• Schematic Editor<br />

• WaveForm Viewer<br />

• Easily Share Simulations<br />

Try-it Now!<br />

www.partsim.com<br />

8 <strong>EEWeb</strong> | Electrical Engineering Community<br />

Visit www.eeweb.com<br />

9

<strong>EEWeb</strong> FEATURED PULSE PRODUCTS<br />

FEATURED INTERVIEW PRODUCTS<br />

Technology You Can Trust<br />

Avago Technologies Optocouplers<br />

A Superior Technology<br />

for High Voltage Protection!<br />

IEC 60747-5-5 Certifi ed<br />

Optocouplers are the only isolation devices that meet or exceed the IEC 60747-5-5<br />

International Safety Standard for insulation and isolation. Stringent evaluation tests show Avago’s<br />

optocouplers deliver outstanding performance on essential safety and deliver exceptional High Voltage protection<br />

for your equipment. Alternative isolation technologies such as ADI’s magnetic or TI’s capacitive isolators do not deliver<br />

anywhere near the high voltage insulation protection or noise isolation capabilities that optocouplers deliver.<br />

For more details on this subject, read our white paper at: www.avagoresponsecenter.com/672<br />

VoLTE Capabilities for Smart Phones<br />

Renesas Mobile Corporation, announced the completion of the integration<br />

of the Voice over LTE (VoLTE) capabilities for Renesas Mobile’s<br />

communication processor and slim modem platforms for LTE smart<br />

phones. Ecrio’s FlexIMS based VoLTE Client Software is now integrated<br />

and optimised in the MP5232 and SP2532 multi-mode LTE platforms<br />

paving the way for the broad supply of VoLTE Services based on the 3GPP<br />

IP Multimedia Subsystem (IMS). Renesas Mobile will be demonstrating<br />

VoLTE capabilities on the MP5232 platform at Mobile World Congress<br />

2013 in Barcelona on both TD-LTE and FDD-LTE systems. For more<br />

information, please click here.<br />

Single and Dual Low-Power CMOS Amplifiers<br />

The LMV601/LMV602/LMV604 are single, dual, and quad low voltage, low<br />

power Operational Amplifiers. They are designed specifically for low voltage<br />

general purpose applications. Other important product characteristics are<br />

low input bias current, rail-to-rail output, and wide temperature range.<br />

The LMV601/LMV602/LMV604 have 29nV Voltage Noise at 10KHz, 1MHz<br />

GBW, 1.0V/μs Slew Rate, 0.25mV Vos. The LMV601/2/4 operates from a<br />

single supply voltage as low as 2.7V, while drawing 100uA (typ) quiescent<br />

current. In shutdown mode the current can be reduced to 45pA. The<br />

industrial-plus temperature range of −40°C to 125°C allows the LMV601/<br />

LMV602/LMV604 to accommodate a broad range of extended environment<br />

applications. For more information, click here.<br />

DAB Receiver Enables SDR<br />

Maxim Integrated Products, Inc. (NASDAQ: MXIM) today announced<br />

the MAX2173 RF to Bits® tuner for digital audio broadcast (DAB)<br />

applications in automobiles and other mobile DAB/FM products. The<br />

industry’s first RF to Bits DAB/FM tuner integrates a radio tuner, analogto-digital<br />

converter (ADC), and digital filtering, and uses a digital I2S<br />

output to interface directly to digital signal processors (DSPs). RF to Bits<br />

radios will enable system designers to implement baseband processing<br />

using off-the-shelf DSPs. This level of integration eliminates numerous<br />

external components associated with traditional RF tuners to reduce<br />

cost, BOM count, and space. For more information, please click here.<br />

High Density Thyristor Module Platform<br />

IXYS Corporation announced a new bipolar module platform for high<br />

power applications. The new ComPack family represents a compact<br />

package with the highest power density. The ComPack design is<br />

resulting from the implementation of the newest assembly methods in<br />

combination with the proprietary ‘power metallization chip’ technologies<br />

of IXYS. Advancement in the module design as well as the silicon die<br />

technology leads to a userfriendly product that fulfills the highest needs<br />

in reliability and functionality. The modules have a rated current of<br />

600 Amperes per leg, improved surge rating and a maximum junction<br />

temperature of 140 Deg C. For more information, please click here.<br />

10 <strong>EEWeb</strong> | Electrical Engineering Community<br />

Visit www.eeweb.com<br />

11

<strong>EEWeb</strong> FEATURED PULSE PRODUCTS<br />

FEATURED INTERVIEW PRODUCTS<br />

Fiber Optic Receiver for 50 MBaud MOST<br />

AFBR-2013 Receiver are designed to receive up to 25MBit/s optical data<br />

which are biphase coded (up to 50Mbaud). They are packaged in 4-pin<br />

transfer molded, low-cost packages ready for assembly into MOST®<br />

plastic fiber optic connector receptacles. Output data has TTL switching<br />

levels, compatible with MOST® Network Interface Controller ICs. These<br />

optical components are specified for operation over a -40°C to +95°C<br />

temperature range, and reliability requirements of automotive applications.<br />

It is allowed to process the AFBR-2013 devices with reflow soldering. In<br />

the absence of data activity, the receiver switches to very low power mode.<br />

For more information, please click here.<br />

2G/3G/4G Multiband LTE Transceiver Chip<br />

Fujitsu Semiconductor Wireless Products, Inc. (FSWP) today announced<br />

that its second LTE multimode product, the MB86L11 2G/3G/4G transceiver,<br />

is shipping in commercial quantities. The MB86L11 is a single chip<br />

multiband, multimode transceiver that supports all wireless communication<br />

modes including LTE (FDD & TDD), HSPA+, DC-HSPA, WCDMA, GSM,<br />

EDGE, CDMA and TD-SCDMA. The MB86L11 transceiver incorporates<br />

many advanced features, including envelope tracking (ET) and antenna<br />

tuning (AT). For more information, please click here.<br />

14.2W/in3 Power Density in T8 LED Driver<br />

Power Integrations announced two new reference designs describing<br />

high-efficiency, non-isolated, high-power-factor (PF) LED drivers for T8<br />

tubes. The designs feature low component count and leverage simple<br />

magnetics and single-sided boards yielding industry-leading power<br />

densities of 14.2 W/in³. Based on the LNK460KG LED driver from Power<br />

Integrations’ LinkSwitch-PL family of ICs, the circuits detailed in DER-<br />

337 (high-line) and DER-345 (low-line) use single-stage non-isolated<br />

topologies which result in a profile of only 8 mm – small enough to be<br />

mounted behind the LEDs in the T8 tube. T8-tube reference designs<br />

describing high-efficiency, non-isolated, high-power-factor (PF) LED<br />

drivers. For more information, please click here.<br />

Wireless Power Transmitters<br />

Integrated Device Technology, Inc. announced the industry’s most<br />

integrated wireless power transmitter solutions optimized for the Wireless<br />

Power Consortium (WPC) Tx-A5, Tx-A6, and Tx-A11 configurations. The<br />

new products expand IDT’s portfolio of WPC Qi-compliant magnetic<br />

induction transmitters with solutions optimized for single-coil 5 V and<br />

three-coil 12 V applications. The IDTP9035 and IDTP9036 are highefficiency,<br />

feature-rich wireless power transmitters. The IDTP9035 is<br />

designed to meet the requirements of the WPC Tx-A5 and Tx-A11 (5<br />

V) specifications, while the IDTP9036 is designed to meet the WPC<br />

Tx-A6 (12 V) specification. The IDTP9035 is optimized for a single-coil<br />

configuration with a standard 5V supply input, allowing customers to<br />

reduce their bill-of-materials (BOM) with cost-effective, low-voltage<br />

power adaptors. For more information, please click here.<br />

World’s lowest power capacitive<br />

sensors with auto-calibration<br />

NXP is a leader in low power capacitance touch sensors, which work based<br />

on the fact that the human body can serve as one of the capacitive plates in<br />

parallel to the second plate, connected to the input of the NXP capacitive<br />

sensor device.<br />

Thanks to a patented auto-calibration technology, the capacitive sensors<br />

can detect changes in capacitance and continually adjust to the environment.<br />

Things such as dirt, humidity, freezing temperatures, or damage to the<br />

electrode do not affect the device function.<br />

The rise of touch sensors in modern electronics has become a worldwide<br />

phenomenon, and with NXP’s low power capacitive sensors it’s never been<br />

easier to create the future.<br />

Learn more at: touch.interfacechips.com<br />

12 <strong>EEWeb</strong> | Electrical Engineering Community<br />

Visit www.eeweb.com<br />

13

<strong>EEWeb</strong> PULSE SPECIAL FEATURE<br />

Magna-Power<br />

SL Series by<br />

Pushing the Limits of Programmable Power<br />

Magna-Power Electronics<br />

has been providing power electronics solutions for over thirty years.<br />

The company was originally founded in 1981 and provided contract<br />

R&D for power electronics. Over the years, the company evolved into a<br />

product-based manufacturing company to where today, all of the R&D<br />

is geared towards new programmable power products. We spoke with<br />

Adam Pitel, the Director of Business Development at Magna-Power,<br />

about the company’s unique approach to manufacturing, its focus on<br />

vertical integration, and its diverse line of power supplies.<br />

14 <strong>EEWeb</strong> | Electrical Engineering Community<br />

Visit www.eeweb.com<br />

15

<strong>EEWeb</strong> PULSE SPECIAL FEATURE<br />

As the company has grown, Magna-Power has<br />

brought more and more processes in house for<br />

manufacturing power. “We believe that vertical<br />

integration allows us to not only maintain higher quality,”<br />

Pitel told us, “but also control lead times and also our<br />

costs involved.” One of the major things about these<br />

programmable power products is that they’re all<br />

configurable, meaning that they are built to order with<br />

the standard models also offered. “Today, at Magna-<br />

Power, we do all of our own transformer and inductor<br />

winding,” Pitel explained. “We have our own sheet metal<br />

operations, we do power coating, we manufacture our own<br />

heatsinks, we do PCB assemblies, we even manufacture<br />

our own magnetic cores for our transformers…” and the<br />

list goes on.<br />

SL Series<br />

The latest product from Magna-Power is the SL series<br />

product, which provides programmable DC power from<br />

1.5, 2.6, and 4 KW in a 1U package. The SL series is a<br />

power supply that pushes the density and power into<br />

a single 1U package. Pitel stated that, “Magna-Power<br />

has made a significant leap in the available 1U power<br />

density for programmable DC power supplies.” With<br />

Magna-Power’s growth, the company has broken into<br />

a market where there are a lot more applications with a<br />

significantly higher volume. “It’s really required us to scale<br />

up our resources and get to a point where we can build<br />

a 1U product and really make a splash,” Pitel explained.<br />

SL Specs<br />

The SL series has a variety of models that are all single<br />

output DC power supplies. There are 70 different models<br />

available with voltage ranges from 0 to 5 volts, up to 0 to<br />

1,000 volts. It also has a current range from 1.5 amps to 250<br />

amps, so there is a broad spectrum of different voltages<br />

and currents available. Just last year, Magna-Power<br />

introduced a high accuracy controller to provide highly<br />

accurate measurements for these supplies. Pitel recalled<br />

being on site with a client and his response to seeing<br />

external power meters taking all of their measurements;<br />

“I told them that they’re spending a small fortune on<br />

coupling power meters with every single power supply.”<br />

The client told Pitel that they were doing so because the<br />

accuracy from programmable DC power supplies just<br />

wasn’t high enough. Magna-Power responded directly to<br />

this problem. “In our latest generation of products,” Pitel<br />

told us, “we increased our programming accuracy nearly<br />

10-fold—it’s now +/- 0.075% for both voltage and current.”<br />

“In our latest generation of products,” Pitel told us, “we<br />

increased our programming accuracy nearly 10-fold.”<br />

Controlling the Device<br />

Every power supply from Magna-Power comes with three<br />

ways of programming it. One way is by using the front<br />

panel control knobs, which is for very basic operations.<br />

Another way is by using the 37 isolated analog and digital<br />

I/Os, so users can program it from an analog 10V signal<br />

and tie it in with a PLC. These supplies also come with<br />

a computer interface as well, which offers LXI-certified<br />

TCP/IP Ethernet and IEEE 488 GPIB. Recently, Magna-<br />

Power certified its products with the new LXI 1.4 standard,<br />

which supports the same mDNS standard that Apple<br />

made popular with Bonjour.<br />

If developers want to integrate controlling one of these<br />

devices into a customized software they have developed,<br />

Magna-Power also provides support for interfacing the<br />

programming languages. “We invested quite a bit into<br />

developing IVI drivers,” Pitel stated, “which is basically<br />

a universal driver that is supported in a wide variety of<br />

different programming environments.” These different<br />

environments include LabView, LabWindows, and Visual<br />

Studio, providing a full command set for the power supply.<br />

Users can access all of those commands in the power<br />

supply and any of these programming environments,<br />

which is made simple using the IVI driver.<br />

All of Magna-Power’s power supplies under 1,000 volts<br />

come with remote sense functionality, so users can hook<br />

up load wires and have a high impedance remote sense<br />

line to attach as well. Pitel told us that the leadless remote<br />

sense function is becoming very popular among their<br />

customers. “Consider an application where someone is<br />

powering an underwater vehicle and they have a 1,000foot<br />

cable powering it up, which can be pretty daunting.<br />

The nice thing is, you can have a 1,000-foot cable and<br />

have the impedance known through the leadless remote<br />

sense function.” Conveniently enough, if the user knows<br />

the impedance of the cable, they can compensate for that<br />

automatically within the power supply.<br />

Magna-Power’s various programmable power devices<br />

seem to directly respond to the customer’s needs. Whether<br />

it’s hearing about user’s problems from being on-site or by<br />

analyzing the current limitations of programmable power<br />

devices on the market today, Magna-Power pushes the<br />

limits of power devices so that they’re one step ahead<br />

of the rest. ■<br />

16 <strong>EEWeb</strong> | Electrical Engineering Community<br />

Visit www.eeweb.com<br />

17

Online Circuit Simulator<br />

PartSim includes a full SPICE simulation engine,<br />

web-based schematic capture tool, and a graphical<br />

waveform viewer.<br />

Some Features include:<br />

• Simulate in a standard Web Browser<br />

• AC/DC and Transient Simulations<br />

• Schematic Editor<br />

• WaveForm Viewer<br />

• Easily Share Simulations<br />

Our transformers are 100% final<br />

tested for quality.<br />

ZERO DEFECTS GUARANTEED<br />

Try-it Now!<br />

Prem Magnetics, Inc. Johnsburg, IL 60051 USA<br />

Call Us: 815-385-2700<br />

www.partsim.com<br />

Factory Direct Transformers<br />

18 Hour Express Delivery ¥ Buy Online<br />

DIRECT LINKS<br />

Power<br />

Switchmode<br />

Inductors<br />

Audio & Telephony<br />

High Speed Data<br />

Economy Audio<br />

Line Matching<br />

Instrument & Current<br />

CRT Display Magnetics<br />

<br />

<br />

<br />

<br />

<br />

Copyright 2013, Silicon Frameworks, LLC<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

PCBWeb.com

<strong>EEWeb</strong> PULSE TECH ARTICLE<br />

<strong>DDR4</strong> <strong>Design</strong> <strong>Considerations</strong><br />

<strong>DDR4</strong><br />

Mike Micheletti<br />

Product Manager<br />

Teledyne LeCroy<br />

represents a substantial upgrade to<br />

JEDEC’s dynamic random access memory<br />

(DRAM) standard, with numerous changes designed to<br />

lower power consumption while delivering higher<br />

density and bandwidth within the memory subsystem.<br />

DDR developers are targeting this new technology<br />

at a range of applications from high density blade<br />

servers, to high performance workstations and<br />

power-conscious mobile devices. Deploying general<br />

purpose memory in systems with specialized power<br />

and performance requirements means the designer<br />

must evaluate the cost and benefits of these new<br />

<strong>DDR4</strong> features within the context of the target<br />

application. New techniques for analyzing and<br />

testing DDR operation in a live systems will be<br />

essential to gain this visibility. Balancing the<br />

promise of faster memory IO with the goal of lower<br />

power consumption at the system level will require<br />

tuning of features, timing, and design.<br />

20 <strong>EEWeb</strong> | Electrical Engineering Community<br />

Visit www.eeweb.com<br />

21

<strong>EEWeb</strong> PULSE TECH ARTICLE<br />

<strong>DDR4</strong> is expected to deliver significantly higher<br />

performance, via faster data transfer rates reaching<br />

at least 3200 MT/s over time. In addition, the new<br />

specification introduces a number of enhancements used<br />

to improve both power efficiency and reliability. These<br />

features can add significant verification complexities for<br />

system designers, firmware developers and software<br />

designers. As one would expect, engineers are expected<br />

to march through the natural progression of the technology<br />

validation including signal integrity, timing analysis and<br />

specification compliance, performance tuning and power<br />

management modeling.<br />

This article explores methods to verify initial design and<br />

compliance with the new <strong>DDR4</strong> JEDEC specifications<br />

along with techniques used to take advantage of <strong>DDR4</strong><br />

features and maximize system performance. While<br />

there are many potential instruments that can be used,<br />

a new generation of dedicated DDR bus analyzers now<br />

provide comprehensive timing and protocol analysis,<br />

making them an important tool for accelerating <strong>DDR4</strong><br />

system validation and design. Substantially lower in<br />

cost than a logic analyzer, these systems can be used to<br />

qualify different memory DIMM components, as well as<br />

help sustain engineering groups as they verify system<br />

operations over the entire product life cycle.<br />

<strong>DDR4</strong> Technical Overview<br />

Table 1 provides a brief comparison between <strong>DDR4</strong> and<br />

DDR3 memory technology. <strong>DDR4</strong>, initially targeted for<br />

the server market, adopts a number of enhancements<br />

intended to deliver better performance, power-savings,<br />

and RAS (reliability, accessibility and serviceability)<br />

versus DDR3. These enhancements present unique<br />

and significant performance improvement and power<br />

reduction opportunities. Special attention must be taken<br />

when setting <strong>DDR4</strong> power savings parameters so that<br />

suitable performance levels are still achieved.<br />

<strong>DDR4</strong>’s new memory interface employs “pseudo-opendrain”<br />

(POD) termination where memory cells can store<br />

a logical 1 without consuming power. POD relies on<br />

switchable, on-die termination instead of a separate<br />

resistor pull up. Parallel-terminating the receiver at the<br />

far end means the <strong>DDR4</strong> DIMM only consumes power<br />

when the Vdd rail is pulled low to represent logical zero.<br />

The anticipated higher transfer rates in <strong>DDR4</strong> mandate<br />

tighter timing margins to support normal variations<br />

in memory DIMMs. <strong>DDR4</strong> also offers programmable<br />

Command-to-Address Latency that can be used to<br />

improve system power efficiency. Expanded role of<br />

MRS and the introduction of bank groups make memory<br />

controller designs more complex. These factors are<br />

expected to drive changes in memory controller designs<br />

and associated IP in order to support <strong>DDR4</strong>.<br />

Data transfer rates for <strong>DDR4</strong> and DDR3 should overlap<br />

for the foreseeable future, with <strong>DDR4</strong> delivering a longer<br />

performance runway. It is quite conceivable for a <strong>DDR4</strong><br />

platform to deliver moderate power savings versus a<br />

comparable DDR3 design, but potentially at the expense<br />

of lower memory bandwidth under certain <strong>DDR4</strong> operating<br />

parameters. System designers need to design highly<br />

tuned, balanced platforms that leverage the power saving<br />

and RAS enhancements of <strong>DDR4</strong>.<br />

Managing <strong>DDR4</strong> JEDEC Specifications<br />

The JEDEC specification targets specific timings for <strong>DDR4</strong><br />

memory controllers and their associated DRAMs. The<br />

majority of these are described as minimums, along with<br />

a minimum time before subsequent events are allowed.<br />

One of the primary JEDEC specification objectives<br />

is to avoid memory collisions caused by overlapping<br />

commands. Memory controllers and DRAMs therefore<br />

must be designed and tested for adherence to the JEDEC<br />

specifications across process, voltage, and temperature<br />

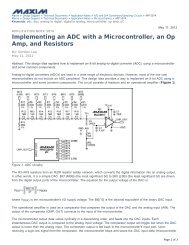

Table 1: <strong>DDR4</strong> vs. DDR3 key enhancements<br />

Figure 1: Evaluating and analyzing timing violations using protocol analyzers.<br />

variation during their functional testing with Automated<br />

Test Equipment (ATE). Additional variables introduced<br />

at the system level, such as DIMM design, socket,<br />

and motherboard design and layout, can contribute to<br />

timing violations at a system level, and must be taken<br />

into consideration.<br />

<strong>DDR4</strong> introduces the concept of Bank Groups that allow<br />

the system designer to build interleaved memory arrays<br />

down to the individual device level. For smaller systems,<br />

which may have only a single memory device, this Bank<br />

Group feature can offer substantial benefits.<br />

For example, one bank group can receive a series of<br />

pipelined commands for its upcoming data transfers.<br />

Once the first Bank Group starts its actual data transfers,<br />

another Bank Group can be initialized with its separate<br />

set of pipelined commands. After the first Bank Group<br />

completes its data transfers, the second Bank Group can<br />

initiate its data transfers, since it has already received its<br />

set of pipelined commands. In many cases, this Bank<br />

Group command pipelining can significantly reduce<br />

the impact of memory device delays, as shown below.<br />

A new generation of dedicated <strong>DDR4</strong> protocol analyzers,<br />

such as the Teledyne-LeCroy Kibra 480 system, provide<br />

automatic detection of JEDEC timing violations by<br />

monitoring memory IO on a live system. Validation<br />

engineers can leverage the flexibility of a protocol<br />

analyzer’s trigger state machine and its deeper recording<br />

memory to set up more complex triggering scenarios,<br />

or optionally use the analyzer in conjunction with an<br />

externally triggered oscilloscope for deeper signal<br />

integrity evaluation and analysis.<br />

Figure 1 illustrates a <strong>DDR4</strong> timing violation captured<br />

from a series of sequential accesses to the same DRAM<br />

bank group. The JEDEC tRRD_L specification requires a<br />

minimum delay of 6 clock periods between subsequent<br />

accesses. In this case, the tRRD_L specification has been<br />

violated since only 5 Clock intervals between activates<br />

are found in the captured trace. The memory controller<br />

needs to be adjusted so that the tRRD_L specification is<br />

properly met. In addition to the spec violation, this violation<br />

may also cause bus contention on the data lines.<br />

Further examination of the lower pane in Figure 1<br />

(Traffic Summary) illustrates the total number of timing<br />

violations in the captured traffic. Note that the traffic<br />

violation tool tip in the waveform pane highlights the<br />

expected timing interval (i.e. timing specification) versus<br />

the actual measured timing. Some of the timing violations<br />

can be attributed to poor design issues in the memory<br />

controller, while others could be caused by signal integrity<br />

marginalities introduced at the board level or sequence/<br />

pattern specific failures. As these violations are flagged,<br />

they point out problem areas for the memory system<br />

designer to investigate.<br />

22 <strong>EEWeb</strong> | Electrical Engineering Community<br />

Visit www.eeweb.com<br />

23

<strong>EEWeb</strong> PULSE TECH ARTICLE<br />

<strong>DDR4</strong> Configuration starts with<br />

MRS Commands<br />

<strong>DDR4</strong> introduces four new MRS commands to help<br />

support new features. Many of these new features are<br />

optional, allowing system integrators to turn them on<br />

and off based on the application. Making systems more<br />

configurable will involve verifying that specific functions<br />

are enabled by viewing the MRS commands.<br />

A critical feature in <strong>DDR4</strong> is the DQ Training with MPR<br />

that is initiated via the MR3 immediately after power on.<br />

This provides pre-defined registers that can be used<br />

to choose fixed or custom training patterns, which will<br />

be read in a controller specified order. Most memory<br />

designers will concede that <strong>DDR4</strong> will not reach the<br />

expected performance without receiver calibration. The<br />

MR3 payload (Figure 2) shows the Address lines (A2) is<br />

used to enable MPR training and the (A12 –A11) are used<br />

to identify the format of the MPR pattern.<br />

Using the <strong>DDR4</strong> Bus analyzer, it’s possible to trigger,<br />

capture, and decode the MR3 command. “MPR Page<br />

Selection:0” specifies that the DIMM should use the<br />

Multi Purpose Register 3 – page zero default patterns<br />

for training and transmit them in serial format. Toggling<br />

the “Dataflow from MPR” option programs the DRAM<br />

to respond with the specified pattern on the next READ<br />

command instead of from the memory array. Back-to-back<br />

reads can then be used to “tune” the receivers to operate<br />

with the highest signal integrity.<br />

Teledyne LeCroy’s Kibra 480 analyzer provides developers<br />

with unique ability to “Follow MRS Commands” on the<br />

fly. Enabling this option allows the analyzer to adjust<br />

the JEDEC timing intervals in real time. In the event the<br />

memory controller sends MRS commands that change<br />

specific parameters, the Follow MRS Commands option<br />

prevents the Kibra from detecting and reporting false<br />

errors (i.e.: MRS commands that toggle DQ Training<br />

mode or change the burst length).<br />

The timing analysis methods discussed above allow<br />

designers to quickly identify timing violations on an<br />

individual system basis. However, robust system designs<br />

should be able to accomodate platform, component, and<br />

DIMM variations. This requires a deeper characterization<br />

of critical timing specifications to ensure sufficient system<br />

design tolerances. As memory systems increase in speed<br />

and complexity, many controller and DIMM combinations<br />

may perform better than the JEDEC specification.<br />

Memory system designers need visibility into the system<br />

configuration and performance, as opposed to simple<br />

specification compliance. Dedicated bus analyzers, like<br />

the Teledyne-LeCroy Kibra 480 system, offer excellent<br />

flexibility to selectively sweep and measure critical timing<br />

Figure 2: Capture and decoding of MRS commands facilitates testing and verification of<br />

<strong>DDR4</strong> subsystem configuration<br />

Figure 3: Timing sensitivity analysis versus<br />

JEDEC specifications.<br />

parameters, helping measure the actual system design<br />

timing margins, as seen in Figure 3. Of unique value,<br />

timing analysis can be performed on previously captured<br />

traffic by simply modifying timing parameters and rerunning<br />

the analysis software on a personal computer,<br />

allowing the protocol analyzer to be freed up for more<br />

critical debug activities.<br />

Maximizing <strong>DDR4</strong> System Performance<br />

As mentioned earlier, while <strong>DDR4</strong> is designed to provide<br />

significant power and performance advantages over<br />

DDR3, in the interim their transfer rates are likely to<br />

overlap, giving the more mature, highly tuned DDR3<br />

designs a performance advantage (for the time being).<br />

Given the near term anticipated cost disadvantage of<br />

<strong>DDR4</strong> memory subsystems, early adopters should pay<br />

special attention to tuning their platform in order to<br />

maximize performance.<br />

<strong>DDR4</strong> architecture introduces the concept of two or four<br />

selectable bank groups, a unique feature that can be<br />

used to boost the performance of <strong>DDR4</strong> platforms. This<br />

allows for separate activation, access, and refresh of each<br />

unique bank group, improving overall memory efficiency<br />

and bandwidth.<br />

<strong>DDR4</strong> platforms can only achieve the highest throughputs<br />

with consecutive reads and writes when targeting different<br />

bank groups, allowing for lower latencies on commandto-command<br />

timing (tCCD-S) and faster burst access.<br />

New memory controller designs taking advantage of<br />

the <strong>DDR4</strong> bank groups must be thoroughly validated<br />

since interleaving data between<br />

bank groups increases the risk<br />

of collisions as <strong>DDR4</strong> systems<br />

pivot between CCD-S and<br />

CCD-L. This effort requires a<br />

high degree of visibility into the<br />

traffic patterns across the banks<br />

and bank groups.<br />

Figure 4 illustrates a <strong>DDR4</strong><br />

platform without <strong>DDR4</strong> bank<br />

group tuning. One can easily<br />

observe that memory access is<br />

sparsely distributed, with long<br />

periods of inactivity where the<br />

banks are left open for long<br />

periods of time.<br />

Figure 5 shows the same<br />

platform during a highly tuned memory access taking<br />

advantage of the performance advantages of bank groups<br />

with demonstrably quicker memory access. ■<br />

» CLICK HERE<br />

to comment on the article.<br />

24 <strong>EEWeb</strong> | Electrical Engineering Community<br />

Visit www.eeweb.com<br />

Figure 4<br />

Figure 5<br />

25

<strong>EEWeb</strong> PULSE TECH ARTICLE<br />

<strong>Design</strong><br />

& Analysis<br />

OF TDC CONVERTER ARCHITECTURES<br />

IN 80NM CMOS TECHNNOLOGY part<br />

2<br />

ABSTRACT:<br />

Umanath Kamath, Cypress Semiconductors<br />

Javier Rodriguez, Strukton Rolling Stock<br />

26 <strong>EEWeb</strong> | Electrical Engineering Community<br />

Visit www.eeweb.com<br />

By:<br />

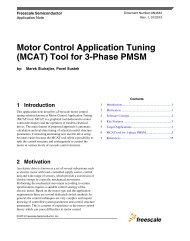

The first part of this article detailed the various topologies for realizing a time-to-digital<br />

converter with their trade-offs. This part will go through implementation of a TDC in 80nm<br />

CMOS process. The article concludes with results of the transistor level implementation<br />

giving the reader an understanding of the method while also appreciating the various<br />

applications to which it can be applied.<br />

27

<strong>EEWeb</strong> PULSE TECH ARTICLE<br />

Click the image below to read Part 1:<br />

Continued from Part 1<br />

5. SYSTEM OVERVIEW<br />

After choosing the TDC structure, we started working<br />

on our design implementation following a top-down<br />

approach. From our point of view, and due to the large<br />

degree of freedom available for this design, this was the<br />

most logical starting point.<br />

5.1. Matrix structure<br />

Choosing an appropriate matrix structure was the first<br />

design issue we had to face. As already mentioned, there<br />

are two main considerations to take into account:<br />

• Dummy structure minimization within the matrix,<br />

since they consume power and contribute to the overall<br />

design area.<br />

• Delay stage loading since a homogeneous load for<br />

every delay stage will contribute to an easier design and<br />

a better resolution controllability.<br />

As discussed before, a bigger matrix yields a larger<br />

number of dummy structures but a more homogeneous<br />

capacitive load for both X and Y delay chains, as the<br />

row-column ratio approaches 1 and the matrix becomes<br />

square, making resolution easier to set. A smaller matrix<br />

will have the opposite effect, thus yielding a smaller<br />

number of dummy structures but making resolution harder<br />

to set.<br />

Keeping these two design parameters in mind, we<br />

derived the mathematical expressions for calculating<br />

them. Afterwards, we built the following table which<br />

summarizes all the possible solutions for our 32 stage 2-D<br />

Vernier TDC design, allowing us to analyze the problem<br />

and find the best solution:<br />

From this table we can conclude the following: elements (X delay chain) and another one of 7 delay<br />

elements (Y delay chain).<br />

Figure 1: 2-D Vernier matrix figures of merit<br />

To achieve a square matrix, and therefore a homogeneous<br />

load for every delay element, we need a 17×17 matrix.<br />

However, this structure will yield an unacceptable number<br />

of dummy structures (88.93% of the matrix will consist<br />

of dummy structures). Hence this matrix layout was<br />

discarded.<br />

There is an interesting set of solutions, yielding a minimum<br />

number of columns (10 columns for 5, 6 and 7 rows).<br />

Naturally, the number of dummy structures increases<br />

with the number of rows. However, we finally chose the<br />

7×10 matrix configuration, as shown in Figure 2, since the<br />

dummy increment is not very large and the row-column<br />

ration is closer to 100% among those three configurations.<br />

Delay y<br />

1 8 15 22 29<br />

2 9 16 23 30<br />

3 10 17 24 31<br />

4 11 18 25 32<br />

5 12 19 26<br />

Delay x<br />

Figure 2: 7x10 TDC matrix structure<br />

5.2. DELAY CHAINS<br />

6 13 20 27<br />

7 14 21 28<br />

As seen in the previous chapters, the Vernier delay line<br />

architecture uses two different delay chains. While in the<br />

linear Vernier delay line architecture these chains only<br />

differ in the nominal propagation delay of each element<br />

(i.e. the propagation delay measured when the other<br />

input signal is tied to ground), 2-D Vernier delay chains<br />

also differ in the number of elements they are made of.<br />

For instance, a 32 stage linear Vernier TDC would need<br />

two delay chains of 32 delay elements each, while our<br />

2-D Vernier TDC would need only one chain of 10 delay<br />

For the delay stages within the chains, we decided to<br />

use non-inverting buffer structures as the main building<br />

blocks. These structures yield a worse propagation<br />

time than a single inverter, but they provide the delay<br />

comparison and encoding stages with a very simple<br />

time information format. For this purpose, we created<br />

two different components within our library, called BUF_X<br />

and BUF_Y.<br />

Since the Y delay chain has to be faster than the X delay<br />

chain but its capacitive load per delay element is, by<br />

construction, larger than the X’s, it makes sense to initially<br />

increase the size of the BUF_Y transistors. However, since<br />

we are only dealing with low-to-high transitions, this can<br />

be achieved by just increasing the pMOS transistor in<br />

the second inverter within the BUF_Y structure. For the<br />

BUF_X component we initially set to minimum size for<br />

both pMOS and nMOS transistors.<br />

Besides setting the minimum size, we added an extra<br />

delay element at the end of both delay chains. This final<br />

delay element was left open (actually it is driving a 1GΩ<br />

resistor to avoid Cadence WARNING messages) and<br />

its only goal is to balance every capacitive load within<br />

the chain.<br />

We also included an extra input delay stage on both chains,<br />

called FIX_DELAY within our library. These structures<br />

were used to provide a rise and fall time independent<br />

signals to the delay chain during the first design tests.<br />

While FIX_DELAY elements remained unchanged through<br />

the design process, BUF_X and BUF_Y buffers were<br />

resized and optimized to achieve the desired resolution.<br />

5.3. Delay comparators<br />

The time difference between the START and STOP signals<br />

is measured by the use of several memory elements<br />

which capture the moment when the START signal is<br />

surpassed by the STOP signal. Following this principle,<br />

a 32-bit pseudo thermo-code format is generated by<br />

the TDC, where the delay information is kept as the<br />

transition from 1 to 0. Finally, this code is passed to the<br />

5-bit encoding circuit.<br />

Choosing among all the available memory elements for<br />

this task, we followed the recommendations given in<br />

[1] and used a NAND gate based S-R latch as the basic<br />

delay comparison element. The main advantage which<br />

presents this structure is its symmetry for both S and<br />

R signals, helping us to achieve a more homogeneous<br />

capacitive loading for both the X and Y delay chains.<br />

Besides, we also included an inverting buffer at each<br />

output, as recommended in [1], making this device less<br />

sensitive to output loading variations and preventing the<br />

design from unwanted non-linear behavior.<br />

28 <strong>EEWeb</strong> | Electrical Engineering Community<br />

Visit www.eeweb.com<br />

S#<br />

R#<br />

Figure 3: Delay comparator (gate level)<br />

Figure 4: S-R latch truth table<br />

Q#<br />

Special care has to be taken when connecting the feedback<br />

and input signals to the NAND pull-down network due to<br />

data dependent delay. Indeed, the nominal propagation<br />

delay of each element within the chain can be affected<br />

by the S-R latch current state, introducing non-linear<br />

effects. In particular, for this TDC architecture, this effect<br />

becomes quite significant since there are several S-R<br />

latches connected to the same delay element output.<br />

Figure 5 shows the two possible configurations.<br />

VDD<br />

GND<br />

FB2<br />

FB2<br />

FB1<br />

S# R#<br />

FB1<br />

Config 1 Config 2<br />

FB1<br />

FB2<br />

VDD<br />

GND<br />

FB2<br />

FB2<br />

FB1<br />

S# R#<br />

Figure 5: Delay comparator (transistor level)<br />

We obtained some interesting results while testing both<br />

configurations; which are shown in Figure 6. In particular,<br />

this figure shows the propagation delay for each delay<br />

element within the X delay chain for both configurations.<br />

We used for this purpose a 10 ps resolution configuration<br />

and a time delay of 160 ps between the START and STOP<br />

FB1<br />

Q<br />

FB1<br />

FB2<br />

29

<strong>EEWeb</strong> PULSE TECH ARTICLE<br />

signals. Therefore, the STOP signal will catch the START<br />

signal in the 16th delay comparator (2nd row, 3rd column).<br />

As can be seen, the propagation delay for the first<br />

configuration remains constant for the first and second<br />

columns, but it starts to decrease linearly after that due to<br />

a change in the capacitive load (data dependent delay).<br />

This is, of course, an undesired effect which must be<br />

avoided to prevent a non-linear behavior. On the other<br />

hand, by using the second configuration, each delay<br />

element within the X delay chain achieves a more uniform<br />

propagation delay and it’s almost data independent.<br />

Despite the fact that the use of this S-R latch configuration<br />

increases the nominal propagation delay, it is not a<br />

big issue and it can be readjusted by sizing the delay<br />

elements. Therefore we will be using the 2nd configuration<br />

in our SR_LATCH library component.<br />

Propagation Delay (ps)<br />

85<br />

83<br />

81<br />

79<br />

77<br />

75<br />

73<br />

71<br />

69<br />

67<br />

65<br />

Config 1<br />

Nom. Config 1 Config 2 Nom. Config 2<br />

X1-X2 X2-X3 X3-X4 X4-X5 X5-X6 X6-X7 X7-X8 X8-X9 X9-X10<br />

Delay Stage (X delay chain)<br />

Figure 6: Data dependent analysis for<br />

both configurations<br />

This concludes the basic description of our TDC delay<br />

comparator. However, as will be discussed in chapter 6,<br />

and due to the amount of dummy S-R latches introduced<br />

by the TDC matrix, we proceeded to substitute them for<br />

more optimal structures which roughly present the same<br />

capacitive loading, helping us to save area and power.<br />

Hence a new library component, called DUMMY, was<br />

created.<br />

5.4. Readout encoder<br />

Finally, we focused on the 32 to 5 encoder needed for the<br />

readout circuit. Since the existing/available testbench<br />

provided us with a quite good encoder, we decided to<br />

spend more effort into the matrix optimization.<br />

6. TUNING THE DESIGN<br />

Once the main design features have been described in<br />

the previous chapter, now we present all the different<br />

strategies we followed to achieve our current design.<br />

6.1. Area minimization<br />

Since our design was quite large in terms of the number<br />

of transistors, area minimization is a critical goal which<br />

allowed us to improve our design performance. In<br />

particular, we focused on the TDC matrix structure and<br />

devised several ways to improve its area consumption.<br />

6.1.1. Y chain load reduction<br />

We realized that for each row within the matrix, there are<br />

at most five out of ten useful devices for delay comparison.<br />

Hence, the Y delay chain had an excessive loading, which<br />

affected both the acquisition time and the circuit area for<br />

the same resolution.<br />

However, as we presented in the previous chapter, our<br />

S-R latch configuration made the circuit almost data<br />

independent. This feature allowed us to disconnect them<br />

from the Y chain and tie them to ground without harming<br />

the circuit performance. Figure 7 shows the TDC matrix<br />

after performing this optimization step, where red dots<br />

represent the S-R latches which were disconnected from<br />

the Y delay chain. However, there were still three dummy<br />

S-R latch structures left to balance the capacitive load.<br />

Delay y<br />

1 8 15 22 29<br />

2 9 16 23 30<br />

3 10 17 24 31<br />

4 11 18 25 32<br />

5 12 19 26<br />

Delay x<br />

Figure 7: Y delay chain optimization<br />

6 13 20 27<br />

7 14 21 28<br />

The, Y chain load was greatly reduced, thus reducing<br />

the propagation delay for each delay element within<br />

the chain. Furthermore, the propagation delay for each<br />

delay element within the X delay chain remained almost<br />

constant due to our S-R latch structure.<br />

6.1.2. Dummy structures<br />

After the Y chain optimization, most of the S-R latches had<br />

one of their input tied to ground. Looking at their gate<br />

level schematic, it was easy to conclude the following:<br />

• Since one NAND gate had an input tied to ground, its<br />

output is tied to 1. This output is used as one of the inputs<br />

of the other NAND gate within the component.<br />

• Removing the former NAND gate along with its<br />

associated inverter reduced the circuit area maintaining a<br />

constant propagation delay for the X chain delay elements.<br />

• However, since these structures do not commute,<br />

dynamic power consumption was not affected by this<br />

optimization.<br />

With these ideas in mind, we obtained the following<br />

structure for our DUMMY component, which is basically<br />

a capacitive load:<br />

6.2. Resolution optimization<br />

As shown in section 3.2, our TDC resolution is given by<br />

the following relationships:<br />

30 <strong>EEWeb</strong> | Electrical Engineering Community<br />

Visit www.eeweb.com<br />

VDD<br />

R#<br />

GND<br />

1<br />

Figure 8: Dummy component (transistor level)<br />

1<br />

NOTE: A further area optimization can be easily done by<br />

removing one of the pMOS transistors within the NAND<br />

gate since it is always OFF. However we did not realize<br />

that until later, we could not include it in the submitted<br />

TDC design.<br />

6.1.3. S-R latch optimization<br />

Our final area improvement dealt with the active S-R<br />

latches themselves. As we only used one of the device<br />

outputs, we just removed the unused output, along with its<br />

associated inverter. By introducing this modification, we<br />

did not observe any major change in the delay element’s<br />

propagation delay.<br />

VDD<br />

GND<br />

S# R#<br />

Figure 9: Final S-R latch component (transistor level)<br />

The following table summarizes all the relevant parameters<br />

needed for a given resolution ranging from 5 to 10 ps:<br />

Figure 10: TDC resolution chart<br />

Therefore, by just sizing the delay elements within both<br />

delay chains we can achieve any required resolution.<br />

However, our TDC architecture presents two major<br />

drawbacks in comparison with the linear Vernier delay<br />

line architecture:<br />

• Our resolution is totally dependent on the propagation<br />

delay of each delay elements, as can be seen in the<br />

table above. Ignoring this fact will cause the system to<br />

behave in an unpredictable and highly non-linear way.<br />

Hence bigger delay elements will be needed if aiming<br />

for high resolution.<br />

• Each delay element has to drive a larger load, due to the<br />

matrix configuration. Again, sizing becomes a problem<br />

for a given resolution, limiting our design space.<br />

Due to this, we aimed for a 9 ps resolution, which is<br />

slightly better than the proposed in the midterm report<br />

and does not imply too large transistors.<br />

Q<br />

31

<strong>EEWeb</strong> PULSE TECH ARTICLE<br />

6.2.1. Sizing procedure<br />

For delay elements sizing we used the approach from<br />

[5], using the following circuit:<br />

1<br />

Figure 11: Delay element sizing problem<br />

, which follows the equation:<br />

S<br />

C L<br />

To solve this equation, we first found the values of t p0 and<br />

the load ratio by simulating the circuit for two different<br />

values of S. Finally, knowing these two parameters, we<br />

could find the value of S for our desired t p . The following<br />

table shows the final values for the transistors within the<br />

delay chains:<br />

Figure 12: Delay chain sizing summary<br />

NOTE: Sizing could be further improved since the first<br />

inverter always performs high to low transitions and the<br />

second inverter always performs low to high transitions.<br />

Therefore, the X BUFFER 2nd inverter nMOS width could<br />

have been left to 120 μm without affecting resolution.<br />

7. FINAL RESULTS AND CONCLUSIONS<br />

With this article, we have shown the procedure we followed<br />

to implement our submitted TDC design. This design<br />

achieves a relatively high time resolution while area and<br />

power consumption has been reduced in comparison with<br />

the original design, described in [1]. In this sense, our<br />

design meets all the requirements described in section<br />

2. To conclude, a summary with all the relevant results<br />

is provided in section 9.<br />

7.1. Challenges and future work<br />

We could not complete all of them, but would like to<br />

include them for reference:<br />

• The given encoder is mostly responsible for power<br />

consumption for high output codes. By increasing its<br />

complexity, power can be reduced for these stages,<br />

yielding a lower average energy and power consumption.<br />

• Acquisition time can also be improved by just using a<br />

different encoder architecture which balances the output<br />

signals code load. Increasing the S-R latch output inverter<br />

can also help to reduce the system acquisition time.<br />

• Better resolution can be achieved by further sizing both<br />

delay chains, as described in section 6.2.<br />

ACKNOWLEDGEMENTS:<br />

The authors wish to acknowledge the references from<br />

the course notes of Digital IC <strong>Design</strong> course at Delft<br />

University of Technology. They also are grateful for various<br />

discussions and inputs from Prof.Nick van der Meijs<br />

during the course of the project.<br />

8. REFERENCES<br />

[1] Vercesi, L., Liscidini, A., Castello, R., “Two-Dimensions<br />

Vernier Time-to-Digital Converter”, IEEE Journal of Solid-<br />

State Circuits, August 2010, pp 1504-1512.<br />

[2] Chen, P., Liu, S. I., Wu, J., “A CMOS pulse shrinking<br />

delay element for time interval measurement”, IEEE<br />

Transactions on Circuits and Systems II,: Analog and<br />

Digital Signal Processing, September 2000.<br />

[3] Staszewski, R. B., Vemulapalli, S., Vallur, P., Wallberg,<br />

J., Balsara, P. T., “1.3 V 20 ps time-to-digital converter for<br />

frequency synthesis in 90-nm CMOS,” IEEE Transactions<br />

on Circuits and Systems II: Express Briefs, March 2006.<br />

[4] Henzler, S., Koeppe, S., Lorenz, D., Kamp, W.,<br />

Kuenemund, R., Schmitt-Landsiedel, D., “A Local Passive<br />

Time Interpolation Concept for Variation-Tolerant High-<br />

Resolution Time-to-Digital Conversion”, IEEE Journal of<br />

Solid State Circuits, July 2008.<br />

[5] Rabaey, J. M., Chandrakasan, A., Nikolic,B., “Digital<br />

Integrated Circuits, a <strong>Design</strong> Perspective” 2nd edition,<br />

Prentice Hall, 2006.<br />

» CLICK HERE<br />

There are some further issues which can be easily<br />

optimized and can lead our design to better performance. to comment on the article.<br />

Parameter<br />

Architecture<br />

Optimized parameter<br />

Voltage supply<br />

Average resolution<br />

Average resolution (slow)<br />

Average resolution (fast)<br />

Area/min. INV size area<br />

Total Power<br />

Average Power<br />

Total Energy<br />

Average Energy<br />

Acquisition time (50%)<br />

Acquisition time (90%)<br />

Advantages<br />

Drawbacks<br />

Targeted application<br />

Umanath Kamath received his Master’s degree<br />

in 2012 from Delft University of Technology,<br />

Delft, the Netherlands and Bachelors degree in<br />

2009 from M.S.Ramaiah Institute of Technology,<br />

Bangalore, India both in electronics. He is currently<br />

a Senior <strong>Design</strong> Engineer with Cypress Semiconductors.<br />

He has held visiting positions during his<br />

studies with IMEC and CMOSIS in Belgium and<br />

Honeywell Research Labs in India. His interests<br />

are in the area of analog and mixed signal circuit<br />

design, low power sensor interfaces, power manag<br />

ment circuits and sigma-delta converters.<br />

9. PROJECT OVERVIEW<br />

9.1. Project summary table<br />

32 <strong>EEWeb</strong> | Electrical Engineering Community<br />

Visit www.eeweb.com<br />

Value<br />

2-D Vernier<br />

Area & Power<br />

1 V<br />

8.96 ps<br />

11.68 ps<br />

6.93 ps<br />

340.375<br />

2.58 mW<br />

0.08 mW<br />

6.462424 pl<br />

0.201951 pl<br />

1.044 ns<br />

1.23 ns<br />

High linearity, low power<br />

High area overhead<br />

RF PLL<br />

About the Authors<br />

Javier Rodriguez received his Telecommunication<br />

Engineering degree from Technical University<br />

of Madrid (UPM) in 2006. After 3 years working<br />

as a R&D engineer in Spain, he obtained his MSc<br />

in Electrical Engineering (Microelectronics) from<br />

Delft University of Technology in 2012, focusing<br />

on circuit design automation and verification techniques.<br />

He is currently working at Strukton Rolling<br />

Stock as a Software Engineer.<br />

33

Productive Lies<br />

Sneaky Delivery - Part 1<br />

GPS Re-route - Part 2