CARLETON UNIVERSITY - Department of Electronics at Carleton ...

CARLETON UNIVERSITY - Department of Electronics at Carleton ...

CARLETON UNIVERSITY - Department of Electronics at Carleton ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>CARLETON</strong> <strong>UNIVERSITY</strong><br />

DURATION: HOURS No. <strong>of</strong> Student:<br />

<strong>Department</strong> Name & Course Number:<br />

Course Instructor(s)<br />

AUTHORIZED MEMORANDA<br />

Final<br />

EXAMINATION<br />

April 24, 2002<br />

Students MUST count the number <strong>of</strong> pages in this examin<strong>at</strong>ion question paper before beginning to<br />

write, and report any discrepancy immedi<strong>at</strong>ely to a proctor. This question paper has 18 pages.<br />

This examin<strong>at</strong>ion paper May Not be taken from the examin<strong>at</strong>ion room.<br />

In addition to this question paper, students require: an examin<strong>at</strong>ion booklet yes no x may request<br />

a Scantron sheet yes no x<br />

page 1 2 3 4 5 6 7 8 9 10 11 12<br />

Name:<br />

Number:<br />

Sign<strong>at</strong>ure:<br />

3 398<br />

Electronic Engineering 97.267A,B and C<br />

Tom Ray and John Knight<br />

Any notes; any non-communic<strong>at</strong>ing calcul<strong>at</strong>or.<br />

Please write your answers on the examin<strong>at</strong>ion paper. You may ask for a booklet if you need it.<br />

Attempt all questions except do only one <strong>of</strong> questions 10 and 11.<br />

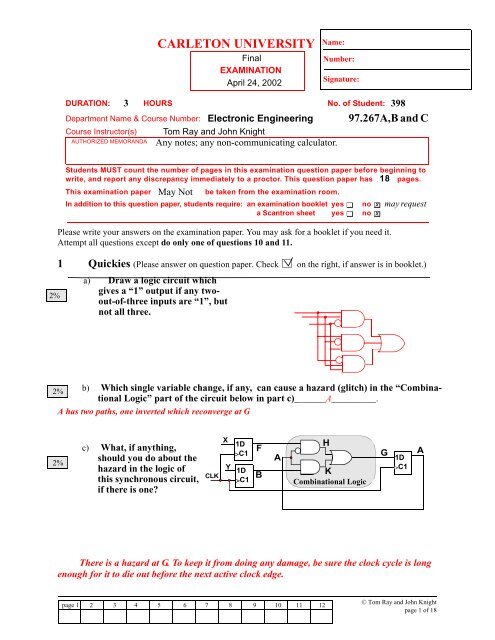

1 Quickies (Please answer on question paper. Check on the right, if answer is in booklet.)<br />

a) Draw a logic circuit which<br />

2%<br />

gives a “1” output if any twoout-<strong>of</strong>-three<br />

inputs are “1”, but<br />

not all three.<br />

2% b) Which single variable change, if any, can cause a hazard (glitch) in the “Combin<strong>at</strong>ional<br />

Logic” part <strong>of</strong> the circuit below in part c)_______A__________.<br />

A has two p<strong>at</strong>hs, one inverted which reconverge <strong>at</strong> G<br />

2%<br />

c) Wh<strong>at</strong>, if anything,<br />

should you do about the<br />

hazard in the logic <strong>of</strong><br />

this synchronous circuit,<br />

if there is one?<br />

CLK<br />

X<br />

Y<br />

1D<br />

C1<br />

1D<br />

C1<br />

F<br />

A<br />

H<br />

G<br />

1D<br />

A<br />

B<br />

K<br />

Combin<strong>at</strong>ional Logic<br />

C1<br />

There is a hazard <strong>at</strong> G. To keep it from doing any damage, be sure the clock cycle is long<br />

enough for it to die out before the next active clock edge.<br />

© Tom Ray and John Knight<br />

page 1 <strong>of</strong> 18

2%<br />

<strong>Carleton</strong> University <strong>Electronics</strong>, 97.267A, B and C Final April 24, 2002<br />

4%<br />

2%<br />

d) Many logic circuits run from a 5 volt power supply<br />

and receive and send out logic signals which have a<br />

logic “0” as 0 volts and a logic “1” as 5 volts. However<br />

in this instance the input signals are not the usual.<br />

C is 4.0 volts and B is 0.8 volts.<br />

Wh<strong>at</strong> logic level would you expect <strong>at</strong> A__0__<br />

Wh<strong>at</strong> logic level would you expect <strong>at</strong> R__1__<br />

4 V is an adequ<strong>at</strong>e 1, 0.8 V is an adequ<strong>at</strong>e 0.<br />

e) Simplify A+AB+BC+CD+DE+EF and don’t take too much space.<br />

=A+B +BC+CD+DE+EF (x+xz=x+z)<br />

=A+B +C+CD+DE+EF (x+xz=x+z)<br />

=A+B +C+D+DE+EF (x+xz=x+z)<br />

=A+B +C+D+E+EF (x+xz=x+z)<br />

=A+B +C+D+E (x+xz=x)<br />

f) Plot A·BC+BCDE on a Karnaugh map<br />

A·BC is on both maps.<br />

BCDE is on the E level (map only)<br />

+5 volt power supply<br />

© Tom Ray and John Knight April 14, 2003 page 2, <strong>of</strong> 18<br />

+<br />

C=4 volt<br />

B=0.8 volt<br />

AB\ CD AB\ CD<br />

1 1 1 1<br />

AB\ CD<br />

R<br />

E E<br />

AB\<br />

1 1<br />

CD<br />

1 1<br />

1<br />

A<br />

1a)See<br />

booklet<br />

1b)See<br />

booklet<br />

1c)See<br />

booklet

<strong>Carleton</strong> University <strong>Electronics</strong>, 97.267A, B and C Final April 24, 2002<br />

2 More Quickies<br />

a) Change to a minimal sum <strong>of</strong> products form.<br />

4%<br />

2%<br />

(A +BC)(A+EF)(ABC + DB )<br />

(AEF + ABC)(ABC + DB) swap<br />

AEFDB + ABC D2<br />

Taking the dual here is a mark loser.<br />

So is brute force multiplying out to 8 terms.<br />

People who did so almost alwas made a mistake, and none got the minimal answer.<br />

b) A minimized synchronous finite-st<strong>at</strong>e machine has<br />

11 inputs,<br />

14 outputs,<br />

40 st<strong>at</strong>es in which 3 are equivalent,<br />

and 129 logic g<strong>at</strong>es.<br />

How many flip-flops does it have?<br />

_________6_______<br />

6 flip-flops can give 2 6 st<strong>at</strong>es.<br />

5 flip-flops can only give 32.<br />

Pay no <strong>at</strong>tantion to all th<strong>at</strong> other confusing info.<br />

© Tom Ray and John Knight April 14, 2003 page 3, <strong>of</strong> 18<br />

2a)See<br />

booklet<br />

2b)See<br />

booklet

<strong>Carleton</strong> University <strong>Electronics</strong>, 97.267A, B and C Final April 24, 2002<br />

3%<br />

c) You have studied synchronous machines, asynchronous machines,<br />

Mealy outputs and Moore outputs.<br />

Which kind(s) <strong>of</strong> machine need race-free st<strong>at</strong>e assignments?<br />

_________________________asynch____________________________<br />

2%<br />

Which kind(s) <strong>of</strong> machine respond the most quickly to input changes?<br />

_______________________asynch______________________________<br />

_______________________Mealy_____________________________<br />

d) If 1101 is a two’s complement binary number, wh<strong>at</strong> is its value in decimal?<br />

1101 = -2 3 *1 + ( 2 2 *1 + 2 1 *0 + 2 0 *1 )= -8+5=-3,<br />

or 1101 0010<br />

+1<br />

0011 = 3dec<br />

hence the original was -3.<br />

© Tom Ray and John Knight April 14, 2003 page 4, <strong>of</strong> 18

<strong>Carleton</strong> University <strong>Electronics</strong>, 97.267A, B and C Final April 24, 2002<br />

3 MUX Logic and Hazards<br />

e) Implement the function F using one or more <strong>of</strong> the MUXs shown. You may<br />

use as many MUXs <strong>of</strong> any type as you need but:<br />

- do not change the inputs, or the ordering <strong>of</strong> the inputs, on the symbols.<br />

- do not use more hardware than needed for your method <strong>of</strong> implement<strong>at</strong>ion.<br />

4%<br />

abc<br />

000<br />

001<br />

010<br />

011<br />

100<br />

101<br />

110<br />

111<br />

abc<br />

ab<br />

00<br />

01<br />

10<br />

11<br />

a b<br />

bc<br />

00<br />

01<br />

10<br />

11<br />

bc<br />

f) Revise the equ<strong>at</strong>ion for H, below, to make the function free <strong>of</strong> st<strong>at</strong>ic hazards.<br />

Give the minimal form th<strong>at</strong> is still hazard free.<br />

7%<br />

F= ab + ac +ac<br />

Not well covered in 2003<br />

© Tom Ray and John Knight April 14, 2003 page 5, <strong>of</strong> 18<br />

ac<br />

00<br />

01<br />

10<br />

11<br />

a c<br />

c<br />

a<br />

b<br />

F= ab + ac +ac<br />

1<br />

0<br />

1<br />

1<br />

1<br />

0<br />

1<br />

0<br />

b+c c<br />

0<br />

c<br />

3a)See<br />

booklet

<strong>Carleton</strong> University <strong>Electronics</strong>, 97.267A, B and C Final April 24, 2002<br />

Put the circles (loops) for the hazard free function including masks on the right hand<br />

map.<br />

Write the equ<strong>at</strong>ion including masks below the map<br />

Blanks<br />

are zeros<br />

CD<br />

AB 00<br />

00 1<br />

D<br />

01 11 10<br />

1 1 1<br />

01 1 1<br />

A<br />

11 1<br />

10 1 1 1<br />

C<br />

CD<br />

AB 00<br />

00 1<br />

D<br />

01 11 10<br />

1 1 1<br />

01 1 1<br />

A<br />

11 1<br />

10 1 1 1<br />

C<br />

CD<br />

AB 00<br />

00 1<br />

D<br />

01 11 10<br />

1 1 1<br />

01 1 1<br />

A<br />

11 1<br />

10 1 1 1<br />

C<br />

H= AD +A B +BD + AC D + BC<br />

B<br />

B<br />

B<br />

H=A·B·D +AD+A·C·D +A·B·C<br />

CD<br />

AB 00<br />

00 1<br />

D<br />

01 11 10<br />

1 1 1<br />

01 1 1<br />

A<br />

11 1<br />

10 1 1 1<br />

C<br />

CD<br />

AB 00<br />

00 1<br />

D<br />

01 11 10<br />

1 1 1<br />

01 1 1<br />

A<br />

11 1<br />

10 1 1 1<br />

C<br />

CD<br />

AB 00<br />

00 1<br />

D<br />

01 11 10<br />

1 1 1<br />

01 1 1<br />

A<br />

11 1<br />

10 1 1 1<br />

C<br />

© Tom Ray and John Knight April 14, 2003 page 6, <strong>of</strong> 18<br />

B<br />

B<br />

B

8%<br />

<strong>Carleton</strong> University <strong>Electronics</strong>, 97.267A, B and C Final April 24, 2002<br />

4 Races and Cycles<br />

Do rough work on the top table.<br />

The bottom table will be marked.<br />

Arrows in the bottom table, which<br />

are not part <strong>of</strong> the answer, will give<br />

neg<strong>at</strong>ive marks.<br />

a) Indic<strong>at</strong>e any cycles or races.<br />

b) Indic<strong>at</strong>e the p<strong>at</strong>h(s) from an<br />

initial stable st<strong>at</strong>e by which<br />

one enters the cycle or race.<br />

c) Iftheracealonecouldcause<br />

the circuit to malfunction write<br />

BAD beside the arrow.<br />

If the circuit should function<br />

s<strong>at</strong>isfactorily with the race,<br />

writeOKbesidethearrow.<br />

For a cycle write CY inside the<br />

loop<br />

we hope you have formed from<br />

the arrows.<br />

Present Next St<strong>at</strong>e, p + ,q +<br />

St<strong>at</strong>e for inputs x,y<br />

© Tom Ray and John Knight April 14, 2003 page 7, <strong>of</strong> 18<br />

PQ<br />

x,y<br />

00<br />

x,y<br />

01<br />

x,y<br />

11<br />

x,y<br />

10<br />

00 00 01 10 00<br />

01 01 00 01 01<br />

11 00 11 11 10<br />

10 10 11 01 11<br />

Present Next St<strong>at</strong>e, p + ,q +<br />

St<strong>at</strong>e for inputs x,y<br />

PQ<br />

x,y<br />

00<br />

x,y<br />

01<br />

x,y<br />

11<br />

x,y<br />

10<br />

00<br />

01<br />

00<br />

01<br />

01<br />

cy<br />

00<br />

10<br />

01<br />

00<br />

01<br />

11 00 11 11 10<br />

cy<br />

10 10 11 01 11<br />

Present Next St<strong>at</strong>e, p + ,q +<br />

St<strong>at</strong>e for inputs x,y<br />

PQ<br />

x,y<br />

00<br />

x,y<br />

01<br />

x,y<br />

11<br />

x,y<br />

10<br />

00 00 01 10 00<br />

01 01 00 01 01<br />

11 00 11 11 10<br />

10 10 11 01 11<br />

Present Next St<strong>at</strong>e, p + ,q +<br />

St<strong>at</strong>e for inputs x,y<br />

PQ<br />

BAD<br />

x,y<br />

00<br />

x,y<br />

01<br />

x,y<br />

11<br />

x,y<br />

10<br />

00<br />

01<br />

00<br />

01<br />

01<br />

cy<br />

00<br />

10<br />

01<br />

00<br />

01<br />

11 00 11 11 10<br />

cy<br />

10 10 11 01 11<br />

BAD<br />

BAD<br />

4) See<br />

booklet

<strong>Carleton</strong> University <strong>Electronics</strong>, 97.267A, B and C Final April 24, 2002<br />

10%<br />

5 Minimiz<strong>at</strong>ion <strong>of</strong> Multiple Outputs<br />

Minimizethelogicsize.<br />

a) Show your final circles on the lower map, rough work on the top maps.<br />

b) Shade the circles th<strong>at</strong> are common to two or more maps.<br />

c) Write the logic equ<strong>at</strong>ions under the maps.<br />

YZ<br />

WX 00<br />

00<br />

Z<br />

01 11 10<br />

1 1 1<br />

YZ<br />

WX 00<br />

00 1<br />

Z<br />

01 11 10<br />

1 1<br />

YZ<br />

WX 00<br />

00<br />

Z<br />

01 11 10<br />

1<br />

01<br />

11<br />

W<br />

10 d<br />

1 1<br />

1<br />

1<br />

1<br />

X<br />

01<br />

11<br />

W<br />

10 d 1<br />

X<br />

01<br />

11<br />

W<br />

10 1<br />

1<br />

1<br />

1<br />

1<br />

1<br />

1<br />

Y<br />

Y<br />

Y<br />

Map <strong>of</strong> F<br />

Map <strong>of</strong> G<br />

Map <strong>of</strong> H<br />

3circlesto<br />

get 1 bit<br />

YZ<br />

WX 00<br />

00<br />

Z<br />

01 11 10<br />

1 1 1<br />

YZ<br />

WX 00<br />

00 1<br />

Z<br />

01 11 10<br />

1 1<br />

YZ<br />

WX 00<br />

00<br />

Z<br />

01 11 10<br />

1<br />

2circlesto<br />

get 1 bit<br />

01<br />

11<br />

W<br />

10 d<br />

1 1<br />

1<br />

1<br />

1<br />

X<br />

01<br />

11<br />

W<br />

10 d 1<br />

X<br />

01<br />

11<br />

W<br />

10 1<br />

1<br />

1<br />

1<br />

1<br />

1<br />

1<br />

X<br />

Y<br />

Y<br />

Y<br />

Can share<br />

but extra<br />

YZ<br />

WX 00<br />

00<br />

Z<br />

01 11 10<br />

1 1 1<br />

YZ<br />

WX 00<br />

00 1<br />

Z<br />

01 11 10<br />

1 1<br />

YZ<br />

WX 00<br />

00<br />

Z<br />

01 11 10<br />

1<br />

work to get<br />

1 and 1<br />

01<br />

11<br />

W<br />

10 d<br />

1 1<br />

1<br />

1<br />

1<br />

X<br />

01<br />

11<br />

W<br />

10 d 1<br />

X<br />

01<br />

11<br />

W<br />

10 1<br />

1<br />

1<br />

1<br />

1<br />

1<br />

1<br />

X<br />

Alot<strong>of</strong><br />

work for a<br />

d<br />

YZ<br />

WX 00<br />

00<br />

01<br />

11<br />

W<br />

10 d<br />

Y<br />

Z<br />

01 11 10<br />

1 1 1<br />

1 1 1<br />

1 1<br />

X<br />

YZ<br />

WX 00<br />

00 1<br />

01<br />

11<br />

W<br />

10 d<br />

Y<br />

Z<br />

01 11 10<br />

1 1<br />

1<br />

X<br />

YZ<br />

WX 00<br />

00<br />

01<br />

11<br />

W<br />

10 1<br />

Y<br />

Z<br />

01 11 10<br />

1<br />

1 1 1<br />

1 1 1<br />

X<br />

Y<br />

Y<br />

Y<br />

YZ<br />

WX 00<br />

00<br />

Z<br />

01 11 10<br />

1 1 1<br />

YZ<br />

WX 00<br />

00 1<br />

Z<br />

01 11 10<br />

1 1<br />

YZ<br />

WX 00<br />

00<br />

Z<br />

01 11 10<br />

1<br />

01<br />

11<br />

W<br />

10 d<br />

1 1<br />

1<br />

1<br />

1<br />

X<br />

01<br />

11<br />

W<br />

10 d 1<br />

X<br />

01<br />

11<br />

W<br />

10 1<br />

1<br />

1<br />

1<br />

1<br />

1<br />

1<br />

X<br />

A=WY<br />

Y<br />

Y<br />

Y<br />

B=WXZ<br />

F=A+B+C+XY G=Z X+C<br />

H=WX+A+B+C<br />

C=W X Y Z<br />

22 letters, 9 g<strong>at</strong>es<br />

© Tom Ray and John Knight April 14, 2003 page 8, <strong>of</strong> 18<br />

X

8% 12%<br />

<strong>Carleton</strong> University <strong>Electronics</strong>, 97.267A, B and C Final April 24, 2002<br />

6 St<strong>at</strong>e Graph <strong>of</strong> a Synchronous Machine<br />

Draw the st<strong>at</strong>e graph for a Moore machine which has one input X, and two out-<br />

puts Y and Z:<br />

Y=1 whenever the machine receives the sequence 1001.<br />

Z=1 whenever the machine receives the sequence 0101.<br />

The leftmost bit is received first.<br />

Overlapped sequences are to be detected.<br />

Y and Z are zero except for the single clock period after the appropri<strong>at</strong>e sequence<br />

is completed.<br />

The machine starts <strong>at</strong> the RESET st<strong>at</strong>e.<br />

Draw only the st<strong>at</strong>e graph<br />

Use only the st<strong>at</strong>es provided below and do not change anything already given.<br />

Got<br />

Nothing<br />

Got 0 Got 01 Got 010 Got 0101<br />

Got<br />

Nothing<br />

Reset<br />

YZ=00<br />

0 Tom<br />

YZ=00<br />

0<br />

1<br />

1<br />

Got 01011<br />

Got 1<br />

Got 10<br />

Got 100<br />

Got 1001<br />

Anita<br />

YZ=00<br />

1<br />

Got 11<br />

0<br />

YZ=00<br />

0<br />

Yana<br />

YZ=00<br />

1<br />

Got 011<br />

Y<strong>at</strong>ish<br />

0101<br />

Got 10011<br />

1001<br />

1<br />

1<br />

1<br />

0<br />

Dick<br />

YZ=00<br />

Prize<br />

YZ=10<br />

© Tom Ray and John Knight April 14, 2003 page 9, <strong>of</strong> 18<br />

0<br />

0<br />

Harry<br />

YZ=00<br />

Got 1000<br />

1<br />

Win<br />

YZ=01<br />

0<br />

Got 01010<br />

Got 0 <strong>of</strong> 0101<br />

Got Nothing <strong>of</strong> 1001<br />

Got 010<br />

Got 10010<br />

<strong>of</strong> 0101<br />

Got 10 <strong>of</strong> 1001<br />

1

<strong>Carleton</strong> University <strong>Electronics</strong>, 97.267A, B and C Final April 24, 2002<br />

.<br />

Got<br />

Nothing<br />

Got 1<br />

Got 10<br />

Got 100<br />

Got 1001<br />

Got<br />

Nothing<br />

Reset<br />

YZ=00<br />

1<br />

Anita<br />

YZ=00<br />

0<br />

1<br />

0<br />

1<br />

Got 0 Got 01 Got 010 Got 0101<br />

Tom<br />

YZ=00<br />

Y<strong>at</strong>ish<br />

YZ=00<br />

0<br />

Yana<br />

YZ=00<br />

0<br />

1<br />

1<br />

0<br />

1<br />

1<br />

Dick<br />

YZ=00<br />

Prize<br />

YZ=10<br />

© Tom Ray and John Knight April 14, 2003 page 10, <strong>of</strong> 18<br />

0<br />

0<br />

0<br />

Harry<br />

YZ=00<br />

1<br />

YZ=01<br />

0<br />

Win<br />

1

8% 7%<br />

<strong>Carleton</strong> University <strong>Electronics</strong>, 97.267A, B and C Final April 24, 2002<br />

7 St<strong>at</strong>e Graph to Timing Diagram<br />

CLK<br />

I<br />

St<strong>at</strong>e<br />

z<br />

For the st<strong>at</strong>e graph shown below:<br />

a) Find one impossibility, circle it. and say wh<strong>at</strong> it is (in 10 words or less).<br />

Answer__Two next st<strong>at</strong>es for the same input (I=1 in st<strong>at</strong>e B) is impossible.<br />

b) Complete the timing diagram from the st<strong>at</strong>e graph. Show the present st<strong>at</strong>e and the output Z.<br />

The impossibility in a) should not affect the answer.<br />

C<br />

I=0->z=1<br />

I=1->z=0<br />

I=0<br />

I=1<br />

R<br />

z=0<br />

I=0<br />

I=0<br />

I=1<br />

I=1<br />

B<br />

I=0->z=0<br />

I=1->z=1<br />

© Tom Ray and John Knight April 14, 2003 page 11, <strong>of</strong> 18<br />

I=1<br />

I=0<br />

D<br />

z=1<br />

I=1<br />

R D C B A<br />

I=0<br />

A<br />

z=1<br />

St<strong>at</strong>es only change on the clock edge.<br />

Check input just before the clock edge to calcul<strong>at</strong>e next st<strong>at</strong>e<br />

Look inside st<strong>at</strong>e bubble for outputs inform<strong>at</strong>ion.<br />

Only one input, so can just write 1, 0.<br />

C 0<br />

B<br />

z=I<br />

z=I<br />

Another way <strong>of</strong> giving outputs<br />

1<br />

I=1<br />

7)See<br />

booklet

8%<br />

<strong>Carleton</strong> University <strong>Electronics</strong>, 97.267A, B and C Final April 24, 2002<br />

8 St<strong>at</strong>e Table to Circuit<br />

Design a machine with minimum logic to implement the following st<strong>at</strong>e table.<br />

Only the K-maps and the combin<strong>at</strong>ional circuits for the D inputs (DA and DB ) and Z are expected.<br />

Do not change the st<strong>at</strong>es, st<strong>at</strong>e assignment or the oper<strong>at</strong>ion <strong>of</strong> the machine<br />

St<strong>at</strong>e<br />

Q A Q B<br />

.<br />

St<strong>at</strong>e Q A + QB +<br />

I=0 I=1<br />

Output Z<br />

I=0 I=1<br />

R=0 0 V T 0 1<br />

S=0 1 V T 0 0<br />

T=1 1 R S 1 0<br />

V=1 0 R S 0 0<br />

St<strong>at</strong>e<br />

Q A Q B<br />

St<strong>at</strong>e Q A + QB +<br />

I=0 I=1<br />

Output Z<br />

I=0 I=1<br />

R=0 0 V=1 0 T =1 1 0 1<br />

S=0 1 V=1 0 T=1 1 0 0<br />

T=1 1 R=0 0 S=0 1 1 0<br />

V=1 0 R=0 0 S=0 1 0 0<br />

Q I<br />

A QB 00<br />

01<br />

11<br />

10<br />

0 1<br />

1<br />

1<br />

0<br />

0<br />

D A= Q A<br />

1<br />

1<br />

0<br />

0<br />

D A =Q A +<br />

Q I<br />

A QB 00<br />

01<br />

11<br />

10<br />

0 1<br />

DA Circuit DB Circuit<br />

DA QA I DB QB 0<br />

0<br />

0<br />

0<br />

1<br />

1<br />

1<br />

1<br />

D B=Q B +<br />

D B =I<br />

QB QA Q I<br />

A QB 00<br />

01<br />

11<br />

10<br />

Z Circuit<br />

0 1<br />

© Tom Ray and John Knight April 14, 2003 page 12, <strong>of</strong> 18<br />

I<br />

0<br />

0<br />

1<br />

0<br />

1<br />

0<br />

0<br />

0<br />

Z=Q A Q BI+ Q A Q BI<br />

Z<br />

8)See<br />

booklet

<strong>Carleton</strong> University <strong>Electronics</strong>, 97.267A, B and C Final April 24, 2002<br />

9 St<strong>at</strong>e Reduction<br />

In the st<strong>at</strong>e table below, and using a merge table, find which st<strong>at</strong>es, if any are equivalent.<br />

Make a new st<strong>at</strong>e table with the minimum number <strong>of</strong> st<strong>at</strong>es<br />

. Changed one next st<strong>at</strong>e <strong>of</strong> B and C from original exam to make the problem a little harder.<br />

St<strong>at</strong>e Next St<strong>at</strong>e<br />

I=0 I=1<br />

Output<br />

Z<br />

R E A 1<br />

A E B 0<br />

B A B 0<br />

C E C 0<br />

D C R 0<br />

E D R 0<br />

A<br />

B<br />

C<br />

D<br />

E<br />

A<br />

B<br />

C<br />

D<br />

E<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

Different outputs<br />

A B<br />

E B<br />

E C<br />

E B<br />

C R<br />

E B<br />

D R<br />

E B<br />

E C<br />

A B<br />

C R<br />

A B<br />

D R<br />

A B<br />

C R<br />

E R<br />

D R<br />

E R<br />

D R<br />

C R<br />

R A B C D<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

A B<br />

E C<br />

E C<br />

E B<br />

C R<br />

E B<br />

D R<br />

E B<br />

E C<br />

A B<br />

C R<br />

A B<br />

D R<br />

A B<br />

C R<br />

E R<br />

D R<br />

E R<br />

D R<br />

C R<br />

R A B C D<br />

To merge st<strong>at</strong>es<br />

Must have the same output.<br />

Must have the same next st<strong>at</strong>es<br />

However<br />

They only have to be the same<br />

after all the mergers.<br />

Setting up the merge table<br />

BandAcan merge<br />

only if (A and E)<br />

and (B andC))<br />

are merged.<br />

AandEcan merge<br />

only if (B and R)<br />

and (D and E)<br />

are merged<br />

BandRhave<br />

different outputs!<br />

Thus DandE<br />

are irrelevant<br />

© Tom Ray and John Knight April 14, 2003 page 13, <strong>of</strong> 18

<strong>Carleton</strong> University <strong>Electronics</strong>, 97.267A, B and C Final April 24, 2002<br />

A<br />

B<br />

C<br />

D<br />

E<br />

A<br />

B<br />

C<br />

D<br />

E<br />

A<br />

B<br />

C<br />

D<br />

E<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

A B<br />

E C<br />

E C<br />

E B<br />

C R<br />

E B<br />

D R<br />

E B<br />

E C<br />

A B<br />

C R<br />

A B<br />

D R<br />

A B<br />

C R<br />

E R<br />

D R<br />

E R<br />

D R<br />

C R<br />

R A B C D<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

A B<br />

E C<br />

E C<br />

E B<br />

C R<br />

E B<br />

D R<br />

E B<br />

E C<br />

A B<br />

C R<br />

A B<br />

D R<br />

A B<br />

C R<br />

E R<br />

D R<br />

E R<br />

D R<br />

C R<br />

R A B C D<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

Z=0<br />

Z=1<br />

A B<br />

E C<br />

E C<br />

E B<br />

C R<br />

E B<br />

D R<br />

E B<br />

E C<br />

A B<br />

C R<br />

A B<br />

D R<br />

A B<br />

C R<br />

E R<br />

D R<br />

E R<br />

D R<br />

C R<br />

R A B C D<br />

Gray squares<br />

have been<br />

elimin<strong>at</strong>ed as<br />

merger candid<strong>at</strong>es<br />

on previous<br />

iter<strong>at</strong>ion<br />

D C<br />

E C<br />

E D<br />

D C<br />

© Tom Ray and John Knight April 14, 2003 page 14, <strong>of</strong> 18<br />

E<br />

Three way<br />

merge

<strong>Carleton</strong> University <strong>Electronics</strong>, 97.267A, B and C Final April 24, 2002<br />

C will merge with D, C with E and E with D.<br />

Thus all three can merge into CDE..<br />

Review<br />

St<strong>at</strong>e Next St<strong>at</strong>e<br />

I=0 I=1<br />

OutputZ<br />

R CDE A 1<br />

A CDE B 0<br />

B R B 0<br />

CDE CDE R 0<br />

Assigning Bit-P<strong>at</strong>terns to Difficult St<strong>at</strong>e Graphs By Adding St<strong>at</strong>es<br />

A difficult st<strong>at</strong>e graph<br />

A B K<br />

D<br />

R<br />

Triangular st<strong>at</strong>es connections<br />

like ADR, can never all differ<br />

by only one bit<br />

Here A and R could not be<br />

made adjacent because<br />

<strong>of</strong> the triangle.<br />

00<br />

01<br />

11<br />

10<br />

0 1<br />

A B<br />

D R<br />

Assigning Bit-P<strong>at</strong>terns to St<strong>at</strong>es Using Flow-Through St<strong>at</strong>es.<br />

A difficult st<strong>at</strong>e graph<br />

x,y=1,1<br />

x,y=0,d<br />

A B K<br />

D<br />

xy=1,1<br />

R<br />

Triangular connections<br />

x,y=1,1<br />

K<br />

A B K<br />

© Tom Ray and John Knight April 14, 2003 page 15, <strong>of</strong> 18<br />

D<br />

α<br />

x,y=0,d<br />

A B K<br />

D<br />

x,y=1,1<br />

R<br />

R<br />

Add a temporary<br />

st<strong>at</strong>e α to elimin<strong>at</strong>e<br />

the triangle<br />

Since x,y=1,1 sends both R and<br />

D to A, let R flow through D.<br />

(D acts as a transient st<strong>at</strong>e)<br />

00<br />

01<br />

11<br />

10<br />

The new st<strong>at</strong>e<br />

assignment<br />

without races<br />

00<br />

01<br />

11<br />

10<br />

0 1<br />

A D<br />

α R<br />

B<br />

0 1<br />

A<br />

B K<br />

R<br />

D<br />

K<br />

Race free<br />

Assignment

12%<br />

<strong>Carleton</strong> University <strong>Electronics</strong>, 97.267A, B and C Final April 24, 2002<br />

10 Race-Free St<strong>at</strong>e Assignment. (Do either question 10 or 11 but not both.)<br />

For the following st<strong>at</strong>e table, revise the table and select a race-free assignment<br />

.Do not change the machine any more than necessary.<br />

Keep R as st<strong>at</strong>e 001.<br />

Do not increase the number <strong>of</strong> rows in the table. Do not merge st<strong>at</strong>es.<br />

Enter all <strong>of</strong> your answers below --- means “don’t care”<br />

.<br />

St<strong>at</strong>e Next<br />

St<strong>at</strong>e,<br />

Input<br />

XY=00<br />

Next<br />

St<strong>at</strong>e,<br />

Input<br />

XY=01<br />

Next<br />

St<strong>at</strong>e,<br />

Input<br />

XY=11<br />

Next<br />

St<strong>at</strong>e,<br />

Input<br />

XY=10<br />

A --- A A B<br />

B E --- --- B<br />

C C A C B<br />

D C D R D<br />

E E D C E<br />

R NotC<br />

Allowed<br />

A R D<br />

St<strong>at</strong>e Next<br />

St<strong>at</strong>e,<br />

Input<br />

XY=00<br />

Next<br />

St<strong>at</strong>e,<br />

Input<br />

XY=01<br />

Next<br />

St<strong>at</strong>e,<br />

Input<br />

XY=11<br />

Next<br />

St<strong>at</strong>e,<br />

Input<br />

XY=10<br />

A --- A A B<br />

B E --- --- B<br />

C C A C B<br />

D C D R D<br />

E E D C E<br />

R C A R D<br />

B<br />

C<br />

A R<br />

© Tom Ray and John Knight April 14, 2003 page 16, <strong>of</strong> 18<br />

C<br />

Assign st<strong>at</strong>es<br />

on map.<br />

Circle stable st<strong>at</strong>es<br />

Identify allowed<br />

st<strong>at</strong>e transitions<br />

Make graph<br />

<strong>of</strong> allowed<br />

transitions<br />

B<br />

C<br />

E<br />

A R<br />

C<br />

D<br />

Trytogetrid<strong>of</strong><br />

triangles.<br />

D<br />

B E<br />

Use transient st<strong>at</strong>es<br />

to avoid races.<br />

00<br />

01<br />

11<br />

10<br />

0 1<br />

A<br />

R<br />

C D<br />

B E

12%<br />

.025%<br />

<strong>Carleton</strong> University <strong>Electronics</strong>, 97.267A, B and C Final April 24, 2002<br />

Answer: Fill in the st<strong>at</strong>e table. Use letters to represent st<strong>at</strong>es, as above.<br />

Write your st<strong>at</strong>e assignmnt in a table (K-map).<br />

St<strong>at</strong>e Next St<strong>at</strong>e,<br />

Input<br />

XY=00<br />

Next St<strong>at</strong>e,<br />

Input<br />

XY=01<br />

Next St<strong>at</strong>e,<br />

Input<br />

XY=11<br />

Next St<strong>at</strong>e,<br />

Input<br />

XY=10<br />

A A=000 A=000 C=010<br />

B E=111 C=010 B=110<br />

C C=010 A=000 C=010 B=110<br />

D D=011 D=011 R=001 D=011<br />

E E=111 D=011 B=110 E=111<br />

R C=010 A=000 R=001 D=011<br />

11 Race-Free St<strong>at</strong>e Assignment. (Do either question 10 or 11 but not both.)<br />

A master-slave D flip-flop can be made differently than was shown in the notes.<br />

a) Find the best place(s) to break the circuit for analyze. Try to use the minimum<br />

number <strong>of</strong> breaks.<br />

z<br />

b) Label the next-st<strong>at</strong>e/st<strong>at</strong>e variables across breaks like this<br />

c) Derive the equ<strong>at</strong>ions rel<strong>at</strong>ing the variable on the left side <strong>of</strong> the break to the inputs and the<br />

variables on the right hand side <strong>of</strong> the break. Make appropri<strong>at</strong>e circuit simplific<strong>at</strong>ions graphically.<br />

+<br />

Z<br />

C<br />

D<br />

C<br />

D<br />

E<br />

N<br />

M<br />

F<br />

E<br />

N<br />

M<br />

F<br />

C<br />

m M +<br />

N<br />

C<br />

© Tom Ray and John Knight April 14, 2003 page 17, <strong>of</strong> 18<br />

C<br />

M<br />

N<br />

C<br />

V<br />

P<br />

W<br />

V<br />

P<br />

W<br />

q +<br />

00<br />

01<br />

11<br />

10<br />

0 1<br />

A R<br />

C D<br />

B E<br />

Q<br />

Q P<br />

Q<br />

Q P

.025%<br />

<strong>Carleton</strong> University <strong>Electronics</strong>, 97.267A, B and C Final April 24, 2002<br />

C<br />

D<br />

C<br />

D<br />

E<br />

N<br />

M<br />

F<br />

E=C+D<br />

N<br />

M<br />

F=DC<br />

m +<br />

C<br />

N=M+DC<br />

C<br />

M<br />

N<br />

C<br />

M<br />

When 2002 is written in binary, wh<strong>at</strong> will the least significant bit be?_______<br />

Have a good summer! Even numbers end in 0.<br />

© Tom Ray and John Knight April 14, 2003 page 18, <strong>of</strong> 18<br />

C<br />

V<br />

P<br />

W<br />

V=M+C<br />

Q<br />

W=CN<br />

Q<br />

Q P<br />

P<br />

q +<br />

Q<br />

P=Q+W=Q+CN<br />

m+=(M + F)(C + D) = (M + DC)(C + D) = MC+ MD + DC = MC + DC (concensus)<br />

q + = (Q+W)(C+M) = (Q+CN)(C+M) = QC+QM+CNM) = QC+QM+C(M+DC)M<br />

=QC+QM+CM=QC+CM (concensus)<br />

Note