AN-9732 - Fairchild Semiconductor

AN-9732 - Fairchild Semiconductor

AN-9732 - Fairchild Semiconductor

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>AN</strong>-<strong>9732</strong> APPLICATION NOTE<br />

2.<br />

5 115mho<br />

fI<br />

<br />

V 2<br />

C<br />

f<br />

CP<br />

OUT<br />

<br />

2<br />

R<br />

COMP<br />

GM 115 mho<br />

COMP,<br />

LF<br />

1<br />

C<br />

COMP,<br />

HF<br />

[ Hz]<br />

[ Hz]<br />

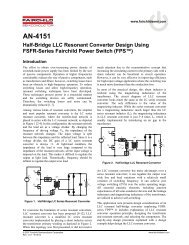

Figure 27. Compensation Network<br />

(31)<br />

The feedback resistor is chosen to scale down the output<br />

voltage to meet the internal reference voltage:<br />

R<br />

R<br />

FB1<br />

FB1<br />

R<br />

FB2<br />

V<br />

OUT<br />

2.<br />

5V<br />

(32)<br />

Typically, high RFB1 is used to reduce power consumption<br />

and, at the same time, CFB can be added to raise the noise<br />

immunity. The maximum CFB currently used is several nano<br />

farads. Adding a capacitor at the feedback loop introduces a<br />

pole as:<br />

f<br />

FP<br />

<br />

2<br />

<br />

1<br />

<br />

2<br />

R<br />

1<br />

R// R <br />

FB1<br />

FB2<br />

C<br />

FB<br />

where R// R <br />

FB1<br />

FB2<br />

C<br />

[ Hz]<br />

FB<br />

RFB1<br />

RFB2<br />

FB2<br />

<br />

RFB1<br />

RFB2<br />

(33)<br />

Though RFB1 is high, pole frequency made by the<br />

synthesized total resistance and several nano farads is<br />

several kilo hertz and rarely affects control-loop response.<br />

The procedure to design the feedback loop is:<br />

a. Determine the crossover frequency (fC) around<br />

1/10~1/5 of line frequency. Since the control-tooutput<br />

transfer function of the power stage has<br />

-20dB/dec slope and -90 o phase at the crossover<br />

frequency, as shown in Figure 28; it is required to<br />

place the zero of the compensation network (fCZ)<br />

around the crossover frequency so 45 phase<br />

margin is obtained. The capacitor CCOMP,LF is<br />

determined as:<br />

V <br />

2<br />

KSAW<br />

LINE 2.<br />

5 115mho<br />

CCOMP,<br />

LF [ f ]<br />

2<br />

2 (34)<br />

2VOUT<br />

L<br />

COUT2fC<br />

To place the compensation zero at the crossover<br />

frequency, the compensation resistor is obtained as:<br />

1<br />

<br />

2<br />

f C<br />

© 2011 <strong>Fairchild</strong> <strong>Semiconductor</strong> Corporation www.fairchildsemi.com<br />

Rev. 1.0.0 • 3/23/11 14<br />

R<br />

COMP<br />

C<br />

COMP,<br />

LF<br />

[ ]<br />

(35)<br />

b. Place this compensator high-frequency pole (fCP) at<br />

least a decade higher than fC to ensure that it does<br />

not interfere with the phase margin of the voltage<br />

regulation loop at its crossover frequency. It should<br />

also be sufficiently lower than the switching<br />

frequency of the converter for noise to be<br />

effectively attenuated. The capacitor CCOMP,HF is<br />

determined as:<br />

C<br />

COMP,<br />

HF<br />

1<br />

[ ]<br />

(36)<br />

2<br />

f R<br />

CP<br />

COMP<br />

Figure 28. Compensation Network Design