Introduction to the Altera Nios II Soft Processor - FTP - Altera

Introduction to the Altera Nios II Soft Processor - FTP - Altera

Introduction to the Altera Nios II Soft Processor - FTP - Altera

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>Altera</strong>’s <strong>Nios</strong> <strong>II</strong> is a soft processor, defined in a hardware description language, which can be implemented in<br />

<strong>Altera</strong>’s FPGA devices by using <strong>the</strong> Quartus R○ <strong>II</strong> CAD system. This tu<strong>to</strong>rial provides a basic introduction <strong>to</strong> <strong>the</strong><br />

<strong>Nios</strong> <strong>II</strong> processor, intended for a user who wishes <strong>to</strong> implement a <strong>Nios</strong> <strong>II</strong> based system on <strong>the</strong> <strong>Altera</strong> DE2 board.<br />

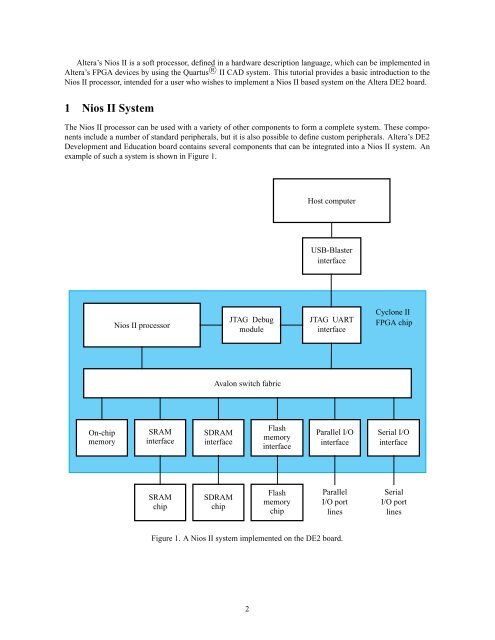

1 <strong>Nios</strong> <strong>II</strong> System<br />

The <strong>Nios</strong> <strong>II</strong> processor can be used with a variety of o<strong>the</strong>r components <strong>to</strong> form a complete system. These components<br />

include a number of standard peripherals, but it is also possible <strong>to</strong> define cus<strong>to</strong>m peripherals. <strong>Altera</strong>’s DE2<br />

Development and Education board contains several components that can be integrated in<strong>to</strong> a <strong>Nios</strong> <strong>II</strong> system. An<br />

example of such a system is shown in Figure 1.<br />

Host computer<br />

USB-Blaster<br />

interface<br />

<strong>Nios</strong> <strong>II</strong> processor<br />

JTAG Debug<br />

module<br />

JTAG UART<br />

interface<br />

Cyclone <strong>II</strong><br />

FPGA chip<br />

Avalon switch fabric<br />

On-chip<br />

memory<br />

SRAM<br />

interface<br />

SDRAM<br />

interface<br />

Flash<br />

memory<br />

interface<br />

Parallel I/O<br />

interface<br />

Serial I/O<br />

interface<br />

SRAM<br />

chip<br />

SDRAM<br />

chip<br />

Flash<br />

memory<br />

chip<br />

Parallel<br />

I/O port<br />

lines<br />

Serial<br />

I/O port<br />

lines<br />

Figure 1. A <strong>Nios</strong> <strong>II</strong> system implemented on <strong>the</strong> DE2 board.<br />

2