Reduction of THD in Diode Clamped Multilevel Inverter ... - Ijsrp.org

Reduction of THD in Diode Clamped Multilevel Inverter ... - Ijsrp.org

Reduction of THD in Diode Clamped Multilevel Inverter ... - Ijsrp.org

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

International Journal <strong>of</strong> Scientific and Research Publications, Volume 3, Issue 6, June 2013 4<br />

ISSN 2250-3153<br />

any multilevel <strong>in</strong>verter configurations and we can generalize this<br />

method to any higher order <strong>in</strong>verters.<br />

REFERENCES<br />

Fig. 5.4 The reference (cos<strong>in</strong>e) and carrier waves (triangular) for a five-level<br />

NPCMLI with SPWM.<br />

Fig. 5.5 The reference (cos<strong>in</strong>e) and carrier waves (triangular) for a five-level<br />

NPCMLI with SPWM.<br />

[1] J. Rodriguez, J. S. Lai, and F. Z. Peng, “<strong>Multilevel</strong> <strong>in</strong>verters: A survey <strong>of</strong><br />

topologies, controls, and applications,” IEEE Trans. Ind. Electron., vol. 49, no.<br />

4, pp. 724–738, Aug. 2002.<br />

[2] T.Ohnishi and H.Okitsu, “A novel PWM technique for three-phase<br />

<strong>in</strong>verter/converter,” International Power Electronics Conference, 1983, pp.384-<br />

395.<br />

[3] A. Nabae, I. Takahashi, and H. Akagi, “A new neutral-po<strong>in</strong>t clamped PWM<br />

<strong>in</strong>verter,” IEEE Trans. Ind. Applicat., vol. IA-17, pp. 518–523, Sept./Oct. 1981.<br />

[4] N. Celanovic and D. Boroyevic, “A fast space vector modulation algorithm<br />

for multilevel three-phase converters,” <strong>in</strong> Conf. Rec. IEEE-IAS Annu. Meet<strong>in</strong>g,<br />

Phoenix, AZ, Oct. 1999, pp. 1173–1177.<br />

[5] J. Rodríguez, P. Correa, and L. Morán, “A vector control technique for<br />

medium voltage multilevel <strong>in</strong>verters,” <strong>in</strong> Proc. IEEE APEC, Anaheim, CA, Mar.<br />

2001, pp. 173–178.<br />

[6] P. Hammond, “A new approach to enhance power quality for medium voltage<br />

ac drives,” IEEE Trans. Ind. Applicat., vol. 33, pp. 202–208, Jan./Feb. 1997.<br />

[7] L. Tolbert and T. G. Habetler, “Novel multilevel <strong>in</strong>verter carrier-based PWM<br />

method,” IEEE Trans. Ind. Applicat., vol. 35, pp. 1098–1107, Sept./Oct. 1999.<br />

[8] B. N. Mw<strong>in</strong>yiwiwa, Z.Wolanski, and B. T. Ooi, “Microprocessor<br />

implemented SPWM for multiconverters with phase-shifted triangle carriers,” <strong>in</strong><br />

Conf. Rec. IEEE-IAS Annu. Meet<strong>in</strong>g, NewOrleans, LA, Oct. 1997, pp. 1542–<br />

1549.<br />

[9] V. G. Agelidis and M. Calais, “Application specific harmonic performance<br />

evaluation <strong>of</strong> multicarrier PWM techniques,” <strong>in</strong> Proc. IEEE PESC’98, Fukuoka,<br />

Japan, May 1998, pp. 172–178.<br />

[10] W. A. Hill and C. D. Harbourt, “Performance <strong>of</strong> medium voltage multilevel<br />

<strong>in</strong>verters,” <strong>in</strong> Conf. Rec. IEEE-IAS Annu. Meet<strong>in</strong>g, Pheonix, AZ, Oct. 1999, pp.<br />

1186–1192.<br />

[11] Carrara, G.,Gardella, S.G., Archesoni,M., Salutari, R., and Sciutto,<br />

G.: ‘A new multi-level PWM method: A theoretical analysis’, IEEE Trans.<br />

Power Electron., 1992, 7, (3), pp. 497–505<br />

[12] McGrath, B.P.; Holmes, D.G.; "Multicarrier PWM strategies for multilevel<br />

<strong>in</strong>verters," Industrial Electronics, IEEE Transactions on, vol.49, no.4, pp. 858-<br />

867, Aug 2002 doi: 10.1109/TIE.2002.801073<br />

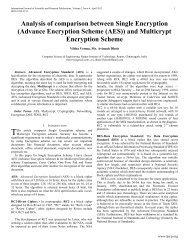

Fig. 5.6 <strong>THD</strong> spectrum for a three-level NPCMLI with SPWM<br />

TABLE II. REDUCTION OF <strong>THD</strong> BY VARYING INVERTER LEVEL<br />

Output Voltage level<br />

<strong>of</strong> NPCI<br />

<strong>THD</strong><br />

Fundamental<br />

Component<br />

Three Level 34.51% 84.45<br />

Five Level 16.82% 347<br />

VII. CONCLUSION<br />

A classical SPWM technique is proposed for three-level<br />

and five-level NPC <strong>in</strong>verter. The ma<strong>in</strong> feature <strong>of</strong> the modulation<br />

scheme lies <strong>in</strong> its ability to elim<strong>in</strong>ate the harmonics <strong>in</strong> the<br />

<strong>in</strong>verter output voltages. To assist the analysis and design <strong>of</strong> the<br />

classical scheme, the mechanism <strong>of</strong> the <strong>THD</strong> reduction with<br />

<strong>in</strong>crease <strong>in</strong> level <strong>of</strong> <strong>in</strong>verter employ<strong>in</strong>g SPWM technique is<br />

discussed.<br />

The harmonic content and <strong>THD</strong> <strong>of</strong> the <strong>in</strong>verter output voltage<br />

produced by the three and five levels are compared and it<br />

seamless for five level neutral po<strong>in</strong>t clamped <strong>in</strong>verter compared<br />

to three level NPCI. The proposed technique can be applied to<br />

www.ijsrp.<strong>org</strong>