- Page 1 and 2: Intel ® HD Graphics OpenSource PRM

- Page 3 and 4: Revision History Document Number Re

- Page 5 and 6: 2.9 Refresh Rate Hardware Control R

- Page 7 and 8: 1.1.1 Terminology Description Softw

- Page 9 and 10: Enable panel power as needed to ret

- Page 11 and 12: 2. North Shared Functions (40000h-

- Page 13 and 14: VGACNTRL—VGA Display Plane Contro

- Page 15 and 16: 2.2 Sine ROM Registers 2.2.1 SINE_R

- Page 17 and 18: DE_POWER1 - Display Engine Power Re

- Page 19 and 20: DE_POWER1 - Display Engine Power Re

- Page 21 and 22: DPFC_CONTROL— DPFC Control Bit De

- Page 23 and 24: DPFC_CONTROL— DPFC Control 24:16

- Page 25 and 26: 2.4.3 DPFC_RECOMP_CTL — DPFC ReCo

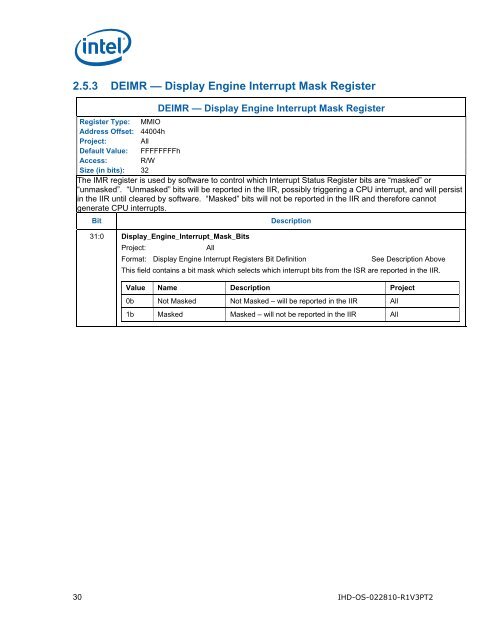

- Page 27 and 28: 2.5 Interrupt Control Registers 2.5

- Page 29: Display Engine Interrupt Registers

- Page 33 and 34: 2.5.6 GT Interrupt Registers Bit De

- Page 35 and 36: GT Interrupt Registers Bit Definiti

- Page 37 and 38: 2.5.7 GTISR — GT Interrupt Status

- Page 39 and 40: 2.5.10 GTIER — GT Interrupt Enabl

- Page 41 and 42: 2.5.12 PMISR — PM Interrupt Statu

- Page 43 and 44: 2.5.15 PMIER — Power Management I

- Page 45 and 46: 2.5.17 GTT Fault Status Register Re

- Page 47 and 48: GTT Fault Status Register 0 Primary

- Page 49 and 50: 2.7 Display Arbitration Control 2.7

- Page 51 and 52: DISP_ARB_CTL—Display Arbiter Cont

- Page 53 and 54: 2.8 Display Watermark Registers The

- Page 55 and 56: 2.8.3 WM1—Low Power 1 Display Wat

- Page 57 and 58: WM3—Low Power 3 Display Watermark

- Page 59 and 60: 2.10 Backlight Control and Modulati

- Page 61 and 62: 2.10.3 BLM_HIST_CTL—Image Enhance

- Page 63 and 64: BLM_HIST_CTL—Image Enhancement Hi

- Page 65 and 66: 2.10.5 Histogram Threshold Guardban

- Page 67 and 68: MBM_CTRL—MBM Control 28:27 MBM_Su

- Page 69 and 70: 2.12 Color Conversion & Control Reg

- Page 71 and 72: 2.12.1 Pipe A Color Control 2.12.1.

- Page 73 and 74: 2.12.1.4 CSC_A_Coefficients 4 CSC_A

- Page 75 and 76: CSC_A_Mode 2 CSC_Black_Screen_Offse

- Page 77 and 78: 2.12.1.10 Pre-CSC_A Low Color Chann

- Page 79 and 80: 2.12.2.4 CSC_B_Coefficients 4 CSC_B

- Page 81 and 82:

CSC_B_Mode 2 CSC_Black_Screen_Offse

- Page 83 and 84:

2.12.2.10 Pre-CSC_B Low Color Chann

- Page 85 and 86:

2.13.2 LGC_PALETTE_B—Pipe B Legac

- Page 87 and 88:

PREC_PALETTE_A—Pipe A Precision D

- Page 89 and 90:

2.13.5 PIPEAGCMAX—Pipe A Gamma Co

- Page 91 and 92:

2.14.2 GT Scratchpad GT Scratchpad

- Page 93 and 94:

3.1.1.2 HBLANK_A—Pipe A Horizonta

- Page 95 and 96:

3.1.1.4 VTOTAL_A—Pipe A Vertical

- Page 97 and 98:

VSYNC_A—Pipe A Vertical Sync Regi

- Page 99 and 100:

3.1.2 Pipe A M/N Values Calculation

- Page 101 and 102:

3.1.2.3 PipeADataN2— Pipe A Data

- Page 103 and 104:

3.1.2.6 PipeADPLinkM2— Pipe A Lin

- Page 105 and 106:

3.1.3.2 PipeBDataN1— Pipe B Data

- Page 107 and 108:

3.1.3.6 PipeBDPLinkN1— Pipe B Lin

- Page 109 and 110:

PFA_PWR_GATE_CTRL—Panel Fitter A

- Page 111 and 112:

PFB_PWR_GATE_CTRL—Panel Fitter B

- Page 113 and 114:

PFA_WIN_POS—Panel Fitter A Window

- Page 115 and 116:

3.1.4.4 PF_CTRL_1—Panel Fitter Co

- Page 117 and 118:

PFB_CTRL_1—Panel Fitter B Control

- Page 119 and 120:

Panel Fitter Coefficient Definition

- Page 121 and 122:

PFB_HFILTL_COEF—Panel Fitter B Ho

- Page 123 and 124:

3.1.7.1 PF_VFILTL_COEF—Panel Fitt

- Page 125 and 126:

4. Plane Controls (70000h-7FFFFh) 4

- Page 127 and 128:

PIPEA_SLC—Pipe A Display Scan Lin

- Page 129 and 130:

PIPEACONF—Pipe A Configuration Re

- Page 131 and 132:

PIPEACONF—Pipe A Configuration Re

- Page 133 and 134:

4.1.2 Display Pipeline A Counters a

- Page 135 and 136:

4.1.3 Display Timestamp This regist

- Page 137 and 138:

4.1.4.2 PIPEB_SLC—Pipe B Display

- Page 139 and 140:

PIPEBCONF—Pipe B Configuration Re

- Page 141 and 142:

PIPEBCONF—Pipe B Configuration Re

- Page 143 and 144:

4.1.5 Display Pipeline B Counters a

- Page 145 and 146:

4.1.6.1 CURACNTR—Cursor A Control

- Page 147 and 148:

5 Cursor Mode Select CURACNTR—Cur

- Page 149 and 150:

4.1.6.3 CURAPOS—Cursor A Position

- Page 151 and 152:

4.1.6.5 CURAPALET—Cursor A Palett

- Page 153 and 154:

4.1.7 Cursor B Plane Control Regist

- Page 155 and 156:

4.1.7.2 CURBBASE—Cursor B Base Ad

- Page 157 and 158:

4.1.7.4 CURBPALET—Cursor B Palett

- Page 159 and 160:

DSPACNTR—Primary A Control Regist

- Page 161 and 162:

DSPACNTR—Primary A Control Regist

- Page 163 and 164:

4.1.8.3 DSPASTRIDE—Primary A Stri

- Page 165 and 166:

4.1.8.5 DSPATILEOFF—Primary A Til

- Page 167 and 168:

DSPBCNTR—Primary B Control Regist

- Page 169 and 170:

DSPBCNTR—Primary B Control Regist

- Page 171 and 172:

DSPBSTRIDE—Primary B Stride Regis

- Page 173 and 174:

4.1.10 Video Sprite A Control Two v

- Page 175 and 176:

DVSACNTR—Video Sprite A Control R

- Page 177 and 178:

DVSACNTR—Video Sprite A Control R

- Page 179 and 180:

SPRITE YUV Y1 U Y2 V YUV 4:2:2 YUYV

- Page 181 and 182:

4.1.10.4 DVSAPOS—Video Sprite A P

- Page 183 and 184:

4.1.10.6 DVSAKEYVAL—Video Sprite

- Page 185 and 186:

4.1.10.8 DVSASURF—Video Sprite A

- Page 187 and 188:

DVSATILEOFF—Video Sprite A Tiled

- Page 189 and 190:

DVSASCALE—Video Sprite A Scaler C

- Page 191 and 192:

These registers are used to determi

- Page 193 and 194:

4.1.11.1 DVSBCNTR—Video Sprite B

- Page 195 and 196:

DVSBCNTR—Video Sprite B Control R

- Page 197 and 198:

DVSBCNTR—Video Sprite B Control R

- Page 199 and 200:

4.1.11.2 DVSBLINOFF—Video Sprite

- Page 201 and 202:

4.1.11.4 DVSBPOS—Video Sprite B P

- Page 203 and 204:

4.1.11.6 DVSBKEYVAL—Video Sprite

- Page 205 and 206:

4.1.11.8 DVSBSURF—Video Sprite B

- Page 207 and 208:

4.1.11.10 DVSBTILEOFF—Video Sprit

- Page 209 and 210:

DVSBSCALE—Video Sprite B Scaler C

- Page 211:

IHD-OS-022810-R1V3PT2 211