Volume 3, Part 2 - Display Registers - Codon.org.uk

Volume 3, Part 2 - Display Registers - Codon.org.uk

Volume 3, Part 2 - Display Registers - Codon.org.uk

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

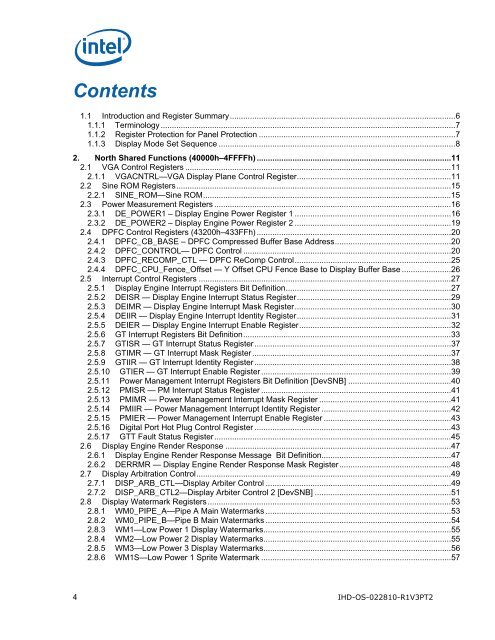

Contents<br />

1.1 Introduction and Register Summary.....................................................................................................6<br />

1.1.1 Terminology ....................................................................................................................................7<br />

1.1.2 Register Protection for Panel Protection ........................................................................................7<br />

1.1.3 <strong>Display</strong> Mode Set Sequence ..........................................................................................................8<br />

2. North Shared Functions (40000h–4FFFFh) .......................................................................................11<br />

2.1 VGA Control <strong>Registers</strong> .......................................................................................................................11<br />

2.1.1 VGACNTRL—VGA <strong>Display</strong> Plane Control Register.....................................................................11<br />

2.2 Sine ROM <strong>Registers</strong>...........................................................................................................................15<br />

2.2.1 SINE_ROM—Sine ROM...............................................................................................................15<br />

2.3 Power Measurement <strong>Registers</strong> ..........................................................................................................16<br />

2.3.1 DE_POWER1 – <strong>Display</strong> Engine Power Register 1 ......................................................................16<br />

2.3.2 DE_POWER2 – <strong>Display</strong> Engine Power Register 2 ......................................................................19<br />

2.4 DPFC Control <strong>Registers</strong> (43200h–433FFh) .......................................................................................20<br />

2.4.1 DPFC_CB_BASE – DPFC Compressed Buffer Base Address....................................................20<br />

2.4.2 DPFC_CONTROL— DPFC Control .............................................................................................20<br />

2.4.3 DPFC_RECOMP_CTL — DPFC ReComp Control......................................................................25<br />

2.4.4 DPFC_CPU_Fence_Offset — Y Offset CPU Fence Base to <strong>Display</strong> Buffer Base ......................26<br />

2.5 Interrupt Control <strong>Registers</strong> .................................................................................................................27<br />

2.5.1 <strong>Display</strong> Engine Interrupt <strong>Registers</strong> Bit Definition..........................................................................27<br />

2.5.2 DEISR — <strong>Display</strong> Engine Interrupt Status Register.....................................................................29<br />

2.5.3 DEIMR — <strong>Display</strong> Engine Interrupt Mask Register......................................................................30<br />

2.5.4 DEIIR — <strong>Display</strong> Engine Interrupt Identity Register.....................................................................31<br />

2.5.5 DEIER — <strong>Display</strong> Engine Interrupt Enable Register....................................................................32<br />

2.5.6 GT Interrupt <strong>Registers</strong> Bit Definition.............................................................................................33<br />

2.5.7 GTISR — GT Interrupt Status Register........................................................................................37<br />

2.5.8 GTIMR — GT Interrupt Mask Register.........................................................................................37<br />

2.5.9 GTIIR — GT Interrupt Identity Register........................................................................................38<br />

2.5.10 GTIER — GT Interrupt Enable Register.....................................................................................39<br />

2.5.11 Power Management Interrupt <strong>Registers</strong> Bit Definition [DevSNB] ..............................................40<br />

2.5.12 PMISR — PM Interrupt Status Register .....................................................................................41<br />

2.5.13 PMIMR — Power Management Interrupt Mask Register ...........................................................41<br />

2.5.14 PMIIR — Power Management Interrupt Identity Register ..........................................................42<br />

2.5.15 PMIER — Power Management Interrupt Enable Register .........................................................43<br />

2.5.16 Digital Port Hot Plug Control Register ........................................................................................43<br />

2.5.17 GTT Fault Status Register..........................................................................................................45<br />

2.6 <strong>Display</strong> Engine Render Response .....................................................................................................47<br />

2.6.1 <strong>Display</strong> Engine Render Response Message Bit Definition..........................................................47<br />

2.6.2 DERRMR — <strong>Display</strong> Engine Render Response Mask Register..................................................48<br />

2.7 <strong>Display</strong> Arbitration Control..................................................................................................................49<br />

2.7.1 DISP_ARB_CTL—<strong>Display</strong> Arbiter Control ...................................................................................49<br />

2.7.2 DISP_ARB_CTL2—<strong>Display</strong> Arbiter Control 2 [DevSNB] .............................................................51<br />

2.8 <strong>Display</strong> Watermark <strong>Registers</strong>.............................................................................................................53<br />

2.8.1 WM0_PIPE_A—Pipe A Main Watermarks ...................................................................................53<br />

2.8.2 WM0_PIPE_B—Pipe B Main Watermarks ...................................................................................54<br />

2.8.3 WM1—Low Power 1 <strong>Display</strong> Watermarks....................................................................................55<br />

2.8.4 WM2—Low Power 2 <strong>Display</strong> Watermarks....................................................................................55<br />

2.8.5 WM3—Low Power 3 <strong>Display</strong> Watermarks....................................................................................56<br />

2.8.6 WM1S—Low Power 1 Sprite Watermark .....................................................................................57<br />

4 IHD-OS-022810-R1V3PT2