Volume 3, Part 2 - Display Registers - Codon.org.uk

Volume 3, Part 2 - Display Registers - Codon.org.uk

Volume 3, Part 2 - Display Registers - Codon.org.uk

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

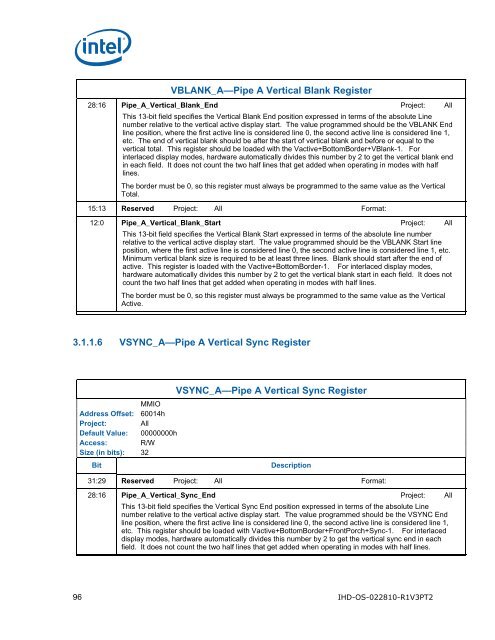

VBLANK_A—Pipe A Vertical Blank Register<br />

28:16 Pipe_A_Vertical_Blank_End Project: All<br />

This 13-bit field specifies the Vertical Blank End position expressed in terms of the absolute Line<br />

number relative to the vertical active display start. The value programmed should be the VBLANK End<br />

line position, where the first active line is considered line 0, the second active line is considered line 1,<br />

etc. The end of vertical blank should be after the start of vertical blank and before or equal to the<br />

vertical total. This register should be loaded with the Vactive+BottomBorder+VBlank-1. For<br />

interlaced display modes, hardware automatically divides this number by 2 to get the vertical blank end<br />

in each field. It does not count the two half lines that get added when operating in modes with half<br />

lines.<br />

The border must be 0, so this register must always be programmed to the same value as the Vertical<br />

Total.<br />

15:13 Reserved Project: All Format:<br />

12:0 Pipe_A_Vertical_Blank_Start Project: All<br />

This 13-bit field specifies the Vertical Blank Start expressed in terms of the absolute line number<br />

relative to the vertical active display start. The value programmed should be the VBLANK Start line<br />

position, where the first active line is considered line 0, the second active line is considered line 1, etc.<br />

Minimum vertical blank size is required to be at least three lines. Blank should start after the end of<br />

active. This register is loaded with the Vactive+BottomBorder-1. For interlaced display modes,<br />

hardware automatically divides this number by 2 to get the vertical blank start in each field. It does not<br />

count the two half lines that get added when operating in modes with half lines.<br />

The border must be 0, so this register must always be programmed to the same value as the Vertical<br />

Active.<br />

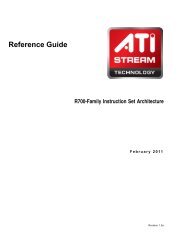

3.1.1.6 VSYNC_A—Pipe A Vertical Sync Register<br />

MMIO<br />

Address Offset: 60014h<br />

Project: All<br />

Default Value: 00000000h<br />

Access: R/W<br />

Size (in bits): 32<br />

Bit<br />

VSYNC_A—Pipe A Vertical Sync Register<br />

Description<br />

31:29 Reserved Project: All Format:<br />

28:16 Pipe_A_Vertical_Sync_End Project: All<br />

This 13-bit field specifies the Vertical Sync End position expressed in terms of the absolute Line<br />

number relative to the vertical active display start. The value programmed should be the VSYNC End<br />

line position, where the first active line is considered line 0, the second active line is considered line 1,<br />

etc. This register should be loaded with Vactive+BottomBorder+FrontPorch+Sync-1. For interlaced<br />

display modes, hardware automatically divides this number by 2 to get the vertical sync end in each<br />

field. It does not count the two half lines that get added when operating in modes with half lines.<br />

96 IHD-OS-022810-R1V3PT2