HW1_VT13 - KTH

HW1_VT13 - KTH

HW1_VT13 - KTH

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Page 4 of 6 Homework Assigment 1 EL2450<br />

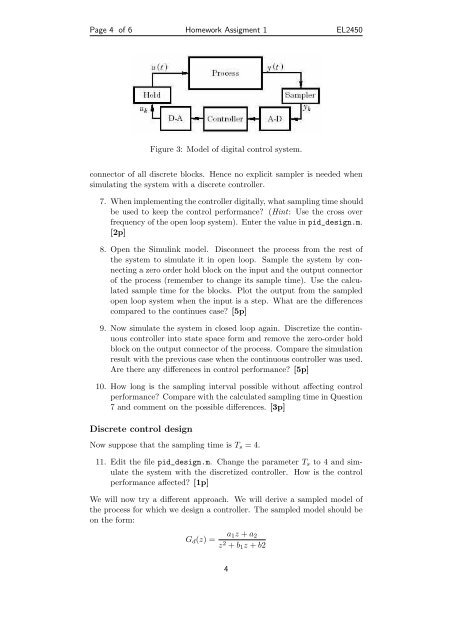

Figure 3: Model of digital control system.<br />

connector of all discrete blocks. Hence no explicit sampler is needed when<br />

simulating the system with a discrete controller.<br />

7. When implementing the controller digitally, what sampling time should<br />

be used to keep the control performance? (Hint: Use the cross over<br />

frequency of the open loop system). Enter the value in pid_design.m.<br />

[2p]<br />

8. Open the Simulink model. Disconnect the process from the rest of<br />

the system to simulate it in open loop. Sample the system by connecting<br />

a zero order hold block on the input and the output connector<br />

of the process (remember to change its sample time). Use the calculated<br />

sample time for the blocks. Plot the output from the sampled<br />

open loop system when the input is a step. What are the differences<br />

compared to the continues case? [5p]<br />

9. Now simulate the system in closed loop again. Discretize the continuous<br />

controller into state space form and remove the zero-order hold<br />

block on the output connector of the process. Compare the simulation<br />

result with the previous case when the continuous controller was used.<br />

Are there any differences in control performance? [5p]<br />

10. How long is the sampling interval possible without affecting control<br />

performance? Compare with the calculated sampling time in Question<br />

7 and comment on the possible differences. [3p]<br />

Discrete control design<br />

Now suppose that the sampling time is T s = 4.<br />

11. Edit the file pid_design.m. Change the parameter T s to 4 and simulate<br />

the system with the discretized controller. How is the control<br />

performance affected? [1p]<br />

We will now try a different approach. We will derive a sampled model of<br />

the process for which we design a controller. The sampled model should be<br />

on the form:<br />

G d (z) = a 1z + a 2<br />

z 2 + b 1 z + b2<br />

4