A Simulator based on QEMU and SystemC for Robustness ... - SEE

A Simulator based on QEMU and SystemC for Robustness ... - SEE

A Simulator based on QEMU and SystemC for Robustness ... - SEE

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

• User mode emulati<strong>on</strong>. In this mode, <strong>QEMU</strong> can launch<br />

processes (not OSes) compiled <strong>for</strong> <strong>on</strong>e CPU <strong>on</strong> another<br />

CPU, whereas compatibility is needed between the applicati<strong>on</strong><br />

<strong>and</strong> the hosting operating system where <strong>QEMU</strong> is<br />

running.<br />

To implement the full system emulati<strong>on</strong>, <strong>QEMU</strong> provides a set<br />

of predefined system plat<strong>for</strong>ms, characterized by a particular<br />

instructi<strong>on</strong> set architecture <strong>and</strong> by a set of emulated devices.<br />

The list of system plat<strong>for</strong>ms includes (but is not limited to) a<br />

PC system <str<strong>on</strong>g>based</str<strong>on</strong>g> <strong>on</strong> the x86 emulator, a PREP or PowerMac<br />

PowerPC system with a PowerPC cpu, a UltraSPARC machine<br />

<str<strong>on</strong>g>based</str<strong>on</strong>g> <strong>on</strong> sparc64, several boards <str<strong>on</strong>g>based</str<strong>on</strong>g> <strong>on</strong> ARM. The emulated<br />

devices available <strong>for</strong> each plat<strong>for</strong>m can be binded to host<br />

devices, redirected to files, or c<strong>on</strong>figured to be accessible from<br />

other processes in the host system, e.g., by sockets.<br />

B. Desyre<br />

The Desyre framework [4] is a <strong>SystemC</strong>-<str<strong>on</strong>g>based</str<strong>on</strong>g> virtual prototyping<br />

envir<strong>on</strong>ment. In this framework, the virtual prototype<br />

is composed of a set of modeling comp<strong>on</strong>ents, instantiated<br />

out of model libraries which may cover functi<strong>on</strong>al <strong>and</strong> architectural<br />

aspects of the system (e.g., protocol models, communicati<strong>on</strong><br />

channels, computati<strong>on</strong>al plat<strong>for</strong>ms). The virtual<br />

prototype is specified as a hierarchical netlist with a set of<br />

parameterized c<strong>on</strong>figurati<strong>on</strong> input files, compliant to the IP-<br />

XACT <strong>for</strong>mat [17]. These files define <strong>and</strong> instantiate the<br />

model comp<strong>on</strong>ents, <strong>and</strong> c<strong>on</strong>nect them together to specify the<br />

model of the entire system. To facilitate the generati<strong>on</strong> of the<br />

system netlists <strong>for</strong> complex designs <strong>and</strong> <strong>for</strong> the design space<br />

explorati<strong>on</strong>, Desyre provides an explorati<strong>on</strong> language (EL) to<br />

describe in a more c<strong>on</strong>cise <strong>for</strong>m, as parameter sets <strong>and</strong> parameter<br />

relati<strong>on</strong>s, the different c<strong>on</strong>figurati<strong>on</strong>s to be simulated.<br />

The EL specificati<strong>on</strong> is used to automatically generate <strong>and</strong><br />

parameterize the IP-XACT file sets, representing the selected<br />

scenarios. The designer has the freedom to run selectively<br />

the simulati<strong>on</strong> of a scenario or of all scenarios as a batch<br />

explorati<strong>on</strong>. A simulati<strong>on</strong> is per<strong>for</strong>med in three phases:<br />

1) Netlist elaborati<strong>on</strong> <strong>and</strong> comp<strong>on</strong>ent loading;<br />

2) Simulati<strong>on</strong>;<br />

3) Data post-processing <strong>and</strong> visualizati<strong>on</strong>.<br />

The first two phases are repeated <strong>for</strong> each of the chosen<br />

scenarios. In the elaborati<strong>on</strong> <strong>and</strong> loading phase, according<br />

to the designer’s netlists, the model builder of DESYRE<br />

dynamically creates in memory the system model by parsing<br />

the IP-XACT files <strong>and</strong> loading the required <strong>SystemC</strong> models<br />

(compiled <strong>and</strong> present in the library). In simulati<strong>on</strong>, the created<br />

system model is executed <strong>and</strong> the output traces are produced.<br />

In the data post-processing, traces are analyzed to aggregate<br />

<strong>and</strong>/or verify the per<strong>for</strong>mance <strong>and</strong> the functi<strong>on</strong>al data.<br />

The dynamic technique <strong>for</strong> the model creati<strong>on</strong> facilitates<br />

the design space explorati<strong>on</strong> by 1) removing the need <strong>for</strong><br />

the compilati<strong>on</strong> of the different <strong>SystemC</strong> netlists (the flow<br />

is compiler free); 2) enabling the designer to quickly derive<br />

additi<strong>on</strong>al scenarios by parameterizing the EL or IP-XACT<br />

files.<br />

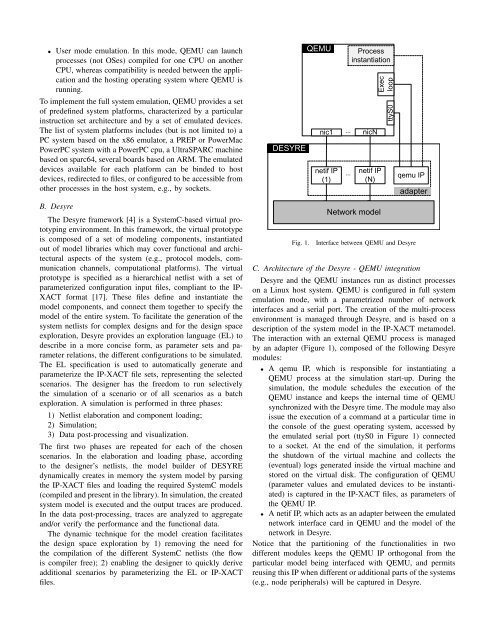

DESYRE<br />

Fig. 1.<br />

<strong>QEMU</strong><br />

nic1<br />

netif IP<br />

(1)<br />

...<br />

Process<br />

instantiati<strong>on</strong><br />

nicN<br />

Exec<br />

loop<br />

ttyS0<br />

... netif IP<br />

qemu IP<br />

(N)<br />

Network model<br />

adapter<br />

Interface between <strong>QEMU</strong> <strong>and</strong> Desyre<br />

C. Architecture of the Desyre - <strong>QEMU</strong> integrati<strong>on</strong><br />

Desyre <strong>and</strong> the <strong>QEMU</strong> instances run as distinct processes<br />

<strong>on</strong> a Linux host system. <strong>QEMU</strong> is c<strong>on</strong>figured in full system<br />

emulati<strong>on</strong> mode, with a parametrized number of network<br />

interfaces <strong>and</strong> a serial port. The creati<strong>on</strong> of the multi-process<br />

envir<strong>on</strong>ment is managed through Desyre, <strong>and</strong> is <str<strong>on</strong>g>based</str<strong>on</strong>g> <strong>on</strong> a<br />

descripti<strong>on</strong> of the system model in the IP-XACT metamodel.<br />

The interacti<strong>on</strong> with an external <strong>QEMU</strong> process is managed<br />

by an adapter (Figure 1), composed of the following Desyre<br />

modules:<br />

• A qemu IP, which is resp<strong>on</strong>sible <strong>for</strong> instantiating a<br />

<strong>QEMU</strong> process at the simulati<strong>on</strong> start-up. During the<br />

simulati<strong>on</strong>, the module schedules the executi<strong>on</strong> of the<br />

<strong>QEMU</strong> instance <strong>and</strong> keeps the internal time of <strong>QEMU</strong><br />

synchr<strong>on</strong>ized with the Desyre time. The module may also<br />

issue the executi<strong>on</strong> of a comm<strong>and</strong> at a particular time in<br />

the c<strong>on</strong>sole of the guest operating system, accessed by<br />

the emulated serial port (ttyS0 in Figure 1) c<strong>on</strong>nected<br />

to a socket. At the end of the simulati<strong>on</strong>, it per<strong>for</strong>ms<br />

the shutdown of the virtual machine <strong>and</strong> collects the<br />

(eventual) logs generated inside the virtual machine <strong>and</strong><br />

stored <strong>on</strong> the virtual disk. The c<strong>on</strong>figurati<strong>on</strong> of <strong>QEMU</strong><br />

(parameter values <strong>and</strong> emulated devices to be instantiated)<br />

is captured in the IP-XACT files, as parameters of<br />

the <strong>QEMU</strong> IP.<br />

• A netif IP, which acts as an adapter between the emulated<br />

network interface card in <strong>QEMU</strong> <strong>and</strong> the model of the<br />

network in Desyre.<br />

Notice that the partiti<strong>on</strong>ing of the functi<strong>on</strong>alities in two<br />

different modules keeps the <strong>QEMU</strong> IP orthog<strong>on</strong>al from the<br />

particular model being interfaced with <strong>QEMU</strong>, <strong>and</strong> permits<br />

reusing this IP when different or additi<strong>on</strong>al parts of the systems<br />

(e.g., node peripherals) will be captured in Desyre.