Technical Reference Manual - Business Support Center - Hewlett ...

Technical Reference Manual - Business Support Center - Hewlett ...

Technical Reference Manual - Business Support Center - Hewlett ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

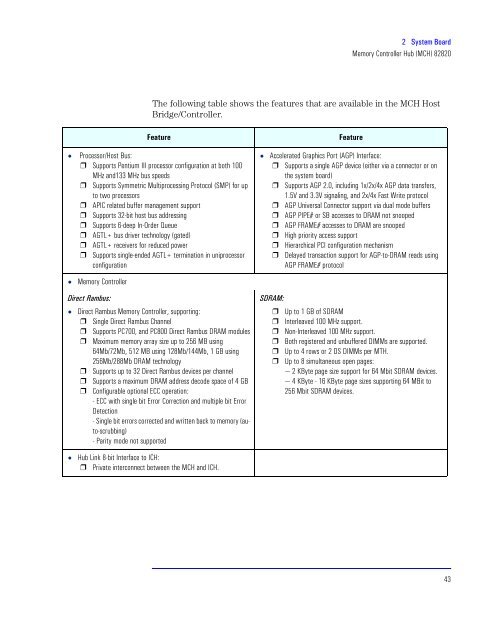

2 System Board<br />

Memory Controller Hub (MCH) 82820<br />

The following table shows the features that are available in the MCH Host<br />

Bridge/Controller.<br />

Feature Feature<br />

• Processor/Host Bus:<br />

❒ <strong>Support</strong>s Pentium III processor configuration at both 100<br />

MHz and133 MHz bus speeds<br />

❒ <strong>Support</strong>s Symmetric Multiprocessing Protocol (SMP) for up<br />

to two processors<br />

❒ APIC related buffer management support<br />

❒ <strong>Support</strong>s 32-bit host bus addressing<br />

❒ <strong>Support</strong>s 6-deep In-Order Queue<br />

❒ AGTL+ bus driver technology (gated)<br />

❒ AGTL+ receivers for reduced power<br />

❒ <strong>Support</strong>s single-ended AGTL+ termination in uniprocessor<br />

configuration<br />

• Memory Controller<br />

Direct Rambus:<br />

• Direct Rambus Memory Controller, supporting:<br />

❒ Single Direct Rambus Channel<br />

❒ <strong>Support</strong>s PC700, and PC800 Direct Rambus DRAM modules<br />

❒ Maximum memory array size up to 256 MB using<br />

64Mb/72Mb, 512 MB using 128Mb/144Mb, 1 GB using<br />

256Mb/288Mb DRAM technology<br />

❒ <strong>Support</strong>s up to 32 Direct Rambus devices per channel<br />

❒ <strong>Support</strong>s a maximum DRAM address decode space of 4 GB<br />

❒ Configurable optional ECC operation:<br />

- ECC with single bit Error Correction and multiple bit Error<br />

Detection<br />

- Single bit errors corrected and written back to memory (auto-scrubbing)<br />

- Parity mode not supported<br />

• Hub Link 8-bit Interface to ICH:<br />

❒ Private interconnect between the MCH and ICH.<br />

• Accelerated Graphics Port (AGP) Interface:<br />

❒ <strong>Support</strong>s a single AGP device (either via a connector or on<br />

the system board)<br />

❒ <strong>Support</strong>s AGP 2.0, including 1x/2x/4x AGP data transfers,<br />

1.5V and 3.3V signaling, and 2x/4x Fast Write protocol<br />

❒ AGP Universal Connector support via dual mode buffers<br />

❒ AGP PIPE# or SB accesses to DRAM not snooped<br />

❒ AGP FRAME# accesses to DRAM are snooped<br />

❒ High priority access support<br />

❒ Hierarchical PCI configuration mechanism<br />

❒ Delayed transaction support for AGP-to-DRAM reads using<br />

AGP FRAME# protocol<br />

SDRAM:<br />

❒ Up to 1 GB of SDRAM<br />

❒ Interleaved 100 MHz support.<br />

❒ Non-Interleaved 100 MHz support.<br />

❒ Both registered and unbuffered DIMMs are supported.<br />

❒ Up to 4 rows or 2 DS DIMMs per MTH.<br />

❒ Up to 8 simultaneous open pages:<br />

— 2 KByte page size support for 64 Mbit SDRAM devices.<br />

— 4 KByte - 16 KByte page sizes supporting 64 MBit to<br />

256 Mbit SDRAM devices.<br />

43