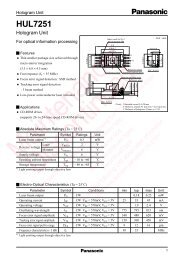

DATA SHEET

DATA SHEET

DATA SHEET

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

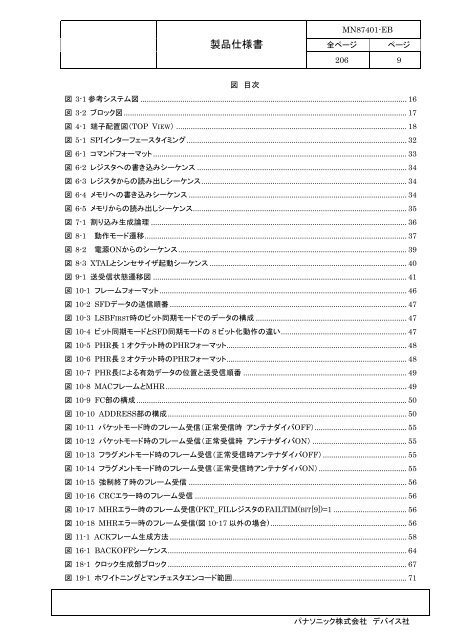

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 9<br />

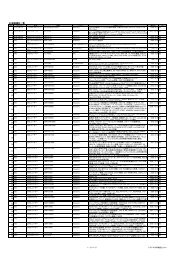

図 目 次<br />

図 3-1 参 考 システム 図 ............................................................................................................................... 16<br />

図 3-2 ブロック 図 ....................................................................................................................................... 17<br />

図 4-1 端 子 配 置 図 (TOP VIEW) .............................................................................................................. 18<br />

図 5-1 SPIインターフェースタイミング......................................................................................................... 32<br />

図 6-1 コマンドフォーマット......................................................................................................................... 33<br />

図 6-2 レジスタへの 書 き 込 みシーケンス .................................................................................................... 34<br />

図 6-3 レジスタからの 読 み 出 しシーケンス.................................................................................................. 34<br />

図 6-4 メモリへの 書 き 込 みシーケンス ........................................................................................................ 34<br />

図 6-5 メモリからの 読 み 出 しシーケンス...................................................................................................... 35<br />

図 7-1 割 り 込 み 生 成 論 理 .......................................................................................................................... 36<br />

図 8-1 動 作 モード 遷 移 ............................................................................................................................. 37<br />

図 8-2 電 源 ONからのシーケンス............................................................................................................. 39<br />

図 8-3 XTALとシンセサイザ 起 動 シーケンス .............................................................................................. 40<br />

図 9-1 送 受 信 状 態 遷 移 図 ......................................................................................................................... 41<br />

図 10-1 フレームフォーマット...................................................................................................................... 46<br />

図 10-2 SFDデータの 送 信 順 番 ................................................................................................................. 47<br />

図 10-3 LSBFIRST 時 のビット 同 期 モードでのデータの 構 成 ........................................................................ 47<br />

図 10-4 ビット 同 期 モードとSFD 同 期 モードの 8 ビット 化 動 作 の 違 い............................................................ 47<br />

図 10-5 PHR 長 1 オクテット 時 のPHRフォーマット...................................................................................... 48<br />

図 10-6 PHR 長 2 オクテット 時 のPHRフォーマット...................................................................................... 48<br />

図 10-7 PHR 長 による 有 効 データの 位 置 と 送 受 信 順 番 .............................................................................. 49<br />

図 10-8 MACフレームとMHR................................................................................................................... 49<br />

図 10-9 FC 部 の 構 成 ................................................................................................................................. 50<br />

図 10-10 ADDRESS 部 の 構 成 .................................................................................................................. 50<br />

図 10-11 パケットモード 時 のフレーム 受 信 ( 正 常 受 信 時 アンテナダイバOFF)............................................ 55<br />

図 10-12 パケットモード 時 のフレーム 受 信 ( 正 常 受 信 時 アンテナダイバON) ............................................. 55<br />

図 10-13 フラグメントモード 時 のフレーム 受 信 ( 正 常 受 信 時 アンテナダイバOFF)........................................ 55<br />

図 10-14 フラグメントモード 時 のフレーム 受 信 ( 正 常 受 信 時 アンテナダイバON).......................................... 55<br />

図 10-15 強 制 終 了 時 のフレーム 受 信 ........................................................................................................ 56<br />

図 10-16 CRCエラー 時 のフレーム 受 信 ..................................................................................................... 56<br />

図 10-17 MHRエラー 時 のフレーム 受 信 (PKT_FILレジスタのFAILTIM(BIT[9])=1 ................................... 56<br />

図 10-18 MHRエラー 時 のフレーム 受 信 ( 図 10-17 以 外 の 場 合 ) ................................................................. 56<br />

図 11-1 ACKフレーム 生 成 方 法 ................................................................................................................. 58<br />

図 16-1 BACKOFFシーケンス.................................................................................................................. 64<br />

図 18-1 クロック 生 成 部 ブロック .................................................................................................................. 67<br />

図 19-1 ホワイトニングとマンチェスタエンコード 範 囲 ................................................................................... 71<br />

パナソニック 株 式 会 社 デバイス 社