DATA SHEET

DATA SHEET

DATA SHEET

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

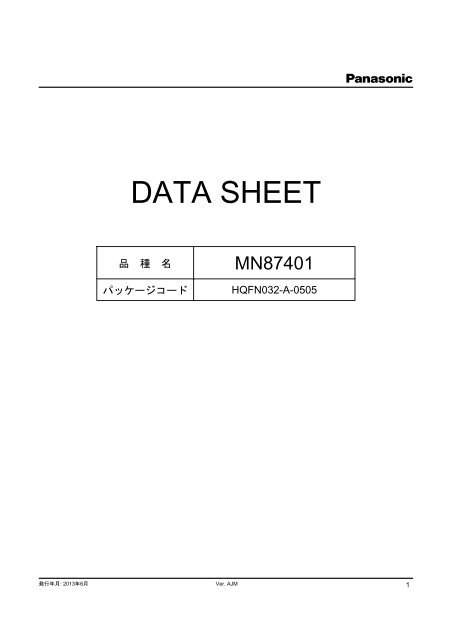

<strong>DATA</strong> <strong>SHEET</strong><br />

品 種 名<br />

パッケージコード<br />

MN87401<br />

HQFN032-A-0505<br />

発 行 年 月 : 2013 年 6 月<br />

Ver. AJM<br />

1

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 3<br />

目 次<br />

1 概 要 ................................................................................................................................................. 14<br />

2 略 語 ................................................................................................................................................. 15<br />

3 参 考 システム 図 とチップブロック 図 ..................................................................................................... 16<br />

4 端 子 説 明 .......................................................................................................................................... 18<br />

4.1 端 子 レイアウト ............................................................................................................................. 18<br />

4.2 端 子 機 能 説 明 .............................................................................................................................. 19<br />

4.2.1 動 作 モード 設 定 用 端 子 ......................................................................................................... 20<br />

4.2.2 ホストインターフェイス 用 端 子 ................................................................................................ 20<br />

4.2.3 GPIO 端 子 ........................................................................................................................... 21<br />

4.2.4 XTAL 端 子 ........................................................................................................................... 22<br />

4.2.5 RF 端 子 ................................................................................................................................ 23<br />

4.2.6 電 源 ..................................................................................................................................... 23<br />

5 電 気 的 特 性 ...................................................................................................................................... 24<br />

5.1 スリープ・アイドル 消 費 電 流 .......................................................................................................... 24<br />

5.2 送 受 信 電 流 ................................................................................................................................. 25<br />

5.3 起 動 時 間 ..................................................................................................................................... 25<br />

5.4 XTAL、シンセサイザ ................................................................................................................... 25<br />

5.5 受 信 特 性 ..................................................................................................................................... 26<br />

5.6 送 信 特 性 ..................................................................................................................................... 29<br />

5.7 アクセサリ 特 性 ............................................................................................................................ 31<br />

5.8 SPIインターフェースACタイミング................................................................................................. 31<br />

6 SPIインターフェイス .......................................................................................................................... 33<br />

6.1 概 要 ............................................................................................................................................ 33<br />

6.2 コマンドフォーマット ...................................................................................................................... 33<br />

6.3 信 号 動 作 ..................................................................................................................................... 33<br />

7 割 り 込 み........................................................................................................................................... 36<br />

8 動 作 モード........................................................................................................................................ 37<br />

8.1 動 作 モード 遷 移 図 ........................................................................................................................ 37<br />

8.2 各 動 作 モードの 説 明 .................................................................................................................... 37<br />

8.2.1 DEEP SLEEPモード........................................................................................................... 37<br />

8.2.2 RESETモード ...................................................................................................................... 37<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 4<br />

8.2.3 SLEEPモード ...................................................................................................................... 38<br />

8.2.4 IDLEモード ......................................................................................................................... 38<br />

8.2.5 RXWAITモード.................................................................................................................... 38<br />

8.2.6 TRXモード........................................................................................................................... 39<br />

9 送 信 、 受 信 の 動 作 モード ................................................................................................................... 41<br />

9.1 各 ステートでの 動 作 説 明 .............................................................................................................. 42<br />

9.1.1 RXWAITステート................................................................................................................. 42<br />

9.1.2 SENSEステート................................................................................................................... 42<br />

9.1.3 TRXステート........................................................................................................................ 42<br />

9.1.4 RSSIステート....................................................................................................................... 42<br />

9.1.5 BKOFF_REQステート......................................................................................................... 42<br />

9.1.6 BKOFFステート .................................................................................................................. 42<br />

9.1.7 T_RXtoTXステート .............................................................................................................. 43<br />

9.1.8 TXステート........................................................................................................................... 43<br />

9.1.9 T_TXtoRXステート .............................................................................................................. 43<br />

9.1.10 WAITACKステート .............................................................................................................. 43<br />

9.1.11 TXDONEステート ............................................................................................................... 43<br />

9.1.12 TXFAILステート.................................................................................................................. 44<br />

9.1.13 RXステート .......................................................................................................................... 44<br />

9.1.14 R_RXtoTXステート.............................................................................................................. 44<br />

9.1.15 TXACKステート................................................................................................................... 44<br />

9.1.16 R_TXtoRXステート.............................................................................................................. 44<br />

9.1.17 RXDONEステート ............................................................................................................... 44<br />

9.1.18 RXFAILステート.................................................................................................................. 45<br />

9.1.19 TESTTXステート................................................................................................................. 45<br />

10 機 能 説 明 ...................................................................................................................................... 46<br />

10.1 対 応 可 能 フレームフォーマット................................................................................................... 46<br />

10.2 プリアンブル............................................................................................................................. 46<br />

10.3 同 期 ........................................................................................................................................ 46<br />

10.3.1 SFD 同 期 モード(SFD sync mode) ....................................................................................... 46<br />

10.3.2 ビット 同 期 モード(bit sync mod)............................................................................................ 47<br />

10.4 PHR ........................................................................................................................................... 47<br />

10.5 MHR .......................................................................................................................................... 49<br />

10.5.1 FC 部 ................................................................................................................................... 50<br />

10.5.2 SQN 部 ................................................................................................................................ 51<br />

10.5.3 ADDRESS 部 ...................................................................................................................... 52<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 5<br />

10.6 CRC............................................................................................................................................ 54<br />

10.7 フレーム 受 信 時 の 割 り 込 み....................................................................................................... 55<br />

11 ハードウェアアクセラレータ ............................................................................................................ 57<br />

11.1 MHRフィルタ............................................................................................................................... 57<br />

11.2 ACK 自 動 送 信 ............................................................................................................................. 58<br />

11.3 ACK 待 ち 受 けと 再 送 機 能 ............................................................................................................ 59<br />

12 BEACON 同 期 機 能 ...................................................................................................................... 59<br />

13 BEACON LOST 検 出 機 能 ........................................................................................................... 59<br />

14 RSSI 機 能 ..................................................................................................................................... 59<br />

14.1 プリアンブル 検 出 時 RSSI ......................................................................................................... 60<br />

14.2 RSSI 計 測 要 求 時 RSSI ................................................................................................................ 60<br />

15 SENSE 機 能 ................................................................................................................................. 62<br />

16 CSMA 機 能 .................................................................................................................................. 62<br />

17 タイマ 機 能 .................................................................................................................................... 64<br />

17.1 BEACON 周 期 タイマ...................................................................................................................... 64<br />

17.2 SUPER FRAME 周 期 タイマ ............................................................................................................ 64<br />

17.3 BACKOFFタイマ ........................................................................................................................ 65<br />

17.4 CAP 期 間 計 測 タイマ .................................................................................................................... 65<br />

17.5 GTSタイマ................................................................................................................................... 65<br />

17.6 IFSタイマ .................................................................................................................................... 65<br />

17.7 ACKタイマ .................................................................................................................................. 65<br />

17.8 MISCタイマ................................................................................................................................. 66<br />

18 クロック 生 成 機 能 .......................................................................................................................... 67<br />

18.1 MACブロッククロック ................................................................................................................... 67<br />

18.2 PHYブロッククロック(TX) ........................................................................................................... 68<br />

18.3 PHYブロッククロック(RX) ........................................................................................................... 68<br />

19 PHY 機 能 ..................................................................................................................................... 69<br />

19.1 概 要 ........................................................................................................................................ 69<br />

19.2 サポート 変 調 モード .................................................................................................................. 69<br />

19.3 データホワイトニングとエンコーディング .................................................................................... 70<br />

19.4 プリアンブル 同 期 ..................................................................................................................... 71<br />

19.5 PHRによるフレーム 長 検 出 .......................................................................................................... 71<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 6<br />

19.6 AFC............................................................................................................................................ 71<br />

19.7 AGC ........................................................................................................................................... 71<br />

19.8 アンテナダイバシティ................................................................................................................ 72<br />

20 送 信 用 フィルタ .............................................................................................................................. 73<br />

21 フレームバッファ............................................................................................................................ 76<br />

21.1 メモリマップ.............................................................................................................................. 76<br />

21.2 送 信 フレームバッファのデータフォーマット ................................................................................ 78<br />

21.3 受 信 フレームバッファのデータフォーマット ................................................................................ 79<br />

22 パケットモードとフラグメントモード .................................................................................................. 80<br />

22.1 パケットモード .......................................................................................................................... 80<br />

22.1.1 パケットモード 送 信 ............................................................................................................... 80<br />

22.1.2 パケットモード 受 信 ............................................................................................................... 80<br />

22.2 フラグメントモード ..................................................................................................................... 81<br />

22.2.1 フラグメントモード 送 信 .......................................................................................................... 81<br />

22.2.2 フラグメントモード 受 信 .......................................................................................................... 82<br />

23 RFパラメータのデータフォーマット.................................................................................................. 85<br />

23.1 RF 設 定 用 パラメータバッファ 領 域 の 設 定 ...................................................................................... 85<br />

23.2 RFパラメータ 格 納 フォーマット ...................................................................................................... 85<br />

23.2.1 コマンドフォーマット .............................................................................................................. 85<br />

23.3 RFパラメータコマンド 一 覧 ( 例 )..................................................................................................... 87<br />

24 バッテリモニタ ............................................................................................................................... 89<br />

25 温 度 センサ ................................................................................................................................... 90<br />

26 XTAL........................................................................................................................................... 91<br />

27 PLLシンセサイザ ......................................................................................................................... 92<br />

27.1 中 心 周 波 数 設 定 例 ................................................................................................................... 93<br />

28 アンテナ 制 御 ................................................................................................................................ 94<br />

29 テスト 信 号 生 成 機 能 ...................................................................................................................... 95<br />

30 アドレスマップ ............................................................................................................................... 96<br />

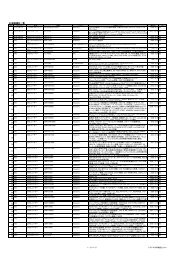

30.1 レジスタマップ .......................................................................................................................... 96<br />

30.2 レジスタ 詳 細 .......................................................................................................................... 103<br />

30.2.1 OPE_MODEレジスタ ........................................................................................................ 103<br />

30.2.2 INTMSKレジスタ .............................................................................................................. 107<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 7<br />

30.2.3 INTCLRレジスタ ............................................................................................................... 109<br />

30.2.4 INTEVENTレジスタ ......................................................................................................... 110<br />

30.2.5 TXFRMCTRレジスタ ........................................................................................................ 114<br />

30.2.6 RXFRMCTRレジスタ ........................................................................................................ 118<br />

30.2.7 STATUS レジスタ ............................................................................................................. 121<br />

30.2.8 BKOFF_CTR レジスタ ..................................................................................................... 122<br />

30.2.9 IFS レジスタ ..................................................................................................................... 124<br />

30.2.10 RXLIM レジスタ ........................................................................................................... 125<br />

30.2.11 SLOT_CTR レジスタ .................................................................................................... 126<br />

30.2.12 TXCLK1 レジスタ ......................................................................................................... 128<br />

30.2.13 TXCLK2 レジスタ ......................................................................................................... 130<br />

30.2.14 SLOTINT レジスタ ....................................................................................................... 131<br />

30.2.15 FIELD_CTR レジスタ................................................................................................... 133<br />

30.2.16 FRM_INF レジスタ....................................................................................................... 136<br />

30.2.17 PKT_FIL レジスタ ........................................................................................................ 138<br />

30.2.18 TIM_MISC レジスタ..................................................................................................... 141<br />

30.2.19 ACC_CNT レジスタ ...................................................................................................... 142<br />

30.2.20 CARRIER_SENSEレジスタ.......................................................................................... 143<br />

30.2.21 MY_PANIDレジスタ...................................................................................................... 145<br />

30.2.22 MYADDR レジスタ ....................................................................................................... 146<br />

30.2.23 MYADDR_S レジスタ ................................................................................................... 147<br />

30.2.24 RF_PARAM_ADDR レジスタ....................................................................................... 148<br />

30.2.25 STAT_CTRL レジスタ................................................................................................... 150<br />

30.2.26 STAT_TXFRM レジスタ ............................................................................................... 151<br />

30.2.27 STAT_RXFRM レジスタ ............................................................................................... 152<br />

30.2.28 STAT_RXACK レジスタ ............................................................................................... 153<br />

30.2.29 STAT_TXACK レジスタ................................................................................................ 154<br />

30.2.30 STAT_TXFAIL レジスタ ............................................................................................... 155<br />

30.2.31 STAT_RXFAIL レジスタ............................................................................................... 156<br />

30.2.32 STAT_PHY_DETSYNC レジスタ................................................................................. 157<br />

30.2.33 STAT_PHY_DETSFD レジスタ.................................................................................... 158<br />

30.2.34 PHY_OP レジスタ......................................................................................................... 159<br />

30.2.35 RXIQ レジスタ .............................................................................................................. 161<br />

30.2.36 PHASE_ADJ1 レジスタ................................................................................................ 162<br />

30.2.37 PHASE_ADJ2 レジスタ................................................................................................ 163<br />

30.2.38 PHRCTR レジスタ ........................................................................................................ 164<br />

30.2.39 SFD レジスタ ................................................................................................................ 165<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 8<br />

30.2.40 SFDTIMEOUT レジスタ .............................................................................................. 166<br />

30.2.41 SYNC_CTR レジスタ .................................................................................................... 167<br />

30.2.42 AGC_CTR レジスタ ...................................................................................................... 169<br />

30.2.43 CCA_CTR レジスタ....................................................................................................... 171<br />

30.2.44 FAFC_OPE1 レジスタ .................................................................................................. 173<br />

30.2.45 FAFC_OPE2 レジスタ .................................................................................................. 174<br />

30.2.46 GFSK_COEF01 レジスタ ............................................................................................. 175<br />

30.2.47 GFSK_COEF23 レジスタ ............................................................................................. 176<br />

30.2.48 GFSK_COEF45 レジスタ ............................................................................................. 177<br />

30.2.49 CHFIL_COEF0-6 レジスタ .......................................................................................... 178<br />

30.2.50 ADC_STABLE レジスタ ............................................................................................... 180<br />

30.2.51 ADC_OFFSET レジスタ ............................................................................................... 181<br />

30.2.52 AFC_COARSE_LOAD レジスタ .................................................................................. 182<br />

30.2.53 AFC_FINE_LOAD レジスタ ........................................................................................ 183<br />

30.2.54 AGC_FILTER0-3 レジスタ ........................................................................................... 184<br />

30.2.55 CLKRCV レジスタ........................................................................................................ 185<br />

30.2.56 SFDTIM_CLKDIV レジスタ........................................................................................ 186<br />

30.2.57 TEST レジスタ .............................................................................................................. 187<br />

30.2.58 DIVER レジスタ............................................................................................................ 189<br />

30.2.59 PERI_CNT1 レジスタ................................................................................................... 191<br />

30.2.60 PERI_CNT2 レジスタ................................................................................................... 193<br />

30.2.61 PERI_CNT3 レジスタ................................................................................................... 194<br />

30.2.62 PERI_CNT4 レジスタ................................................................................................... 195<br />

30.2.63 LBD_TEMP_CTRレジスタ............................................................................................ 196<br />

30.2.64 TX 出 力 パワー 設 定 レジスタ............................................................................................ 197<br />

30.2.65 IREG_CTRレジスタ....................................................................................................... 198<br />

30.2.66 RX_CAL_ENレジスタ.................................................................................................... 199<br />

30.2.67 RX_TUNEレジスタ........................................................................................................ 200<br />

30.2.68 AD_CTRレジスタ........................................................................................................... 201<br />

30.2.69 XO 制 御 レジスタ ............................................................................................................. 202<br />

30.2.70 SYNTH1 レジスタ......................................................................................................... 203<br />

30.2.71 SYNTH2 レジスタ......................................................................................................... 204<br />

30.2.72 TX_TUNEレジスタ........................................................................................................ 205<br />

31 リファレンスデザイン.................................................................................................................... 206<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 9<br />

図 目 次<br />

図 3-1 参 考 システム 図 ............................................................................................................................... 16<br />

図 3-2 ブロック 図 ....................................................................................................................................... 17<br />

図 4-1 端 子 配 置 図 (TOP VIEW) .............................................................................................................. 18<br />

図 5-1 SPIインターフェースタイミング......................................................................................................... 32<br />

図 6-1 コマンドフォーマット......................................................................................................................... 33<br />

図 6-2 レジスタへの 書 き 込 みシーケンス .................................................................................................... 34<br />

図 6-3 レジスタからの 読 み 出 しシーケンス.................................................................................................. 34<br />

図 6-4 メモリへの 書 き 込 みシーケンス ........................................................................................................ 34<br />

図 6-5 メモリからの 読 み 出 しシーケンス...................................................................................................... 35<br />

図 7-1 割 り 込 み 生 成 論 理 .......................................................................................................................... 36<br />

図 8-1 動 作 モード 遷 移 ............................................................................................................................. 37<br />

図 8-2 電 源 ONからのシーケンス............................................................................................................. 39<br />

図 8-3 XTALとシンセサイザ 起 動 シーケンス .............................................................................................. 40<br />

図 9-1 送 受 信 状 態 遷 移 図 ......................................................................................................................... 41<br />

図 10-1 フレームフォーマット...................................................................................................................... 46<br />

図 10-2 SFDデータの 送 信 順 番 ................................................................................................................. 47<br />

図 10-3 LSBFIRST 時 のビット 同 期 モードでのデータの 構 成 ........................................................................ 47<br />

図 10-4 ビット 同 期 モードとSFD 同 期 モードの 8 ビット 化 動 作 の 違 い............................................................ 47<br />

図 10-5 PHR 長 1 オクテット 時 のPHRフォーマット...................................................................................... 48<br />

図 10-6 PHR 長 2 オクテット 時 のPHRフォーマット...................................................................................... 48<br />

図 10-7 PHR 長 による 有 効 データの 位 置 と 送 受 信 順 番 .............................................................................. 49<br />

図 10-8 MACフレームとMHR................................................................................................................... 49<br />

図 10-9 FC 部 の 構 成 ................................................................................................................................. 50<br />

図 10-10 ADDRESS 部 の 構 成 .................................................................................................................. 50<br />

図 10-11 パケットモード 時 のフレーム 受 信 ( 正 常 受 信 時 アンテナダイバOFF)............................................ 55<br />

図 10-12 パケットモード 時 のフレーム 受 信 ( 正 常 受 信 時 アンテナダイバON) ............................................. 55<br />

図 10-13 フラグメントモード 時 のフレーム 受 信 ( 正 常 受 信 時 アンテナダイバOFF)........................................ 55<br />

図 10-14 フラグメントモード 時 のフレーム 受 信 ( 正 常 受 信 時 アンテナダイバON).......................................... 55<br />

図 10-15 強 制 終 了 時 のフレーム 受 信 ........................................................................................................ 56<br />

図 10-16 CRCエラー 時 のフレーム 受 信 ..................................................................................................... 56<br />

図 10-17 MHRエラー 時 のフレーム 受 信 (PKT_FILレジスタのFAILTIM(BIT[9])=1 ................................... 56<br />

図 10-18 MHRエラー 時 のフレーム 受 信 ( 図 10-17 以 外 の 場 合 ) ................................................................. 56<br />

図 11-1 ACKフレーム 生 成 方 法 ................................................................................................................. 58<br />

図 16-1 BACKOFFシーケンス.................................................................................................................. 64<br />

図 18-1 クロック 生 成 部 ブロック .................................................................................................................. 67<br />

図 19-1 ホワイトニングとマンチェスタエンコード 範 囲 ................................................................................... 71<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 10<br />

図 20-1 送 信 用 フィルタブロック(PHY_OPレジスタのGFSKENフィールド(BIT[7])=1 時 )............................ 73<br />

図 20-2 送 信 用 フィルタ 形 状 ....................................................................................................................... 73<br />

図 20-3 送 信 用 フィルタブロック(PHY_OPレジスタのGFSKENフィールド(BIT[7])=0 時 )............................ 74<br />

図 21-1 フレームバッファ 格 納 データ........................................................................................................... 77<br />

図 21-2 INFOフィールドフォーマット .......................................................................................................... 78<br />

図 21-3 MHRが 存 在 する 場 合 のTXフレームバッファへの 格 納 フォーマット................................................. 78<br />

図 21-4 MHRが 存 在 しない 場 合 のTXフレームバッファへの 格 納 フォーマット .............................................. 79<br />

図 21-5 PHRが 付 加 されている 場 合 のRXフレームバッファへの 格 納 フォーマット ........................................ 79<br />

図 22-1 パケットモードの 送 信 シーケンス.................................................................................................... 80<br />

図 22-2 パケットモードの 受 信 シーケンス.................................................................................................... 81<br />

図 22-3 TXFIFO 構 造 ............................................................................................................................... 82<br />

図 22-4 TX 時 のフレームバッファからのデータ 読 み 出 しタイミング............................................................... 82<br />

図 22-5 フラグメントモード(バイト 数 計 測 モード)の 送 信 シーケンス............................................................... 84<br />

図 22-6 フラグメントモード(バイト 数 計 測 モード)の 受 信 シーケンス............................................................... 84<br />

図 26-1 XTAL、TCXO 接 続 図 ................................................................................................................... 91<br />

図 27-1 PLLシンセサイザブロック 概 略 図 .................................................................................................. 92<br />

図 28-1 アンテナ 制 御 方 法 ......................................................................................................................... 94<br />

図 31-1 参 考 回 路 図 (920MHZ)................................................................................................................. 206<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 11<br />

表 目 次<br />

表 4-1 GPIO MUX .................................................................................................................................. 21<br />

表 7-1 割 り 込 み 種 類 .................................................................................................................................. 36<br />

表 8-1 動 作 モード 一 覧 ............................................................................................................................... 39<br />

表 10-1 PHRに 含 まれるデータ.................................................................................................................. 47<br />

表 10-2 ADDRESS 部 設 定 一 覧 ................................................................................................................ 52<br />

表 10-3 フレーム 受 信 時 IRQ 信 号 発 生 タイミング ........................................................................................ 55<br />

表 14-1 RSSI 計 測 時 間 ............................................................................................................................. 61<br />

表 15-1 SENSE 用 RSSI 計 測 時 間 ............................................................................................................. 62<br />

表 18-1 送 信 レートごとのTXCLK1,2 レジスタの 設 定 値 ............................................................................. 68<br />

表 19-1 変 調 モード 設 定 ............................................................................................................................. 69<br />

表 19-2 FSKのレートとMODULATION INDEXの 関 係 ................................................................................. 69<br />

表 19-3 WHITENING 動 作 .......................................................................................................................... 70<br />

表 19-4 アンテナダイバシティモード 設 定 .................................................................................................... 72<br />

表 19-5 送 信 アンテナ 設 定 ......................................................................................................................... 72<br />

表 20-1 設 定 値 とMUL 値 の 関 係 ................................................................................................................ 74<br />

表 20-2 FILTERED-FSK 時 のフィルタ 係 数 の 設 定 例 ................................................................................... 75<br />

表 20-3 FSK 時 のフィルタ 係 数 の 設 定 例 .................................................................................................... 75<br />

表 21-1 フレームバッファマップ、バッファ 名 定 義 ......................................................................................... 76<br />

表 23-1 RFパラメータ 格 納 ポインタ ............................................................................................................ 85<br />

表 23-2 RFパラメータ 格 納 フォーマット ....................................................................................................... 85<br />

表 23-3 コマンドタイプ 1 のRFパラメータコマンドフォーマット ...................................................................... 86<br />

表 23-4 コマンドタイプ 1 の 制 御 内 容 .......................................................................................................... 86<br />

表 23-5 コマンドタイプ 1 の 制 御 内 容 .......................................................................................................... 86<br />

表 23-6 コマンドタイプ 2 のRFパラメータコマンドフォーマット ...................................................................... 87<br />

表 23-7 RF_TXSTART_PARAの 設 定 内 容 ............................................................................................... 87<br />

表 23-8 RF_TXEND_PARAの 設 定 内 容 .................................................................................................. 87<br />

表 23-9 RF_RXSTART_PARAの 設 定 内 容 .............................................................................................. 88<br />

表 23-10 RF_RXEND_PARAの 設 定 内 容 ................................................................................................ 88<br />

表 23-11 RF_RXEN_OFF_PARAの 設 定 内 容 .......................................................................................... 88<br />

表 27-1 PLL 各 BAND 設 定 内 容 .................................................................................................................. 92<br />

表 29-1 テスト 送 信 モード ........................................................................................................................... 95<br />

表 30-1 レジスタマップ............................................................................................................................... 96<br />

表 30-2 OPE_MODEレジスタ................................................................................................................. 103<br />

表 30-3 INTMSKレジスタ....................................................................................................................... 107<br />

表 30-4 INTCLRレジスタ........................................................................................................................ 109<br />

表 30-5 INTEVENTレジスタ.................................................................................................................. 110<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 12<br />

表 30-6 TXFRMCTRレジスタ................................................................................................................. 114<br />

表 30-7 RXFRMCTRレジスタ................................................................................................................. 118<br />

表 30-8 STATUSレジスタ ....................................................................................................................... 121<br />

表 30-9 BKOFF_CTRレジスタ................................................................................................................ 122<br />

表 30-10 IFSレジスタ.............................................................................................................................. 124<br />

表 30-11 RXLIMレジスタ........................................................................................................................ 125<br />

表 30-12 SLOT_CTR ............................................................................................................................. 126<br />

表 30-13 TXCLK1 レジスタ .................................................................................................................... 128<br />

表 30-14 TXCLK2 レジスタ .................................................................................................................... 130<br />

表 30-15 SLOTINTレジスタ ................................................................................................................... 131<br />

表 30-16 FIELD_CTRレジスタ............................................................................................................... 133<br />

表 30-17 FRM _INFレジスタ .................................................................................................................. 136<br />

表 30-18 PKT_FILレジスタ .................................................................................................................... 138<br />

表 30-19 TIM_MISCレジスタ ................................................................................................................. 141<br />

表 30-20 ACC_CNTレジスタ .................................................................................................................. 142<br />

表 30-21 CARRIER_SENSEレジスタ .................................................................................................... 143<br />

表 30-22 MY_PANIDレジスタ ................................................................................................................ 145<br />

表 30-23 MYADDRレジスタ.................................................................................................................... 146<br />

表 30-24 MYADDR_Sレジスタ ............................................................................................................... 147<br />

表 30-25 RF_PARAM_ADDRレジスタ ................................................................................................... 148<br />

表 30-26 STAT_CTRLレジスタ............................................................................................................... 150<br />

表 30-27 STAT_TXFRMレジスタ ........................................................................................................... 151<br />

表 30-28 STAT_RXFRMレジスタ ........................................................................................................... 152<br />

表 30-29 STAT_RXACKレジスタ............................................................................................................ 153<br />

表 30-30 STAT_TXACKレジスタ............................................................................................................ 154<br />

表 30-31 STAT_TXFAILレジスタ ........................................................................................................... 155<br />

表 30-32 STAT_RXFAILレジスタ ........................................................................................................... 156<br />

表 30-33 STAT_PHY_DETSYNCレジスタ............................................................................................. 157<br />

表 30-34 STAT_DETSFDレジスタ.......................................................................................................... 158<br />

表 30-35 PHY_OPレジスタ ..................................................................................................................... 159<br />

表 30-36 RXIQレジスタ........................................................................................................................... 161<br />

表 30-37 PHASE_ADJ1 レジスタ........................................................................................................... 162<br />

表 30-38 PHASE_ADJ2 レジスタ........................................................................................................... 163<br />

表 30-39 PHRCTRレジスタ .................................................................................................................... 164<br />

表 30-40 SFDレジスタ............................................................................................................................. 165<br />

表 30-41 SFDTIMEOUTレジスタ .......................................................................................................... 166<br />

表 30-42 SYNC_CTRレジスタ ................................................................................................................ 167<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 13<br />

表 30-43 AGC_CTRレジスタ................................................................................................................... 169<br />

表 30-44 CCA_CTRレジスタ................................................................................................................... 171<br />

表 30-45 FAFC_OPE1 レジスタ.............................................................................................................. 173<br />

表 30-46 FAFC_OPE2 レジスタ.............................................................................................................. 174<br />

表 30-47 GFSK_COEF01 レジスタ ........................................................................................................ 175<br />

表 30-48 GFSK_COEF23 レジスタ ........................................................................................................ 176<br />

表 30-49 GFSK_COEF45 レジスタ ........................................................................................................ 177<br />

表 30-50 CHFIL_COEF0-6 レジスタ...................................................................................................... 178<br />

表 30-51 ADC_STABLEレジスタ ........................................................................................................... 180<br />

表 30-52 ADC_OFFSETレジスタ ........................................................................................................... 181<br />

表 30-53 AFC_COARSE_LOADレジスタ............................................................................................... 182<br />

表 30-54 AFC_FINE_LOADレジスタ..................................................................................................... 183<br />

表 30-55 AGC_FILTER0-3 レジスタ ...................................................................................................... 184<br />

表 30-56 CLKRCVレジスタ .................................................................................................................... 185<br />

表 30-57 SFDTIM_CLKDIVレジスタ ................................................................................................... 186<br />

表 30-58 TESTレジスタ .......................................................................................................................... 187<br />

表 30-59 DIVERレジスタ........................................................................................................................ 189<br />

表 30-60 PERI_CNT1 レジスタ .............................................................................................................. 191<br />

表 30-61 PERI_CNT2 レジスタ .............................................................................................................. 193<br />

表 30-62 PERI_CNT3 レジスタ .............................................................................................................. 194<br />

表 30-63 PERI_CNT4 レジスタ .............................................................................................................. 195<br />

表 30-64 LBD_TEMP_CTRレジスタ..................................................................................................... 196<br />

表 30-65 TX_SETレジスタ...................................................................................................................... 197<br />

表 30-66 IREG_CTRレジスタ................................................................................................................ 198<br />

表 30-67 RX_CAL_ENレジスタ............................................................................................................. 199<br />

表 30-68 RX_TUNEレジスタ................................................................................................................. 200<br />

表 30-69 AD_CTRレジスタ.................................................................................................................... 201<br />

表 30-70 XO_CTRレジスタ ..................................................................................................................... 202<br />

表 30-71 SYNTH1 レジスタ.................................................................................................................... 203<br />

表 30-72 SYNTH2 レジスタ.................................................................................................................... 204<br />

表 30-73 TX_TUNEレジスタ................................................................................................................. 205<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 14<br />

1 概 要<br />

変 復 調 機 能<br />

169 / 420 - 510 / 863 - 930 MHz<br />

対 応 変 復 調 方 式 : Filtered FSK /FSK 4.8-200kbps<br />

受 信 感 度<br />

-122dBm @ Filtered FSK 4.8kbps 400MHz バンド<br />

-105dBm @ Filtered FSK 100kbps 900MHzバンド<br />

送 信 出 力 制 御<br />

+15 ~ -6dBm (0.2dB step)<br />

消 費 電 流<br />

24 mA @ 送 信 時 (+13dBm / 400MHz band)<br />

12.6 mA @ 受 信 時 (400MHz band)<br />

MAC アクセラレータ 搭 載 (レジスタ 設 定 により 機 能 停 止 可 能 )<br />

ACK 自 動 送 信<br />

再 送 制 御 (ACK フレームが 受 信 できなかった 場 合 )<br />

MAC フレームヘッダフィルタリング,CRC 生 成 とチェック<br />

フレームバッファ<br />

256 バイト ( 送 受 信 別 に 搭 載 )<br />

アクセサリ<br />

温 度 センサ、バッテリモニタ<br />

uC インターフェイス<br />

SPI<br />

GPIO<br />

外 部 FE 制 御 、 汎 用 IO 制 御<br />

パッケージ<br />

QFN 32-pin(5 × 5 mm) Pin ピッチ 0.5mm<br />

動 作 電 圧 範 囲<br />

1.8 - 3.6V<br />

動 作 温 度 範 囲<br />

-40 - 85 ℃<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 15<br />

2 略 語<br />

ACK<br />

AFC<br />

AGC<br />

CAP<br />

CRC<br />

CSMA<br />

FSK<br />

GPIO<br />

IFS<br />

IRQ<br />

LIFS<br />

MAC<br />

MHR<br />

PHR<br />

PHY<br />

PLL<br />

PN<br />

RSSI<br />

RX<br />

SFD<br />

SIFS<br />

SPI<br />

SYNTH<br />

TCXO<br />

TX<br />

uC<br />

XTAL<br />

Acknowledge Frame<br />

Automatic Frequency Control<br />

Automatic Gain Control<br />

Contention Access Period<br />

Cyclic Redundancy Check<br />

Carrier Sense Multiple Access<br />

Frequency Shift Keying<br />

General Purpose InOut<br />

Inter Frame Space<br />

Interupt Request<br />

Long Inter Frame Space<br />

Medium Access Controller<br />

MAC Header<br />

PHY Header<br />

Physical layer<br />

Phase Locked Loop<br />

Pusedo random noise<br />

Received Signal Strength Indication<br />

Receive, Receive Mode<br />

Start Frame Delimiter<br />

Short Inter Frame Space<br />

Serial Peripheral Interface<br />

Synthesizer<br />

Temperature compensated crystal oscillator unit<br />

Transmit, Transmit Mode<br />

Micro-controller<br />

Cyistal<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 16<br />

3 参 考 システム 図 とチップブロック 図<br />

GPIO signals<br />

(ANT & TRX control)<br />

ANT1<br />

(Sub1G)<br />

TX_OUT_10<br />

RX_IN_10P<br />

XOUT<br />

XO<br />

XIN<br />

XBO<br />

GPIO0-7<br />

MN87401<br />

SPI_CSN<br />

uC<br />

RX_IN_10N<br />

SPI_CK<br />

SPI_DI<br />

SPI_DO<br />

IRQ<br />

CHIPEN<br />

VOUT_DIG<br />

VOUT_PLL<br />

VOUT_VCO<br />

VOUT_RX<br />

VSS<br />

TEST2<br />

TEST<br />

図 3-1 参 考 システム 図<br />

本 参 考 システム 図 は 正 確 な 接 続 を 記 載 しているものではありません。 詳 細 な 参 考 回 路 図 は、<br />

図 31-1 を 参 照 ください。<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 17<br />

Sub-GHz<br />

VBAT<br />

Check<br />

Temp.<br />

sensor<br />

ADC<br />

Power controller<br />

VBAT controller<br />

PLL<br />

XO<br />

control<br />

TX<br />

Digital Mod.<br />

to XTAL<br />

from XTAL<br />

Sub-GHz<br />

π/2<br />

ADC<br />

ADC<br />

RX<br />

Digital<br />

Demod.<br />

AFC<br />

AGC<br />

FSK<br />

Hardware<br />

MAC /<br />

Controller<br />

from/to uC<br />

Ant control<br />

GPIO<br />

AGC / RSSI<br />

図 3-2 ブロック 図<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 18<br />

4 端 子 説 明<br />

4.1 端 子 レイアウト<br />

25<br />

26<br />

27<br />

28<br />

29<br />

30<br />

31<br />

32<br />

VOUT_DIG<br />

GPIO0<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

24<br />

23<br />

22<br />

21<br />

20<br />

19<br />

18<br />

17<br />

7<br />

8<br />

GPIO1<br />

GPIO2<br />

GPIO3<br />

GPIO4<br />

GPIO5<br />

GPIO6<br />

TX_OUT_10<br />

VOUT_RX<br />

RX_IN_10P<br />

RX_IN_10N<br />

(open)<br />

(open)<br />

(open)<br />

VBAT<br />

CHIPEN<br />

TEST<br />

(FOR TEST)<br />

(FOR TEST)<br />

XIN<br />

XOUT<br />

TEST2<br />

XBO<br />

裏 面<br />

Vss<br />

16<br />

15<br />

14<br />

13<br />

12<br />

11<br />

10<br />

9<br />

VOUT_PLL<br />

VOUT_VCO<br />

IRQ<br />

SPI_CSN<br />

SPI_DO<br />

SPI_DI<br />

SPI_CK<br />

GPIO7<br />

図 4-1 端 子 配 置 図 (TOP View)<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 19<br />

4.2 端 子 機 能 説 明<br />

No Pin Name I/O Type V 接 続 先 説 明<br />

1 VOUT_DIG O --- 1.2 --- デジタルブロック 用 電 源 出 力<br />

2 GPIO0 I/O D ---<br />

3 GPIO1 I/O D ---<br />

汎 用 デジタル 入 出 力<br />

4 GPIO2 I/O D ---<br />

3.3V インターフェイス<br />

5 GPIO3 I/O D ---<br />

内 部 レジスタ 設 定 により、 外 部 アンプ 部 、ア<br />

6 GPIO4 I/O D ---<br />

ンテナスイッチ 部 を 制 御 するために 用 いるこ<br />

7 GPIO5 I/O D ---<br />

とが 可 能 。<br />

8 GPIO6 I/O D ---<br />

9 GPIO7 I/O D ---<br />

10 SPI_CK I D --- uC<br />

シリアルインターフェイス 用 クロック 入 力<br />

3.3V インターフェイス<br />

11 SPI_DI I D --- uC<br />

シリアルインターフェイス 用 データ 入 力<br />

3.3V インターフェイス<br />

12 SPI_DO O D --- uC<br />

シリアルインターフェイス 用 データ 出 力<br />

3.3V インターフェイス<br />

13 SPI_CSN I D --- uC<br />

シリアルインターフェイス 用 イネーブル<br />

3.3V インターフェイス<br />

14 IRQ O D --- uC<br />

割 り 込 み 通 知<br />

3.3V インターフェイス<br />

15 VOUT_VCO O --- 1.2 --- VCO ブロック 用 電 源 出 力<br />

16 VOUT_PLL O --- 1.2 --- PLL ブロック 用 電 源 出 力<br />

17 VBAT I A 1.8-3.6 Power 電 源 端 子 (1.8~3.6V)<br />

18 --- --- A --- --- 開 放 ( 通 常 動 作 時 )<br />

19 --- --- A --- --- 開 放 ( 通 常 動 作 時 )<br />

20 --- --- A --- --- 開 放 ( 通 常 動 作 時 )<br />

21 RX_IN_10N I A --- ANT サブ GHz バンド 用 RX 負 入 力<br />

22 RX_IN_10P I A --- ANT サブ GHz バンド 用 RX 正 入 力<br />

23 VOUT_RX O - 1.2 --- RX ブロック 用 電 源 出 力<br />

24 TX_OUT_10 O A --- ANT サブ GHz バンド 送 信 用<br />

25 CHIPEN I - --- uC CHIP 動 作 用 イネーブル<br />

26 TEST I D --- for test VSS に 接 続 ( 通 常 動 作 時 )<br />

27 --- --- A --- for test 開 放 ( 通 常 動 作 時 )<br />

28 --- --- A --- for test 開 放 ( 通 常 動 作 時 )<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 20<br />

No Pin Name I/O Type V 接 続 先 説 明<br />

29 XIN I A --- XTAL<br />

30 XOUT O A --- XTAL<br />

26MHz 用 クリスタル<br />

31 TEST2 I D --- for test VSS に 接 続 ( 通 常 動 作 時 )<br />

32 XBO O A 3.3 --- 26MHz 用 リファレンス 出 力<br />

注 意 : VSS 端 子 は、チップ 裏 面 に 配 置 されている。<br />

Type 欄 の A はアナログ 端 子 、D はデジタル 端 子 の 意 味 である。<br />

4.2.1 動 作 モード 設 定 用 端 子<br />

CHIPEN<br />

この 端 子 は、チップ 動 作 の ON/OFF を 設 定 する。この 端 子 が LOW レベルの 場 合 、チップ 内 の 全 レギュ<br />

レータが OFF になり、チップは 完 全 に OFF 状 態 になる。チップを 動 作 状 態 にするためには、この 端 子 を<br />

HIGH レベルにすること。<br />

TEST、TEST2<br />

この 端 子 は、VSS 接 続 にすること。<br />

4.2.2 ホストインターフェイス 用 端 子<br />

SPI_CSN<br />

この 端 子 は、 外 部 uC からの 同 期 シリアルによる 制 御 をイネーブルにする。 外 部 uC は、チップへアクセ<br />

スしない 期 間 では 本 端 子 を HIGH レベルに 保 持 し、アクセスする 期 間 中 は LOW レベルを 保 持 すること。<br />

SPI_CK<br />

この 端 子 は、 外 部 uC からの 同 期 シリアルデータ 伝 送 用 クロックの 入 力 端 子 である。<br />

SPI_DO<br />

この 端 子 は、 外 部 uC への 同 期 シリアルデータ 出 力 端 子 である。SPI_CK の 立 下 りエッジに 同 期 して、 本<br />

端 子 からデータが 出 力 される。<br />

SPI_DI<br />

この 端 子 は、 外 部 uC からの 同 期 シリアルデータ 入 力 端 子 である。SPI_CK の 立 ち 上 がりエッジに 同 期 し<br />

て、 外 部 uC からのデータを 取 り 込 む。<br />

IRQ<br />

この 端 子 は、 外 部 uC への 割 り 込 み 通 知 である。 割 り 込 み 通 知 時 に、 本 端 子 は HIGH レベルになり、 割<br />

り 込 み 要 因 が 解 除 されるまで HIGH レベルを 保 持 する。 割 り 込 み 要 因 がない 場 合 には、 本 端 子 は LOW レ<br />

ベルを 保 持 する。<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 21<br />

4.2.3 GPIO 端 子<br />

GPIO 端 子 は 8 本 用 意 されている。これらの 端 子 の 初 期 状 態 は Hi-Z である。<br />

表 4-1 GPIO MUX<br />

GPIO7 GPIO6 GPIO5 GPIO4 GPIO3 GPIO2 GPIO1 GPIO0<br />

Mode0 PA1 PA0 LNA1 LNA0 TRX1 TRX0 ANT1 ANT0<br />

Mode1 REG15 REG14 REG13 REG12 REG11 REG10 REG9 REG8<br />

Mode2 Low Low Low Low BitDat BitCLK ANT1 ANT0<br />

Mode3 Low Low TRX1 TRX0 BitDat BitCLK ANT1 ANT0<br />

Mode4 REG15 REG14 REG13 REG12 BitDat BitCLK ANT1 ANT0<br />

Mode0<br />

本 モードは、 送 受 信 の 状 態 に 応 じて 外 部 PA 制 御 、 外 部 LNA 制 御 、 外 部 TRX 制 御 、 外 部 ANT 制 御 を<br />

行 う。 本 モードに 設 定 するためには、PERI_CNT4 レジスタの MONSEL フィールド(bit[15:9])を 0( 通 常<br />

動 作 )、CONT フィールド(bit[8])を 0 に 設 定 すること。なお、GPIO 端 子 を 出 力 状 態 にするためには、<br />

PERI_CNT4 レジスタの IOCNT フィールド(bit[7:0])を 0FFh( 全 端 子 出 力 )に 設 定 すること。<br />

送 信 時 :<br />

PA1: PERI_CNT1.bit[15]<br />

PA0: PERI_CNT1.bit[14]<br />

LNA1: PERI_CNT1.bit[9]<br />

LNA0: PERI_CNT1.bit[8]<br />

TRX1: PERI_CNT1.bit[7]<br />

TRX0: PERI_CNT1.bit[6]<br />

ANT1: PERI_CNT1.bit[1]<br />

ANT0: PERI_CNT1.bit[0]<br />

受 信 時 :<br />

PA1: PERI_CNT1.bit[13]<br />

PA0: PERI_CNT1.bit[12]<br />

LNA1: PERI_CNT1.bit[11]<br />

LNA0: PERI_CNT1.bit[10]<br />

TRX1: PERI_CNT1.bit[3]<br />

TRX0: PERI_CNT1.bit[2]<br />

ANT1: PERI_CNT1.bit[1]<br />

ANT0: PERI_CNT1.bit[0]<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 22<br />

Mode1<br />

本 モードでは、GPIO 端 子 を 外 部 uC から 任 意 の 状 態 に 設 定 できる。 本 モードに 設 定 するためには、<br />

PERI_CNT4 レジスタの MOSEL フィールド(bit[15:9])を 0( 通 常 動 作 )に、CONT フィールド(bit[8])を 1<br />

に 設 定 する。GPIO 端 子 を 出 力 状 態 にするためには、PERI_CNT4 レジスタの IOCONT フィールド<br />

(bit[7:0])で 出 力 設 定 したい GPIO 端 子 に 対 応 するビットを 1 に 設 定 すること。 出 力 データは、<br />

PERI_CNT1レジスタの GPIO_OUTフィールド(bit[15:8])に 設 定 ( 表 中 の REG[15:8]に 相 当 )し、 入 力 デ<br />

ータは、PERI_CNT2 レジスタから 読 み 出 すことができる。<br />

Mode2<br />

本 モードでは、ビット 同 期 がとれた 受 信 信 号 のビットクロックとビットデータを 出 力 する。 本 モードに 設 定 す<br />

るためには、PERI_CNT4 レジスタの MONSEL フィールド(bit[15:9])を 6h に、CONT フィールド(bit[8])<br />

を 0 に 設 定 する。また、GPIO 端 子 を 出 力 状 態 にするために、PERI_CNT4 レジスタの IOCNT フィールド<br />

(bit[7:0])を 0FFh( 全 端 子 出 力 )に 設 定 すること。<br />

Mode3<br />

本 モードでは、Mode2に 加 えて TRX[1:0]を 出 力 する。 本 モードに 設 定 するためには、PERI_CNT4レジ<br />

スタの MONSEL フィールド(bit[15:9])を 21h に、CONT フィールド(bit[8])を 0 に 設 定 する。また、GPIO<br />

端 子 を 出 力 状 態 にするために、PERI_CNT4 レジスタの IOCNT フィールド(bit[7:0])を 0FFh( 全 端 子 出<br />

力 )に 設 定 すること。<br />

Mode4<br />

本 モードでは、Mode2 に 加 えて PERI_CNT1 レジスタの GPIO_OUT フィールド(bit[15:12])( 表 中 の<br />

REG[15:8]に 相 当 )を 出 力 する。 本 モードに 設 定 するためには、PERI_CNT4 レジスタの MONSEL フィー<br />

ルド(bit[15:9])を 22h に、CONT フィールド(bit[8])を 0 に 設 定 する。また、GPIO 端 子 を 出 力 状 態 にする<br />

ために、PERI_CNT4 レジスタの IOCNT フィールド(bit[7:0])を 0FFh( 全 端 子 出 力 )に 設 定 すること。<br />

4.2.4 XTAL 端 子<br />

XIN、XO<br />

外 部 水 晶 振 動 子 (26MHz)を 本 端 子 に 接 続 し、 適 切 な 外 部 容 量 を 接 続 すること。TCXO(26MHz)を 接 続<br />

する 際 には、XIN 端 子 に TCXO 出 力 を DC カット( 容 量 をシリアル 接 続 )して 接 続 すること。<br />

XBO<br />

本 端 子 は、 外 部 水 晶 振 動 子 で 発 振 したクロックを 外 部 に 出 力 する。 外 部 でクロックが 不 要 な 場 合 、<br />

XO_CTR レジスタの XBUFON フィールド(bit[12])を 0 に 設 定 することにより 出 力 停 止 可 能 である。 未 使<br />

用 時 は、 開 放 にすること。<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 23<br />

4.2.5 RF 端 子<br />

TX_OUT_10<br />

本 端 子 は、サブ GHz バンド 用 高 周 波 信 号 の 出 力 端 子 である。 未 使 用 時 は、 開 放 にすること。<br />

RX_IN_10P、RX_IN_10N<br />

本 端 子 は、サブ GHz バンド 用 高 周 波 信 号 の 入 力 差 動 端 子 である。<br />

RX_IN_10P: 同 相 端 子 、RX_IN_10N: 逆 相 端 子<br />

未 使 用 時 は、 開 放 にすること。<br />

4.2.6 電 源<br />

VBAT<br />

本 端 子 は、1.8~3.6V の 電 源 端 子 である。<br />

VOUT_DIG<br />

本 端 子 は、VBAT から LSI 内 部 で 生 成 したデジタル 電 源 出 力 端 子 である。 本 端 子 に、0.1uF の 容 量 を<br />

接 続 すること。<br />

VOUT_PLL<br />

本 端 子 は、VBAT から LSI 内 部 で 生 成 した PLL 電 源 出 力 端 子 である。 本 端 子 に、0.1uF の 容 量 を 接 続<br />

すること。<br />

VOUT_VCO<br />

本 端 子 は、VBAT から LSI 内 部 で 生 成 した VCO 電 源 出 力 端 子 である。 本 端 子 に、0.1uF の 容 量 を 接<br />

続 すること。<br />

VOUT_RX<br />

本 端 子 は、VBAT から LSI 内 部 で 生 成 した RF-RX 電 源 出 力 端 子 である。 本 端 子 に、0.1uF の 容 量 を<br />

接 続 すること。<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 24<br />

5 電 気 的 特 性<br />

特 別 な 条 件 記 載 がない 限 り 以 下 の 条 件 での 特 性 を 記 載 したものである<br />

動 作 温 度 :25℃<br />

VBAT 端 子 印 可 電 圧 :3.3V<br />

環 境 : 弊 社 指 定 のリファレンスデザインボード<br />

169MHz バンド:169.45MHz<br />

400MHz バンド:450.00MHz<br />

920MHz バンド:920.00MHz<br />

5.1 スリープ・アイドル 消 費 電 流<br />

パラメータ 条 件 Min Typ Max 単 位<br />

DEEP SLEEP<br />

SLEEP<br />

IDLE<br />

RXWAIT<br />

VBAT 端 子 =3.3V<br />

CHIPEN 端 子 =GND<br />

VBAT 端 子 =3.3V<br />

CHIPEN 端 子 =3.3V<br />

デジタルレギュレータ ON<br />

他 レギュレータ OFF<br />

VBAT 端 子 =3.3V<br />

CHIPEN 端 子 =3.3V<br />

デジタルレギュレータ ON<br />

XTAL 発 振 状 態 (26MHz)<br />

PLL シンセサイザ、TRX 動 作 OFF<br />

VBAT 端 子 =3.3V<br />

CHIPEN 端 子 =3.3V<br />

デジタルレギュレータ ON<br />

XTAL 発 振 状 態 (26MHz)<br />

シンセサイザ 動 作 状 態 (920MHz バンド)<br />

TRX 動 作 OFF<br />

0.05 uA<br />

170 uA<br />

0.9 mA<br />

5.8 mA<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 25<br />

5.2 送 受 信 電 流<br />

パラメータ 条 件 Min Typ Max 単 位<br />

受 信 電 流<br />

送 信 電 流<br />

169MHz バンド GFSK2.4Kbps 11.8 mA<br />

400MHz バンド GFSK4.8Kbps 12.6 mA<br />

920MHz バンド GFSK100Kbps 12.8 mA<br />

169MHz バンド GFSK2.4Kbps<br />

16 mA<br />

TX_OUT_10 端 子 =+10dBm<br />

400MHz バンド GFSK4.8Kbps<br />

24 mA<br />

TX_OUT_10 端 子 =+13dBm<br />

920MHz バンド GFSK100Kbps<br />

30 mA<br />

TX_OUT_10 端 子 =+13dBm<br />

5.3 起 動 時 間<br />

パラメータ 条 件 Min Typ Max 単 位<br />

POR リセット 時 間 リセット 解 除 時 間 100 us<br />

レギュレータ 起 動 時 間 外 部 容 量 0.1uF 5 us<br />

XTAL 起 動 時 間 26MHz 発 振 開 始 時 間 200 us<br />

シンセサイザ 起 動 時 間 920MHz バンド 60 us<br />

RX to TX 切 り 替 え 時 間 50 us<br />

TX to RX 切 り 替 え 時 間 50 us<br />

5.4 XTAL、シンセサイザ<br />

パラメータ 条 件 Min Typ Max 単 位<br />

XTAL 容 量 調 整 精 度 50 fF<br />

シンセサイザ 周 波 数 レン 169MHzバンド 169 169.9 MHz<br />

ジ<br />

400MHz バンド 420 510 MHz<br />

920MHzバンド 863 930 MHz<br />

Phase Noise<br />

920MHzバンド 25kHz offset -92 dBc/Hz<br />

920MHzバンド 100kHz offset -92 dBc/Hz<br />

920MHzバンド 1MHz offset -112 dBc/Hz<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 26<br />

5.5 受 信 特 性<br />

169MHz バンド<br />

パラメータ 条 件 Min Typ Max 単 位<br />

受 信 感 度<br />

2.4 Kbps,FilteredFSK,BT=0.5,M=2.0<br />

BER=1%<br />

-124 dBm<br />

最 大 受 信 入 力 レベル -10 dBm<br />

入 力 インピーダンス RX_IN_10N と RX_IN_10P の 差 動 間 52-j742 Ω<br />

隣 接 チャネル 選 択 度 ・ 希 望 波<br />

50 dB<br />

次 隣 接 チャネル 選 択 度 変 調 :2.4Kbps,FilteredFSK<br />

BT=0.5,M=2.0<br />

レベル > 受 信 感 度 レベル+3dB<br />

・ 妨 害 波<br />

50 dB<br />

変 調 :CW 信 号<br />

チャネル 幅 :12.5kHz<br />

BER=1%<br />

ブロッキング<br />

・ 希 望 波<br />

変 調 :4.8Kbps,FilteredFSK<br />

BT=0.5,M=1.0<br />

レベル > 受 信 感 度 レベル+3dB<br />

・ 妨 害 波<br />

64 dB<br />

変 調 :CW 信 号<br />

周 波 数 : 希 望 波 周 波 数 ±2MHz<br />

BER=1%<br />

不 要 輻 射 レベル 25MHz-1GHz -65 dBm<br />

> 1GHz -65 dBm<br />

イメージ 信 号 減 衰 率 IF frequency = 325kHz<br />

IQ バランス 調 整 後<br />

41 dB<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 27<br />

400MHz バンド<br />

パラメータ 条 件 Min Typ Max 単 位<br />

受 信 感 度<br />

4.8Kbps,FilteredFSK,BT=0.5,M=1.0<br />

BER=1%<br />

-122 dBm<br />

最 大 受 信 入 力 レベル -10 dBm<br />

入 力 インピーダンス RX_IN_10N と RX_IN_10P の 差 動 間 14-j243 Ω<br />

隣 接 チャネル 選 択 度 ・ 希 望 波<br />

46 dB<br />

次 隣 接 チャネル 選 択 度 変 調 :4.8Kbps,FilteredFSK<br />

BT=0.5,M=1.0<br />

レベル > 受 信 感 度 レベル+3dB<br />

・ 妨 害 波<br />

55 dB<br />

変 調 : 希 望 波 と 同 じ<br />

チャネル 幅 :25kHz<br />

BER=1%<br />

ブロッキング<br />

・ 希 望 波<br />

変 調 :4.8Kbps,FilteredFSK<br />

BT=0.5,M=1.0<br />

レベル > 受 信 感 度 レベル+3dB<br />

・ 妨 害 波<br />

65 dB<br />

変 調 :CW 信 号<br />

周 波 数 : 希 望 波 周 波 数 ±2MHz<br />

BER=1%<br />

不 要 輻 射 レベル 25MHz-1GHz -65 dBm<br />

> 1GHz -65 dBm<br />

イメージ 信 号 減 衰 率 IF frequency = 325kHz<br />

IQ バランス 調 整 後<br />

41 dB<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 28<br />

920MHz バンド<br />

パラメータ 条 件 Min Typ Max 単 位<br />

受 信 感 度<br />

4.8Kbps,FilteredFSK,BT=0.5,M=1.0<br />

BER=0.1%<br />

-118 dBm<br />

50Kbps,FilteredFSK,BT=0.5,M=1.0<br />

BER=0.1%<br />

-108 dBm<br />

100Kbps,FilteredFSK,BT=0.5,M=1.0<br />

BER=0.1%<br />

-105 dBm<br />

最 大 受 信 入 力 レベル -10 dBm<br />

入 力 インピーダンス RX_IN_10N と RX_IN_10P の 差 動 間 7-j100 Ω<br />

隣 接 チャネル 選 択 度 ・ 希 望 波<br />

35 dB<br />

次 隣 接 チャネル 選 択 度 変 調 :100Kbps,FilteredFSK<br />

BT=0.5,M=1.0<br />

レベル > 受 信 感 度 レベル+3dB<br />

・ 妨 害 波<br />

40 dB<br />

変 調 : 希 望 波 と 同 じ<br />

チャネル 幅 :400kHz<br />

BER=0.1%<br />

ブロッキング<br />

・ 希 望 波<br />

変 調 :100Kbps,FilteredFSK<br />

BT=0.5,M=1.0<br />

レベル > 受 信 感 度 レベル+3dB<br />

・ 妨 害 波<br />

60 dB<br />

変 調 :CW 信 号<br />

周 波 数 : 希 望 波 周 波 数 ±10MHz<br />

BER=0.1%<br />

不 要 輻 射 レベル 25MHz-1GHz -65 dBm<br />

> 1GHz -65 dBm<br />

イメージ 信 号 減 衰 率 IF frequency = 325kHz<br />

IQ バランス 調 整 後<br />

40 dB<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 29<br />

5.6 送 信 特 性<br />

169MHzバンド<br />

パラメータ 条 件 Min Typ Max 単 位<br />

最 大 送 信 電 力 TX_SET レジスタ=0FFh +13 +15 dBm<br />

最 小 送 信 電 力 TX_SET レジスタ=00h -6 dBm<br />

送 信 電 力 制 御 幅 Pout>+10dBm 0.2 dB<br />

送 信 電 力 温 度 変 動 幅 -40~85℃ ±0.6 dB<br />

高 調 波 レベル<br />

2 次 高 調 波 Pout=+10dBm -42 dBm<br />

3 次 高 調 波 Pout=+10dBm -51 dBm<br />

不 要 発 射 レベル 25MHz-1GHz Pout=+10dBm<br />

高 調 波 除 く<br />

-50 dBm<br />

> 1GHz Pout=+10dBm -50 dBm<br />

400MHz バンド<br />

パラメータ 条 件 Min Typ Max 単 位<br />

最 大 送 信 電 力 TX_SET レジスタ=0FFh +13 +15 dBm<br />

最 小 送 信 電 力 TX_SET レジスタ=00h -6 dBm<br />

送 信 電 力 制 御 幅 Pout>+10dBm 0.2 dB<br />

送 信 電 力 温 度 変 動 幅 -40~85℃ ±0.6 dB<br />

高 調 波 レベル<br />

2 次 高 調 波 Pout=+10dBm -40 dBm<br />

3 次 高 調 波 Pout=+10dBm -56 dBm<br />

不 要 発 射 レベル 25MHz-1GHz Pout=+10dBm<br />

高 調 波 除 く<br />

-46 dBm<br />

> 1GHz Pout=+10dBm<br />

高 調 波 除 く<br />

-46 dBm<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 30<br />

920MHzバンド<br />

パラメータ 条 件 Min Typ Max 単 位<br />

最 大 送 信 電 力 TX_SET レジスタ=0FFh +13 +15 dBm<br />

最 小 送 信 電 力 TX_SET レジスタ=00h -6 dBm<br />

送 信 電 力 制 御 幅 Pout>+10dBm 0.2 dB<br />

送 信 電 力 温 度 変 動 幅 -40~85℃ ±0.6 dB<br />

高 調 波 レベル<br />

2 次 高 調 波 Pout=+10dBm -40 dBm<br />

3 次 高 調 波 Pout=+10dBm -40 dBm<br />

不 要 発 射 レベル 25MHz-1GHz Pout=+10dBm<br />

高 調 波 除 く<br />

-43 dBm<br />

> 1GHz Pout=+10dBm<br />

高 調 波 除 く<br />

-43 dBm<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 31<br />

5.7 アクセサリ 特 性<br />

パラメータ 条 件 Min Typ Max 単 位<br />

温 度 センサ 精 度 測 定 温 度 =-40 ~ 85℃ 2.3 ℃<br />

LBD 検 出 精 度 VBAT=1.8 ~ 2.1V ±0.06 V<br />

RSSI 測 定 精 度 入 力 信 号 レベル =<br />

受 信 感 度 レベル+10dB ~ -10dBm<br />

±1 dB<br />

5.8 SPIインターフェースACタイミング<br />

Ta=-40~85℃、VDD=1.8~3.6V<br />

パラメータ 略 号 条 件 Min Typ Max 単 位<br />

SPI_CK LOW 幅 tCKL 40 ns<br />

SPI_CK HIGH 幅 tCKH 40 ns<br />

SPI_CK 周 期 tCKP 100 ns<br />

SPI_CSN->SPI_CK 立 上 時 間 tCSS 20 ns<br />

SPI_CK->SPI_CSN 立 上 時 間 tCSH 20 ns<br />

SPI_CSN WAIT 時 間 tCSW 230 ns<br />

SPI_DI セットアップ 時 間 tDIS 15 ns<br />

SPI_DI ホールド 時 間 tDIH 15 ns<br />

SPI_DO 出 力 遅 延 時 間 tDOD 25 ns<br />

SPI_DO 出 力 開 始 遅 延 tDOS 30 ns<br />

SPI_DO 出 力 終 了 遅 延 tDOE 30 ns<br />

SPI_CK 中 断 tIDL 250 ns<br />

SPI TIME OUT tTO 10 ms<br />

* 外 部 負 荷 容 量 は 20pF 時 の 値 です。<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 32<br />

tCSS<br />

tCSH<br />

tCSW<br />

SPI_CSN<br />

tCKP<br />

SPI_CK<br />

tCKL<br />

tCKH<br />

SPI_DI<br />

tDOS<br />

tDIS<br />

tDIH<br />

tDOD<br />

tDOE<br />

SPI_DO<br />

tIDL<br />

tTO<br />

SPI_CSN<br />

SPI_CK<br />

図 5-1 SPI インターフェースタイミング<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 33<br />

6 SPIインターフェイス<br />

6.1 概 要<br />

本 同 期 シリアルインターフェイス(3 線 SPI、SPI_CSN、 SPI_CK、 SPI_DI)を 用 いて、 外 部 uC から<br />

MN87401 を 制 御 すること。この 制 御 は、レジスタリード・ライト、メモリリード・ライトコマンドにより 実 行 され<br />

る。なお、そのコマンドは、コマンドバイト、アドレスバイト、データバイトの 順 に 外 部 uC から 送 り、バイト 単 位<br />

で MSB(bit[7])から LSB(bit[0])の 順 に 伝 送 すること。<br />

6.2 コマンドフォーマット<br />

MN87401 へのコマンドは、 以 下 の 3 つのフィールドで 構 成 されている。<br />

• コマンドフィールド(アクセス 内 容 )<br />

8 ビット<br />

• アドレスフィールド(アドレスの 下 位 8 ビット) 8 ビット<br />

• データフィールド<br />

8ビット 以 上 (8 の 倍 数 ビットであること)<br />

コマンドフィールドは、リード・ライトビット(Write/Read ビット、ビット 7)、コマンド 内 容 (Access ビット、<br />

bit[6:5])、 使 用 禁 止 予 約 ビット(bit[4:2] = 000b)、アクセスレジスタ・メモリのアドレスの 上 位 2 ビット<br />

(bit[1:0])で 構 成 されている。<br />

7 6 5 4 3 2 1 0<br />

Write/Read<br />

0:Write<br />

1:Read<br />

UpperAddressExtention<br />

A[9:8]<br />

Reserved<br />

Access<br />

00:Register<br />

01:Reserved<br />

10:Memory<br />

11:Reserved<br />

図 6-1 コマンドフォーマット<br />

6.3 信 号 動 作<br />

レジスタアクセスの 信 号 シーケンスを 図 6-2、 図 6-3 に、メモリアクセスの 信 号 シーケンスを 図 6-4、 図<br />

6-5 にそれぞれ 示 す。MN87401 は、SPI_CKクロックの 立 ち 上 がりエッジでデータをラッチし、SPI_CKクロ<br />

ックの 立 下 りエッジに 同 期 してデータを 出 力 する。データ 伝 送 停 止 時 には、 外 部 uCはSPI_CSN=HIGHレ<br />

ベル、SPI_CLK=HIGHレベルの 状 態 を 保 持 すること。<br />

MN87401 アクセス 時 には、 外 部 uC は SPI_CK=HIGH レベル 状 態 で SPI_CSN を LOW レベルにす<br />

ること。SPI_CSN が LOW レベルに 遷 移 すると、MN87401 は SPI インターフェイスを 動 作 させる。この 後 、<br />

SPI_CK の 最 初 の 立 下 りエッジのタイミングで、MN87401 はコマンドの MSB(bit[7]) 入 力 を 認 識 する。コ<br />

マンド、アドレス、データ 期 間 中 は、 外 部 uC は SPI_CSN を LOW レベルに 保 持 し、 全 データの 入 力 が 終<br />

了 してから SPI_CLK を HIGH レベルにしたのちに、SPI_CSN を HIGH レベルにすること。<br />

レジスタアクセスの 際 、リード・ライトともに 単 一 レジスタへのアクセス(データ 長 は 16 ビット)のみ 可 能 で<br />

ある。ライト 時 は、 最 終 データ(D[8])の SPI_CK の 立 ち 上 がり( 最 終 エッジ)で、MN87401 内 のレジスタへ<br />

パナソニック 株 式 会 社 デバイス 社

製 品 仕 様 書<br />

MN87401-EB<br />

全 ページ ページ<br />

206 34<br />

の 書 き 込 みが 行 われる。データリード・ライトともに、MN87401 は 16 ビットデータの D[7:0]、D[15:8]の 順<br />

番 にデータを 処 理 する。なおレジスタアクセスは、XTAL が 停 止 している 状 態 でも 可 能 である。<br />

SPI_CSN<br />

SPI_CK<br />

SPI_DI<br />

7 0<br />

7 0<br />

7 015 8<br />

SPI_DO<br />

Command Address Write Data<br />

(D[7:0])<br />

Write Data<br />

(D[15:8])<br />

図 6-2 レジスタへの 書 き 込 みシーケンス<br />

SPI_CSN<br />

SPI_CK<br />

SPI_DI<br />

7 0<br />

7 0<br />

7 015 8<br />

SPI_DO<br />

Command<br />

Address<br />

Read Data<br />

(D[7:0])<br />

Read Data<br />

(D[15:8])<br />

図 6-3 レジスタからの 読 み 出 しシーケンス<br />

メモリアクセスでは、 複 数 バイトアクセスが 可 能 である。 複 数 バイトアクセス 時 は、 外 部 uC は、SPI_CSN<br />