sparc-architecture-2011-1728132

sparc-architecture-2011-1728132

sparc-architecture-2011-1728132

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

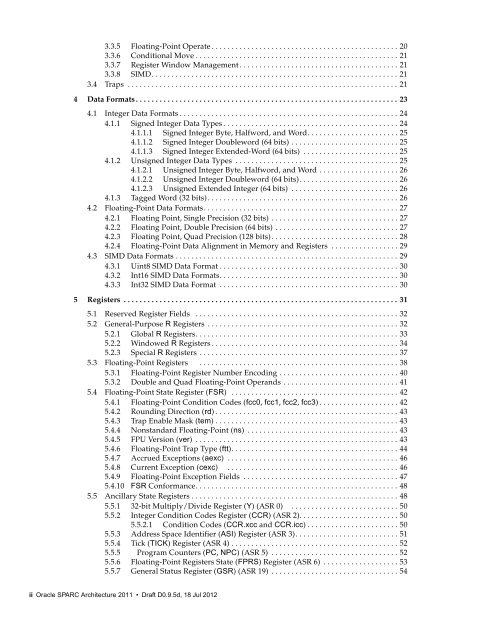

3.3.5 Floating-Point Operate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20<br />

3.3.6 Conditional Move . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21<br />

3.3.7 Register Window Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21<br />

3.3.8 SIMD. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21<br />

3.4 Traps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21<br />

4 Data Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23<br />

4.1 Integer Data Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24<br />

4.1.1 Signed Integer Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24<br />

4.1.1.1 Signed Integer Byte, Halfword, and Word. . . . . . . . . . . . . . . . . . . . . . . 25<br />

4.1.1.2 Signed Integer Doubleword (64 bits) . . . . . . . . . . . . . . . . . . . . . . . . . . . 25<br />

4.1.1.3 Signed Integer Extended-Word (64 bits) . . . . . . . . . . . . . . . . . . . . . . . . 25<br />

4.1.2 Unsigned Integer Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25<br />

4.1.2.1 Unsigned Integer Byte, Halfword, and Word . . . . . . . . . . . . . . . . . . . . 26<br />

4.1.2.2 Unsigned Integer Doubleword (64 bits). . . . . . . . . . . . . . . . . . . . . . . . . 26<br />

4.1.2.3 Unsigned Extended Integer (64 bits) . . . . . . . . . . . . . . . . . . . . . . . . . . . 26<br />

4.1.3 Tagged Word (32 bits). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26<br />

4.2 Floating-Point Data Formats. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27<br />

4.2.1 Floating Point, Single Precision (32 bits) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27<br />

4.2.2 Floating Point, Double Precision (64 bits) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27<br />

4.2.3 Floating Point, Quad Precision (128 bits) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28<br />

4.2.4 Floating-Point Data Alignment in Memory and Registers . . . . . . . . . . . . . . . . . 29<br />

4.3 SIMD Data Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29<br />

4.3.1 Uint8 SIMD Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30<br />

4.3.2 Int16 SIMD Data Formats. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30<br />

4.3.3 Int32 SIMD Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30<br />

5 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31<br />

5.1 Reserved Register Fields . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32<br />

5.2 General-Purpose R Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32<br />

5.2.1 Global R Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33<br />

5.2.2 Windowed R Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34<br />

5.2.3 Special R Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37<br />

5.3 Floating-Point Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38<br />

5.3.1 Floating-Point Register Number Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40<br />

5.3.2 Double and Quad Floating-Point Operands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41<br />

5.4 Floating-Point State Register (FSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42<br />

5.4.1 Floating-Point Condition Codes (fcc0, fcc1, fcc2, fcc3) . . . . . . . . . . . . . . . . . . . . 42<br />

5.4.2 Rounding Direction (rd) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43<br />

5.4.3 Trap Enable Mask (tem) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43<br />

5.4.4 Nonstandard Floating-Point (ns) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43<br />

5.4.5 FPU Version (ver) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43<br />

5.4.6 Floating-Point Trap Type (ftt). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44<br />

5.4.7 Accrued Exceptions (aexc) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46<br />

5.4.8 Current Exception (cexc) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46<br />

5.4.9 Floating-Point Exception Fields . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47<br />

5.4.10 FSR Conformance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48<br />

5.5 Ancillary State Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48<br />

5.5.1 32-bit Multiply/Divide Register (Y) (ASR 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . 50<br />

5.5.2 Integer Condition Codes Register (CCR) (ASR 2). . . . . . . . . . . . . . . . . . . . . . . . . 50<br />

5.5.2.1 Condition Codes (CCR.xcc and CCR.icc) . . . . . . . . . . . . . . . . . . . . . . . 50<br />

5.5.3 Address Space Identifier (ASI) Register (ASR 3). . . . . . . . . . . . . . . . . . . . . . . . . . 51<br />

5.5.4 Tick (TICK) Register (ASR 4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52<br />

5.5.5 Program Counters (PC, NPC) (ASR 5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52<br />

5.5.6 Floating-Point Registers State (FPRS) Register (ASR 6) . . . . . . . . . . . . . . . . . . . 53<br />

5.5.7 General Status Register (GSR) (ASR 19) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54<br />

ii Oracle SPARC Architecture <strong>2011</strong> • Draft D0.9.5d, 18 Jul 2012