50~chapter 11 ams.pdf

50~chapter 11 ams.pdf

50~chapter 11 ams.pdf

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Chapter <strong>11</strong> Exercise Solutions<br />

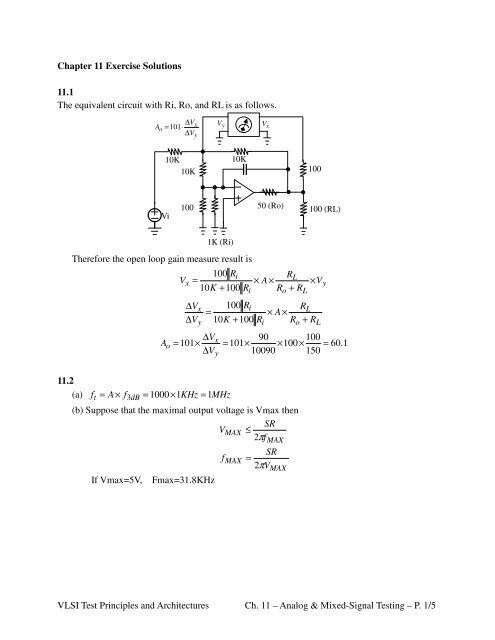

<strong>11</strong>.1<br />

The equivalent circuit with Ri, Ro, and RL is as follows.<br />

∆V<br />

A<br />

x<br />

o =101⋅<br />

∆Vy<br />

Vy<br />

Vx<br />

10K<br />

10K<br />

10K<br />

100<br />

Vi<br />

100<br />

50 (Ro)<br />

100 (RL)<br />

Therefore the open loop gain measure result is<br />

A<br />

o<br />

100 Ri<br />

R<br />

V L<br />

x =<br />

× A×<br />

× Vy<br />

10K<br />

+ 100 Ri<br />

Ro<br />

+ RL<br />

∆V<br />

∆V<br />

x<br />

y<br />

1K (Ri)<br />

(b)<br />

100 Ri<br />

R<br />

=<br />

× A×<br />

L<br />

10K<br />

+ 100 R R + R<br />

∆V<br />

90 100<br />

= 101 ×<br />

x<br />

= 101×<br />

× 100×<br />

= 60.1<br />

∆V<br />

10090 150<br />

y<br />

i<br />

o<br />

L<br />

<strong>11</strong>.2<br />

(a) ft = A×<br />

f3 dB = 1000×<br />

1KHz<br />

= 1MHz<br />

(b) Suppose that the maximal output voltage is Vmax then<br />

SR<br />

VMAX<br />

≤<br />

2πf<br />

If Vmax=5V,<br />

Fmax=31.8KHz<br />

fMAX<br />

=<br />

2π<br />

MAX<br />

SR<br />

VMAX<br />

VLSI Test Principles and Architectures Ch. <strong>11</strong> – Analog & Mixed-Signal Testing – P. 1/5

<strong>11</strong>.3 (Ask student to check the definition first.)<br />

∆V<br />

5.2 − 4.9<br />

(a) Load _ Regulation = 100% × o<br />

= × 100% = 6%<br />

V<br />

5<br />

o _ NOM<br />

Max(<br />

∆I<br />

L ), Min(<br />

Vi<br />

)<br />

∆V<br />

5.15 − 4.9<br />

(b) Line _ Regulation = 100% × o<br />

= × 100% = 5%<br />

V<br />

5<br />

o _ NOM<br />

Max(<br />

∆VI<br />

), Max(<br />

IL<br />

)<br />

(c) Drop out voltage is 5.8V. The minimum input voltage for Vout > 4.75V.<br />

<strong>11</strong>.4<br />

Solution A<br />

Capacitor Voltage<br />

Zener Diode<br />

Max Iout<br />

Min Cap Voltage<br />

At Vc=7V<br />

At Vc=14V<br />

Solution B<br />

7V ≤ VC ≤ 14V<br />

10<br />

VZD = 5.7V<br />

+ ( VC<br />

− 5.7V<br />

) × , 5.83<br />

≤ V ZD ≤ 6. 53V<br />

90 + 10<br />

V − 5.7V<br />

I = CMin<br />

oMax<br />

× 100 , (all the current goes to the base)<br />

90Ω<br />

I ms<br />

V V<br />

oMax ×16.6<br />

CMin = c −<br />

(at maximal current after ripple<br />

10000µ F<br />

deducted)<br />

V CMin = 6. 2V<br />

I oMax = 0. 5A<br />

(solve the above two equations)<br />

V CMin = 13. 2V<br />

I oMax = 0. 5A<br />

(ripple is 0.8V at 0.5A output<br />

current)<br />

Max Output 14V-0.2V (VCE Sat) Minimun Output 6.2V-0.2V<br />

Output Voltage (6V, 13.2V) 9 .6V ± 3. 6V<br />

Line Regulation 7.2V<br />

× 100% = 75%<br />

9.6V<br />

Load Regulation 6.8V<br />

− 6.2V<br />

× 100% = 6.25% (Vo=6.8V without load)<br />

9.6V<br />

Solution C Dropout voltage is 5V (AC) under 0.5A load.<br />

VLSI Test Principles and Architectures Ch. <strong>11</strong> – Analog & Mixed-Signal Testing – P. 2/5

<strong>11</strong>.5<br />

(a) 2.7V (2V + 0.7V)<br />

(b) Once there is a positive bias of the diode, there is distortion. Hence, due to the nonlinear<br />

characteristics of the diode, the distortion free input amplitude is 2V. In other words, the<br />

diode is always reverse biased for distortion free.<br />

<strong>11</strong>.6<br />

(c) Require SPICE simulation. For V in = 2 .7V<br />

× sinωt<br />

, simulate the output waveform. Then,<br />

transform the output waveform (integer number of cycles), into frequency domain by FFT.<br />

Then, use (<strong>11</strong>.<strong>11</strong>) to find the SNR. Note that the result may be different for different diode<br />

models.<br />

(a)<br />

(b)<br />

(c)<br />

I 1 A<br />

V Leak µ<br />

droop = = = 100V<br />

CH<br />

10nF<br />

/ sec<br />

1LSB =<br />

10<br />

1V<br />

/ 2 = 1mV<br />

, T = 0 .5 LSB / V = 5 s<br />

T acq<br />

holdMAX droop µ<br />

−<br />

VA × e τ V<br />

V<br />

≤ 0. 5LSB<br />

, T<br />

A<br />

1<br />

acq = τ × ln = (100 × 10nF)<br />

× ln = 7. 6µ<br />

s<br />

0.5LSB<br />

0.5mV<br />

fmax = 1/( Tacq + TADC<br />

) = 1/8.6µ s = <strong>11</strong>6KHz<br />

.<br />

(d) The leakage after 1us is<br />

Hence, 1LSB=0.2mV.<br />

n<br />

Hence 2 ≤ 1V<br />

/ 0.2mV<br />

= 5000 ∴ n = 12<br />

(e) Same as (c).<br />

<strong>11</strong>.7<br />

(a) The maximal slop of a sine wave is<br />

For 1KHz, the maximal error is<br />

For 1MHz, the maximal error is<br />

(b) 1LSB=0.5mV, hence,<br />

n<br />

T<br />

1 µ s × Vdroop = 0.1mV<br />

= 0. 5LSB<br />

0.1mV.<br />

2 πf ×VA<br />

Tjitter × 2πf<br />

× VA<br />

= 100 p × 2π<br />

× 10 × 0.5V<br />

= 0. 314µ<br />

V<br />

Tjitter × 2π<br />

f × VA<br />

= 100 p × 2π<br />

× 10 × 0.5V<br />

= 0. 314mV<br />

× 2π f × V ≤ 0. mV , f 1. 59MHz<br />

jitter A 5<br />

max =<br />

(c) For 1KHz, 2 ≤ 1V<br />

/ 0.314µ<br />

V = 3.184×<br />

10 ∴ n = 21<br />

n<br />

For 1MHz, 2 ≤ 1V<br />

/ 0.314mV<br />

= 3.184×<br />

10 ∴ n = <strong>11</strong><br />

6<br />

3<br />

3<br />

6<br />

<strong>11</strong>.8<br />

Code 000 001 010 0<strong>11</strong> 100 101 <strong>11</strong>0 <strong>11</strong>1<br />

Frequency 80 163 159 149 140 135 130 68<br />

DNL -0.38 0.27 0.24 0.16 0.09 0.05 0.02 -0.47<br />

INL -0.38 -0.<strong>11</strong> 0.13 0.29 0.38 0.43 0.45 -0.02<br />

VLSI Test Principles and Architectures Ch. <strong>11</strong> – Analog & Mixed-Signal Testing – P. 3/5

f avg<br />

= 1024 /8 = 128<br />

The INL for code (<strong>11</strong>1) should be zero. The nonzero is because of the rounding.<br />

<strong>11</strong>.9<br />

Transfer Curves<br />

3<br />

f ×<br />

16<br />

Histogr<strong>ams</strong><br />

3<br />

f ×<br />

16<br />

3<br />

f ×<br />

16<br />

f<br />

16<br />

f ×<br />

14<br />

16<br />

f ×<br />

14<br />

<strong>11</strong>.10<br />

(a) (b) (c)<br />

(f) for (d), INL=4LSB<br />

7<br />

i<br />

16<br />

For (e), INL = ∫ 0.5×<br />

sin( π ) = 2×<br />

0.5×<br />

16<br />

π<br />

0<br />

(d)<br />

(e)<br />

(a)<br />

(b)<br />

7<br />

i<br />

16<br />

DNL = 0 .1×<br />

16 = 1. 6LSB<br />

, INL = ∫ 0.1×<br />

sin( 2π<br />

) = 2×<br />

0.5×<br />

= 2. 55LSB<br />

0 16<br />

2π<br />

Offset = 0 .1×<br />

16 = 1. 6LSB<br />

, Gain Error=0<br />

(c) Same as (a)<br />

<strong>11</strong>.<strong>11</strong><br />

(a)<br />

(a)<br />

(b)<br />

VLSI Test Principles and Architectures Ch. <strong>11</strong> – Analog & Mixed-Signal Testing – P. 4/5

(b)<br />

(a)<br />

y<br />

y<br />

<strong>11</strong><br />

12<br />

I<br />

=<br />

V<br />

1<br />

I<br />

=<br />

V<br />

1 V2<br />

= 0<br />

1<br />

2 V1<br />

= 0<br />

y<br />

y<br />

21<br />

22<br />

I<br />

=<br />

V<br />

2<br />

I<br />

=<br />

V<br />

1 V2<br />

= 0<br />

2<br />

2 V1<br />

= 0<br />

H P1 P2 P3 P4<br />

y<strong>11</strong> Vs/Im GND GND GND<br />

y12 Im GND Vs GND<br />

y21 Vs GND Im GND<br />

y22 GND GND Vs/Im GND<br />

z<br />

<strong>11</strong><br />

V<br />

=<br />

I<br />

1<br />

1 I2<br />

= 0<br />

V<br />

1 I2<br />

= 0<br />

z<br />

1<br />

2<br />

12 = z22<br />

=<br />

I2<br />

I<br />

I 0 2<br />

1=<br />

I1=<br />

0<br />

H P1 P2 P3 P4<br />

y<strong>11</strong> Is/Vm GND Open GND<br />

y12 Vm GND Is GND<br />

y21 Is GND Vm GND<br />

y22 Open GND Is/Vm GND<br />

g<br />

g<br />

<strong>11</strong><br />

12<br />

I<br />

=<br />

V<br />

1<br />

I<br />

=<br />

I<br />

1 I2<br />

= 0<br />

1<br />

2 V1<br />

= 0<br />

z<br />

g<br />

g<br />

21<br />

21<br />

22<br />

V<br />

=<br />

I<br />

V<br />

2<br />

V<br />

=<br />

V<br />

2<br />

V<br />

=<br />

I<br />

1 I2<br />

= 0<br />

2<br />

2 V1<br />

= 0<br />

H P1 P2 P3 P4<br />

g<strong>11</strong> Vs/Im GND Open GND<br />

g12 Im GND Is GND<br />

g21 Vs GND Vm GND<br />

g22 GND GND Is/Vm GND<br />

VLSI Test Principles and Architectures Ch. <strong>11</strong> – Analog & Mixed-Signal Testing – P. 5/5