fast orbit feedback scheme and implementation for taiwan photon ...

fast orbit feedback scheme and implementation for taiwan photon ...

fast orbit feedback scheme and implementation for taiwan photon ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

control <strong>and</strong> 0.05 nrad <strong>for</strong> <strong>fast</strong> ones. Noise level is around -<br />

120 dB where it would contribute 200 nm RMS <strong>orbit</strong><br />

disturbances from total 168 slow correctors <strong>and</strong> 10 nm <strong>for</strong><br />

96 <strong>fast</strong> correctors. Compared to slow correctors, <strong>orbit</strong><br />

disturbance cause by <strong>fast</strong> correctors could be ignored.<br />

Furthermore, the <strong>fast</strong> corrector response is corresponded<br />

to the 1.3 kHz b<strong>and</strong>width. The test results are shown as<br />

Fig. 5.<br />

-999.05<br />

-999.06<br />

Figure 3: FOFB GDX closed loop test. The upper plot is<br />

position; the lower plot is relative power level change.<br />

CORRECTOR POWER SUPPLY<br />

CONTROL INTERFACE<br />

The corrector power supply module is a sophiscated<br />

switching power supply with analogue regulator [5]. It<br />

will be applied <strong>for</strong> slow correctors, <strong>fast</strong> correctors, skew<br />

quadrupoles <strong>and</strong> etc. Each power suply sub-rack<br />

accomodates up to eight power supply modules. The<br />

center slot is allocated to install a special designed<br />

EPICS IOC with <strong>feedback</strong> support.<br />

The corrector power-supply controller (CPSC)<br />

module is embedded with ARM processor <strong>and</strong> Xilinx<br />

Spartan-6 FPGA. It was contracted to D-TACQ. This<br />

module will be installed at center slot of the power<br />

supply sub-rack. The module embedded EPICS IOC <strong>and</strong><br />

FPGA supports slow access <strong>for</strong> the EPICS CA clients<br />

<strong>and</strong> <strong>fast</strong> settings from <strong>orbit</strong> <strong>feedback</strong> system or the<br />

feedfoward application such as skew compensation. The<br />

<strong>fast</strong> settings from <strong>feedback</strong> engines with rocket I/O or<br />

feed-<strong>for</strong>ward engines with Gigabit ethernet will be<br />

sumed together with slow settings in CPSC to regulator<br />

module of corrector. The functional block diagram of<br />

CPSC module is shown in Fig. 4.<br />

External<br />

Clock<br />

Input<br />

DO (LEMO connector, <strong>for</strong> timing measurement), Trigger out, Package received<br />

Fast<br />

Setting SFP Port<br />

Setting Buffers<br />

Ports (GbE, Rx<br />

Ethernet Interface<br />

UDP/IP),<br />

(Hardware UDP Stack)<br />

Tx<br />

Through<br />

Heartbeat Register<br />

Port<br />

Fast<br />

Rx<br />

Setting Port,<br />

AURORA<br />

Through Tx<br />

Port<br />

Heartbeat Register<br />

(AURORA)<br />

Trigger (3 Hz) Sequencer ~8 x 64 k x 32 bit<br />

Data Acquisition10 kHz clock Wave<strong>for</strong>m Memory<br />

Trigger input<br />

Slow Setting<br />

Slow Trigger<br />

Buffer<br />

(on dem<strong>and</strong>, may not necessary)<br />

Slow Access (~ 10 Hz)<br />

Gigabit<br />

Ethernet<br />

Internal 10 kHz Clock Generator<br />

Up to 10 kHz Fast Setting Clock)<br />

Control <strong>and</strong> Status Registers<br />

Single Board Computer<br />

(Linux, EPICS IOC)<br />

10 kHz rate<br />

wave<strong>for</strong>m<br />

10 Hz rate data<br />

Wave<strong>for</strong>m Memory<br />

Free running<br />

Or Pre/Post Trigger<br />

Slow Access<br />

(~ 10 Hz)<br />

Control <strong>and</strong><br />

Status Registers<br />

4 ways,<br />

8 ch adder<br />

+<br />

Individual<br />

Channel<br />

Enable/Disable<br />

24 ch, 16 bit ADC<br />

Status Registers<br />

8 bit DI<br />

Write Registers<br />

8 bit DO<br />

8 Ch, 20 bit DAC<br />

Precise<br />

digital<br />

temperature<br />

sensors<br />

96 pin<br />

DIN61412<br />

Connectors x 2<br />

8 ch, 24 bit ADC<br />

(10 kHz Sampling)<br />

+/- 15 V<br />

+ 5 V<br />

Figure 4: Functional block diagram of the corrector power<br />

supply controller module. Fast setting from <strong>orbit</strong> <strong>feedback</strong><br />

<strong>and</strong> slow setting from EPICS CA console.<br />

Preliminary corrector power supply testing<br />

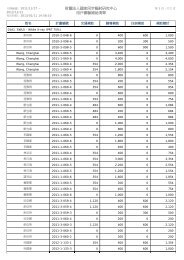

The power supply achieves 20 bit per<strong>for</strong>mance where<br />

it is equivalent to 1 nrad resolution <strong>for</strong> slow corrector<br />

Current (mA)<br />

-999.07<br />

-999.08<br />

-999.09<br />

-999.1<br />

-999.11<br />

-999.12<br />

Volt<br />

Volt<br />

Amp<br />

75 80 85 90 95<br />

(a)<br />

10 -5 imonitor: shunt<br />

10 -6<br />

10 -7<br />

0 200 400 600 800 1000<br />

Volt<br />

10 -5 imonitor: dcct<br />

10 -6<br />

10 -7<br />

0 200 400 600 800 1000<br />

Frequency(Hz)<br />

1.2<br />

1<br />

0.8<br />

0.6<br />

0.4<br />

0.2<br />

0<br />

(b)<br />

Vertical Fast Step Response<br />

Model<br />

-0.2<br />

0 2 4 6 8 10 12 14 16<br />

Time (msec)<br />

(c)<br />

Figure 5: (a) 20 bit per<strong>for</strong>mance, each step is around 20<br />

uA. (b) Noise level is around 1uA (c) Step response of<br />

vertical corrector power supply.<br />

FAST ORBIT FEEDBACK WITH SLOW<br />

CORRECTOR COMPENSATION<br />

The lattice layout <strong>for</strong> one cell of TPS storage ring is as<br />

Fig. 6. There are 7 BPMs <strong>and</strong> 7 horizontal/vertical<br />

correctors are winding on the sextupoles in each cell to<br />

provide hundreds of micro-radian kick strength while<br />

their b<strong>and</strong>width could be limited much less than 100 Hz<br />

due to the TPS alumni vacuum chamber. There<strong>for</strong>e, extra<br />

four <strong>fast</strong> horizontal/vertical correctors are installed on the<br />

bellows which have <strong>fast</strong> response but smaller trim<br />

strength around 20~30 urad [6]. The <strong>fast</strong> corrector will be<br />

used <strong>for</strong> <strong>feedback</strong> correction to suppress various