VITA 46.9: Ensuring mezzanine I/O pinout interoperability for VPX ...

VITA 46.9: Ensuring mezzanine I/O pinout interoperability for VPX ...

VITA 46.9: Ensuring mezzanine I/O pinout interoperability for VPX ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

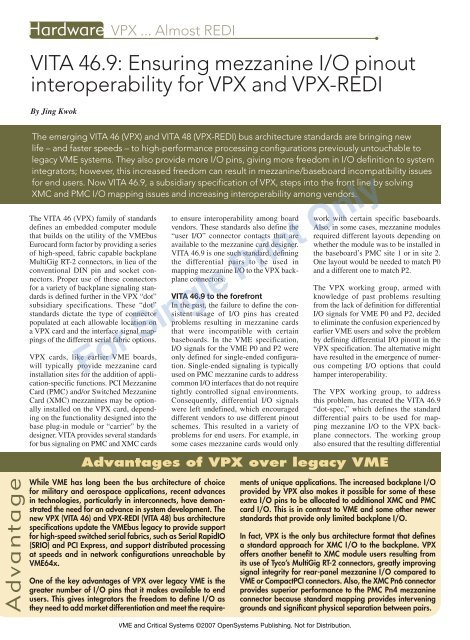

Hardware<strong>VPX</strong> ... Almost REDI<strong>VITA</strong> <strong>46.9</strong>: <strong>Ensuring</strong> <strong>mezzanine</strong> I/O <strong>pinout</strong><strong>interoperability</strong> <strong>for</strong> <strong>VPX</strong> and <strong>VPX</strong>-REDIBy Jing KwokThe emerging <strong>VITA</strong> 46 (<strong>VPX</strong>) and <strong>VITA</strong> 48 (<strong>VPX</strong>-REDI) bus architecture standards are bringing newlife – and faster speeds – to high-per<strong>for</strong>mance processing configurations previously untouchable tolegacy VME systems. They also provide more I/O pins, giving more freedom in I/O definition to systemintegrators; however, this increased freedom can result in <strong>mezzanine</strong>/baseboard incompatibility issues<strong>for</strong> end users. Now <strong>VITA</strong> <strong>46.9</strong>, a subsidiary specification of <strong>VPX</strong>, steps into the front line by solvingXMC and PMC I/O mapping issues and increasing <strong>interoperability</strong> among vendors.The <strong>VITA</strong> 46 (<strong>VPX</strong>) family of standardsdefines an embedded computer modulethat builds on the utility of the VMEbusEurocard <strong>for</strong>m factor by providing a seriesof high-speed, fabric capable backplaneMultiGig RT-2 connectors, in lieu of theconventional DIN pin and socket connectors.Proper use of these connectors<strong>for</strong> a variety of backplane signaling standardsis defined further in the <strong>VPX</strong> “dot”subsidiary specifications. These “dot”standards dictate the type of connectorpopulated at each allowable location ona <strong>VPX</strong> card and the interface signal mappingsof the different serial fabric options.<strong>VPX</strong> cards, like earlier VME boards,will typically provide <strong>mezzanine</strong> cardinstallation sites <strong>for</strong> the addition of application-specificfunctions. PCI MezzanineCard (PMC) and/or Switched MezzanineCard (XMC) <strong>mezzanine</strong>s may be optionallyinstalled on the <strong>VPX</strong> card, dependingon the functionality designed into thebase plug-in module or “carrier” by thedesigner. <strong>VITA</strong> provides several standards<strong>for</strong> bus signaling on PMC and XMC cardsto ensure <strong>interoperability</strong> among boardvendors. These standards also define the“user I/O” connector contacts that areavailable to the <strong>mezzanine</strong> card designer.<strong>VITA</strong> <strong>46.9</strong> is one such standard, definingthe differential pairs to be used inmapping <strong>mezzanine</strong> I/O to the <strong>VPX</strong> backplaneconnectors.<strong>VITA</strong> <strong>46.9</strong> to the <strong>for</strong>efrontIn the past, the failure to define the consistentusage of I/O pins has createdproblems resulting in <strong>mezzanine</strong> cardsthat were incompatible with certainbaseboards. In the VME specification,I/O signals <strong>for</strong> the VME P0 and P2 wereonly defined <strong>for</strong> single-ended configuration.Single-ended signaling is typicallyused on PMC <strong>mezzanine</strong> cards to addresscommon I/O interfaces that do not requiretightly controlled signal environments.Consequently, differential I/O signalswere left undefined, which encourageddifferent vendors to use different <strong>pinout</strong>schemes. This resulted in a variety ofproblems <strong>for</strong> end users. For example, insome cases <strong>mezzanine</strong> cards would onlywork with certain specific baseboards.Also, in some cases, <strong>mezzanine</strong> modulesrequired different layouts depending onwhether the module was to be installed inthe baseboard’s PMC site 1 or in site 2.One layout would be needed to match P0and a different one to match P2.The <strong>VPX</strong> working group, armed withknowledge of past problems resultingfrom the lack of definition <strong>for</strong> differentialI/O signals <strong>for</strong> VME P0 and P2, decidedto eliminate the confusion experienced byearlier VME users and solve the problemby defining differential I/O <strong>pinout</strong> in the<strong>VPX</strong> specification. The alternative mighthave resulted in the emergence of numerouscompeting I/O options that couldhamper <strong>interoperability</strong>.ForSinglePrintOnlyThe <strong>VPX</strong> working group, to addressthis problem, has created the <strong>VITA</strong> <strong>46.9</strong>“dot-spec,” which defines the standarddifferential pairs to be used <strong>for</strong> mapping<strong>mezzanine</strong> I/O to the <strong>VPX</strong> backplaneconnectors. The working groupalso ensured that the resulting differentialAdvantages of <strong>VPX</strong> over legacy VMEAdvantageWhile VME has long been the bus architecture of choice<strong>for</strong> military and aerospace applications, recent advancesin technologies, particularly in interconnects, have demonstratedthe need <strong>for</strong> an advance in system development. Thenew <strong>VPX</strong> (<strong>VITA</strong> 46) and <strong>VPX</strong>-REDI (<strong>VITA</strong> 48) bus architecturespecifications update the VMEbus legacy to provide support<strong>for</strong> high-speed switched serial fabrics, such as Serial RapidIO(SRIO) and PCI Express, and support distributed processingat speeds and in network configurations unreachable byVME64x.One of the key advantages of <strong>VPX</strong> over legacy VME is thegreater number of I/O pins that it makes available to endusers. This gives integrators the freedom to define I/O asthey need to add market differentiation and meet the requirementsof unique applications. The increased backplane I/Oprovided by <strong>VPX</strong> also makes it possible <strong>for</strong> some of theseextra I/O pins to be allocated to additional XMC and PMCcard I/O. This is in contrast to VME and some other newerstandards that provide only limited backplane I/O.In fact, <strong>VPX</strong> is the only bus architecture <strong>for</strong>mat that definesa standard approach <strong>for</strong> XMC I/O to the backplane. <strong>VPX</strong>offers another benefit to XMC module users resulting fromits use of Tyco’s MultiGig RT-2 connectors, greatly improvingsignal integrity <strong>for</strong> rear-panel <strong>mezzanine</strong> I/O compared toVME or CompactPCI connectors. Also, the XMC Pn6 connectorprovides superior per<strong>for</strong>mance to the PMC Pn4 <strong>mezzanine</strong>connector because standard mapping provides interveninggrounds and significant physical separation between pairs.VME and Critical Systems ©2007 OpenSystems Publishing. Not <strong>for</strong> Distribution.

<strong>VPX</strong> ... Almost REDIHardware<strong>pinout</strong> mapping would be symmetrical,<strong>for</strong> example, work on either a 6U <strong>VPX</strong>P3/4 set or on a P5/6 set. In addition, theworking group also defined differential<strong>pinout</strong> usage <strong>for</strong> 3U <strong>VPX</strong> cards and theirP1/2 set. The result is that <strong>VITA</strong> <strong>46.9</strong>solves XMC/PMC I/O mapping on <strong>VPX</strong>and ensures and greatly simplifies the<strong>interoperability</strong> of basecards and <strong>mezzanine</strong>I/O cards from different vendors.“<strong>VITA</strong> <strong>46.9</strong> ensures<strong>interoperability</strong> whileproviding flexibility byoffering a number ofstandard combinations.”Innerworkings of <strong>VITA</strong> <strong>46.9</strong>The objective of the <strong>VITA</strong> <strong>46.9</strong> standard isto supplement the <strong>VITA</strong> 46.0 base standardto fully define the user I/O signal mappingbetween the pins of PMC and/or XMC cardsites provided on a <strong>VPX</strong> compliant carrier<strong>for</strong> both 3U and 6U modules. In addition,it defines the fabric mapping <strong>for</strong> a 3Umodule and placement <strong>for</strong> two channelsof GbE 1000BASE-T. <strong>VITA</strong> <strong>46.9</strong> ensures<strong>interoperability</strong> while providing flexibilityby offering a number of standard combinations.The following combinations weredetermined the most likely to be actuallyimplemented in practice: PMC Jn4 assigned to 3U V46-P2differential and single-endedconnector XMC Jn6 assigned to 3U V46-P2differential connector PMC Jn4 assigned to 6U V46-P3,5 differential connector XMC Jn6 assigned to 6U V46-P3/4,5/6 differential connectorTo accommodate this, various mappingpatterns have been defined: P64s – Maps all 64 contacts ofPMC-Jn4 to <strong>VPX</strong> differential wafers. X12d – Maps 12 selected differentialpairs of XMC-Jn6 to <strong>VPX</strong> differentialwafers. X20d24s – Maps all 20 differentialpairs of XMC-Jn6 and 24 single-endedpairs to <strong>VPX</strong> differential wafers. Thispattern fits within one <strong>VPX</strong> connector. X20d38s – Maps the entire XMCconnector to <strong>VPX</strong> differential wafers.This consists of all 20 differential pairsof XMC-Jn6 and all 38 single-endedsignals.For 6U cards, several overall configurationscan be accommodated by selectingfrom the previously defined mappingpatterns (see Figure 1): <strong>VPX</strong> P3/P5 mapped to PMCJn4 using the P64s and P4/P6 mappedto the XMC Jn6 using the X12dpattern <strong>VPX</strong> P3/4, P5/6 mapped to XMCJn6 using the X20d38s pattern6U <strong>VPX</strong> ModuleXMC/PMC ModuleJn5 Jn1 Jn2Jn6Jn3X20d38sJn4X12dJn5 Jn1 Jn2X20d38sJn6 Jn3 Jn4X12dP64sP64sFigure 1keyP0P1P2keyP3P4P5P6keyFor 3U cards, the following configurationsare supported, as shown in Figure 2: <strong>VPX</strong> P2 mapped to PMC Jn4 usingthe P64s and P1 mapped to the XMCJn6 using the X12d pattern <strong>VPX</strong> P2 mapped to X20d24s3U <strong>VPX</strong> ModuleXMC/PMC ModuleJ15 J11 J12J16J13X12dJ14X20d24sP64sFigure 2keyP0P1P2keyFigures 1 and 2 both show all configurationsmapped on a carrier card. However,in practice, only one configuration willbe mapped at a time. For example, a <strong>VPX</strong>carrier card that supports only a PMC<strong>mezzanine</strong> will only use the P64s mappingas it will only have Jn4 installed.For a <strong>VPX</strong> carrier card that supportsonly XMC Jn6, then the X20d38s mappingwill be used in the 6U case and theX20d24s mapping will be used in the3U case. For a <strong>VPX</strong> carrier card that supportsboth XMC Jn6 and Jn4, then P64sand X12d would be mapped.ForSinglePrintOnlyVME and Critical Systems ©2007 OpenSystems Publishing. Not <strong>for</strong> Distribution.<strong>VITA</strong> <strong>46.9</strong> mapping patternsexploredThe mapping pattern P64s is relativelystraight<strong>for</strong>ward. The P64s maps the 64 Jn4I/O pins on a PMC <strong>mezzanine</strong> to the <strong>VPX</strong>RT2 connector. The 64 pins are arrangedas two rows of 32 pins each. One columnis labeled odd and the other even. Inselecting the differential pairs, the workinggroup selected pins next to each otheras differential pairs. That is, pins 1-3are considered a differential pair and pins2-4 are considered a differential pair.This approach was taken to ease matchedlength routing on the PMC module and thecarrier card. These pins are then mappedto the <strong>VPX</strong> RT2 connector.

Hardware<strong>VPX</strong> ... Almost REDIThe mapping pattern X12d was a morecomplex challenge. The X12d maps12 differential pairs of the XMC Jn6connector to the RT2 connector. Theworking group chose 12 differential pairsas a good tradeoff between the amount ofXMC I/O mapped to the MultiGig RT-2connector versus the number of I/O linesleft over <strong>for</strong> use by the host card itself. Theworking group spent much time debatingthis mapping. The main issue was which12 pairs should be mapped? The XMCJn6 connector is an open field connectorarranged as 6 columns (A to G) and19 rows of pins, <strong>for</strong> a total of 114 pins.Much signal integrity work was done inthe XMC working group. It showed that20 differential pairs can be obtained byplacing them on the odd rows on columnsAB, DE with grounds on the even rows ofthose same columns. The XMC workinggroup further defined that rows 1,3,5,7were to be transmit lines and 11,13,15,17were to be receive lines. This approachprovides an XMC <strong>mezzanine</strong> card with theability to support up to eight lanes of serialtx/rx traffic. The working group decidedto stay with this pattern and allowed8 differential pairs <strong>for</strong> a fabric port onrows 1,3 and 11,13 and assigned theremaining 12 pairs <strong>for</strong> the X12d backplaneI/O pattern.The patterns X20d24s and X20d38s hencefell out from this ef<strong>for</strong>t once the X12dpattern was defined. The X20d24s patternmaps 20 pairs and 24 single-ended pinsfrom columns C and F to a single RT-2connector. The X20d38s pattern maps20 pairs and 38 single-ended pins fromcolumns C and F over two RT-2 connectors.Note that the X20d38s pattern maps78 pins to the RT-2 connector. This is thefull complement of pins on the 114 pinXMC connector as the rest are dedicatedto grounds.<strong>VITA</strong> <strong>46.9</strong> speeds futuredevelopmentBy ensuring that <strong>mezzanine</strong> I/O differentialpair mapping was defined in the<strong>VPX</strong> specification – and particularly<strong>VITA</strong> <strong>46.9</strong> – the <strong>VPX</strong> working group hasensured that <strong>mezzanine</strong>, basecard, andbackplane/chassis designers will have theproper in<strong>for</strong>mation to enable them to designinteroperable PMC and XMC I/O <strong>mezzanine</strong>cards. This will help ease the adoptionof new high-speed <strong>VPX</strong> and <strong>VPX</strong>-REDIapplications, paving a smoother pathto the future <strong>for</strong> the end users of today’schallenging applications. CSJing Kwok isprincipal engineerin the TechnologyGroup at Curtiss-Wright ControlsEmbeddedComputing. Hehas been involvedwith VMEbus standards work <strong>for</strong> thepast 15 years. He is editor of one ofthe <strong>VITA</strong> 46 “dot” specifications nowin working group ballot and was oneof the chapter editors <strong>for</strong> the VME64specification. Jing is a graduate ofthe British Columbia Institute ofTechnology.For more in<strong>for</strong>mation, contact Jing at:Curtiss-Wright ControlsEmbedded Computing333 Palladium Drive, m/s 385Kanata, ON, Canada K2V-1A6613-599-9199, Ext. 5825jing.kwok@curtisswright.comwww.cwcembedded.comForSinglePrintOnlyVME and Critical Systems ©2007 OpenSystems Publishing. Not <strong>for</strong> Distribution.