Three-Phase PWM Rectifier with Constant Switching Frequency

Three-Phase PWM Rectifier with Constant Switching Frequency

Three-Phase PWM Rectifier with Constant Switching Frequency

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

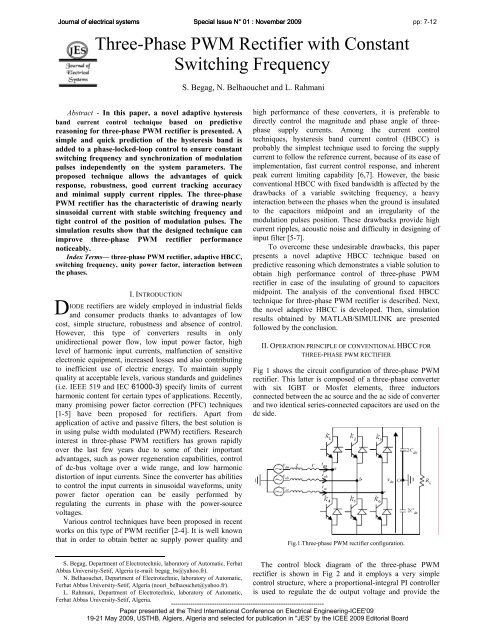

Journal of electrical systems Special Issue N° 01 : November 2009pp: 7-12II.2. Capacitors midpoint <strong>with</strong>out connection to the groundSince the dc bus capacitors midpoint “O” is normallyfloating to avoid the third current harmonic in the neutralpoint, the previous analysis now will be extended to allowfor floating point “O”.When point “O” is floating, the relationship for phase avoltage and current can be reformulated as:adaptive bandwidth digital control is added which ensuresconstant switching frequency. Fig. 4 shows the adaptation ofthe hysteresis band for two consecutive modulation periods[5, 8, 9].disav + v + L + ri = v(10)a o sa sadtWhere vois the voltage of point “O” referred to theground; its expression is given as:( va+ v + vc)bvo= (11)3Subtracting (10) from (2) gives:dδ+ = (12)dta*L rδ v − v + va a a o(12) Shows that, due to the action of voltage v o, eachphase current error is affected by the commutations in theother phases. This interference causes severe irregularities inthe ordinary hysteresis operation.From (3), the current error i*− i can be decoupled intosa satwo parts as:* ' ''aisa isa =− a a'aδ = δ + δ(13)where: δ : non interacting error and δ : interacting errorThe equation of interacting error is:''dδa ''L + rδa= vo(14)dtAn interference-free modulation can be obtained if thehysteresis control is performed on the non interacting erroras:'ad δ' *L + rδa= v −v(15)dta a(15) shows that δ ' only depends on the correspondingavoltage v , similar to (5) if the effect of the input inductoraresistance r is neglected. Hence error δ can be treated inthe same way as the error δain the case of capacitivemidpoint “O” connected to ground. We can see that the'' '' ''three-phase interacting errors are same ( δ = δ = δ ).''a'aFig.4. Bandwidth control algorithm.From Fig.4, we deduce the following equations:⎧β a = Sp. Ton = Sn.T⎪off⎨(17)T = T + T⎪⎩on offWhere spand snare the positive and negative slopes of'the non interacting error δ in modulation period.aFor a switching period corresponding to k , we have:Sp( k) + Sn( k)Tk ( ) = βa( k).(18)S ( k). S ( k)pnFor a switching period corresponding to k + 1 , theequation (18) is written:Sp( k + 1) + Sn( k+1)Tk ( + 1) = βa( k+1).(19)S ( k + 1). S ( k+1)pFor two consecutive switching periods, we have thefollowing simplifying:Sp( k) = Sp( k + 1)(20)S ( k) = S ( k+1)nnFrom (18), (19) and (20), we can derive the controlequation:Tk ( + 1)βa( k + 1) = βa( k).(21)Tk ( )The principle of control given by equation (21) is to keepa b cthe switching period constant, where T( k + 1) is the desiredswitching period which we want to impose and T( kis ) theIII. DEVELOPMENT OF PREDICTIVE ADAPTIVE HBCC measured one, i.e. to define the switching period T( k + 1) weIII.1. <strong>Constant</strong> switching frequency controlpredict at time k the bandwidth β ( 1)a k + and hence thisTo obtain a constant switching frequency (1/ T d ) , thereasoning is intended to evaluate the proper bandwidth toachieve the error between the real switching period and thehysteresis band β has to be dynamically modified desired switching period equal to zero. This reasoning leadsaaccording to this equation:to an algorithm which is equivalent to a first order dead-beatcontrol of the switching period.vdcTd2β a = (1 − vna)(16) The control algorithm is very simple and it is able to4. Lensure a good switching frequency regulation <strong>with</strong> anyThe controller maintains its analog structure, but an knowledge on the system parameters, but it cannot control-----------------------------------------------------------------------Paper presented at the Third International Conference on Electrical Engineering-ICEE'0919-21 May 2009, USTHB, Algiers, Algeria and selected for publication in "JES" by the ICEE 2009 Editorial Boardn

Journal of electrical systems Special Issue N° 01 : November 2009pp: 7-12the position of modulation pulses. This means that thedistribution of the modulation pulses inside the modulationperiod is random.III.2. <strong>Switching</strong> pulses regulationNow we make an additional improvement by introducinga synchronization of modulation pulses. This is based onadding a modification to equation (21), where the phaseerror between an external clock and the control signalcontributes to ensure a good regulation of modulation pulsesposition. The solution is to implement the PLL, generally,this is the effective solution to synchronize two signals if thestability conditions are respected [10, 11].The PLL is a device which causes one signal to trackanother one, it keeps the output signal synchronized <strong>with</strong> areference input signal in frequency as well as in phase. Moreprecisely. The PLL is simply a servo system, which controlsthe phase of its output signal in such a way that the phaseerror between output phase and reference phase reduces to aminimum. The basic fundamental block diagram of PLLconsists of a phase detector, a loop filter and a voltagecontrolled oscillator (VCO). In this case, the PLL blockscheme used to modify the equation (21) is shown in Fig. 5and it is composed of a phase detector to detect the phaseerror between the reference clock <strong>with</strong> frequency fdand theoutput switching signal <strong>with</strong> frequency f , a proportionalintegral(PI) filter and employs the hysteresis comparator(HC) as VCO.When locked to a suitable clock signal, the PLL not onlyensures constant modulation frequency, but also minimizesthe phase displacement Δφbetween the output voltagepulses and the external clock. In three-phase insulatedground systems, the optimal reduction of the current ripplecorresponds to center of the modulation pulses [12, 13]. Inthis case, the phase error Δφis defined as the time betweenthe center of pulse modulation and the reference clock.The PLL loop gives the phase error and hence gives thenecessary compensating bandwidth to ensure a constantswitching frequency and effective lock of modulation pulsesto clock as it is well presented in Fig. 5.Finally, from Fig. 5, it can be derived:β = βa Pa+ βdba(22)Ki+ sKpβPa= ( ).Δ φ(23)sKi+ sKpWhere ( ) is the transfer function of PI filter.sNow, the control equation (21) becomes:Ki + sKp ΔφTdβ ( k + 1) = (1 + . ). . β ( k)(24)dbaTas d T(24) shows the modified dead-beat control law <strong>with</strong> β Paisthe compensating bandwidth given by PLL loop, βdbais thebandwidth given by dead-beat control and β ais the totalbandwidth obtained after correction. Similar expressions ofhysteresis bands can be written for the other phases b and c.Fig. 5. Block scheme of the predictive adaptive HBCC for phase a.IV. SIMULATION RESULTS AND DISCUSSIONSDuring this simulation, we used the parameters which areindicated in table 1.TABLE IDesign specifications and circuit parametersDesired switching frequencySource voltage frequencyac supply voltage peakdc-bus voltageInput resistance rInput inductance LLoad resistance R Ldc-bus capacitorCdc5 KHz50 Hz120 V300V0.2 Ω11.5 mH100 Ω2000 μ FTo verify the performances of the proposed predictiveadaptive HBCC compared to the conventional fixed HBCC,the simulation results are shown in fig. 6 through fig. 13.Fig. 6 shows the supply current and current errorwaveforms of a-phase for conventional fixed HBCC, wherethe fixed band was set to achieve a maximum switchingfrequency of 5 KHz when there is no interaction between thephases. Due to the interaction of three-phase currentcontrollers, the supply current instantaneous error can gobeyond hysteresis band βaand reach up to 2β a, this showsthat the supply current has high ripples. The supply currentand current error waveforms for adaptive HBCC are shownin Fig. 7. In this case the supply current ripples areminimized. The interacting error and non-interacting errorwaveforms for adaptive HBCC are shown in Fig. 8.The supply current FFT for conventional HBCC andadaptive HBCC are shown in Fig. 9 and Fig. 10 respectively.In conventional HBCC, the supply current harmonics arewidely distributed from hundreds of Hertzs to severalkiloHertz frequency and the THD (total harmonic distortion)is higher (10.52%). However, for adaptive HBCC, aswitching frequency is held in 5 kHz, thus the supply currentharmonics are concentrated around 5 kHz frequency and theTHD is reduced to 3.78%. This provides predictability of theconverter input current harmonics, avoids resonanceproblem and makes the filter design task easier.-----------------------------------------------------------------------Paper presented at the Third International Conference on Electrical Engineering-ICEE'0919-21 May 2009, USTHB, Algiers, Algeria and selected for publication in "JES" by the ICEE 2009 Editorial Board