Random Number Generator Using Various Techniques through VHDL

Random Number Generator Using Various Techniques through VHDL

Random Number Generator Using Various Techniques through VHDL

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

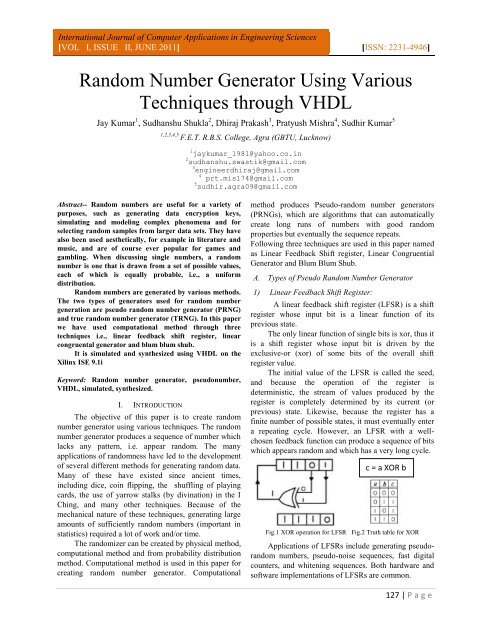

International Journal of Computer Applications in Engineering Sciences[VOL I, ISSUE II, JUNE 2011] [ISSN: 2231-4946]<strong>Random</strong> <strong>Number</strong> <strong>Generator</strong> <strong>Using</strong> <strong>Various</strong><strong>Techniques</strong> <strong>through</strong> <strong>VHDL</strong>Jay Kumar 1 , Sudhanshu Shukla 2 , Dhiraj Prakash 3 , Pratyush Mishra 4 , Sudhir Kumar 51,2,3,4,5F.E.T. R.B.S. College, Agra (GBTU, Lucknow)1 jaykumar_1981@yahoo.co.in2 sudhanshu.swastik@gmail.com3 engineerdhiraj@gmail.com4 prt.mis174@gmail.com5 sudhir.agra09@gmail.comAbstract-- <strong>Random</strong> numbers are useful for a variety ofpurposes, such as generating data encryption keys,simulating and modeling complex phenomena and forselecting random samples from larger data sets. They havealso been used aesthetically, for example in literature andmusic, and are of course ever popular for games andgambling. When discussing single numbers, a randomnumber is one that is drawn from a set of possible values,each of which is equally probable, i.e., a uniformdistribution.<strong>Random</strong> numbers are generated by various methods.The two types of generators used for random numbergeneration are pseudo random number generator (PRNG)and true random number generator (TRNG). In this paperwe have used computational method <strong>through</strong> threetechniques i.e., linear feedback shift register, linearcongruental generator and blum blum shub.It is simulated and synthesized using <strong>VHDL</strong> on theXilinx ISE 9.1iKeyword: <strong>Random</strong> number generator, pseudonumber,<strong>VHDL</strong>, simulated, synthesized.I. INTRODUCTIONThe objective of this paper is to create randomnumber generator using various techniques. The randomnumber generator produces a sequence of number whichlacks any pattern, i.e. appear random. The manyapplications of randomness have led to the developmentof several different methods for generating random data.Many of these have existed since ancient times,including dice, coin flipping, the shuffling of playingcards, the use of yarrow stalks (by divination) in the IChing, and many other techniques. Because of themechanical nature of these techniques, generating largeamounts of sufficiently random numbers (important instatistics) required a lot of work and/or time.The randomizer can be created by physical method,computational method and from probability distributionmethod. Computational method is used in this paper forcreating random number generator. Computationalmethod produces Pseudo-random number generators(PRNGs), which are algorithms that can automaticallycreate long runs of numbers with good randomproperties but eventually the sequence repeats.Following three techniques are used in this paper namedas Linear Feedback Shift register, Linear Congruential<strong>Generator</strong> and Blum Blum Shub.A. Types of Pseudo <strong>Random</strong> <strong>Number</strong> <strong>Generator</strong>1) Linear Feedback Shift Register:A linear feedback shift register (LFSR) is a shiftregister whose input bit is a linear function of itsprevious state.The only linear function of single bits is xor, thus itis a shift register whose input bit is driven by theexclusive-or (xor) of some bits of the overall shiftregister value.The initial value of the LFSR is called the seed,and because the operation of the register isdeterministic, the stream of values produced by theregister is completely determined by its current (orprevious) state. Likewise, because the register has afinite number of possible states, it must eventually entera repeating cycle. However, an LFSR with a wellchosenfeedback function can produce a sequence of bitswhich appears random and which has a very long cycle.c = a XOR bFig.1 XOR operation for LFSR Fig.2 Truth table for XORApplications of LFSRs include generating pseudorandomnumbers, pseudo-noise sequences, fast digitalcounters, and whitening sequences. Both hardware andsoftware implementations of LFSRs are common.127 | P a g e

Kumar et. al.i) Mathematical analysis of LFSRIt is known that a Linear Feedback Shift Register LFSRassociated with its characteristic polynomial G[x] oforder n can generate a very good random like binaryvariable of periodicity 2n-1 [2]. Associating qindependent LFSRs generate a q bit variable Uquniformly distributed over {0, 1, 2... 2q-1}. The LFSRdesign in FPGA need only n logic cells, each of themwith its own register. Figure 2, illustrates the LFSRstructure called "one to many" with the polynomial x5 +x2+1:secondly a - 1is divisible by all prime factors of m, andthirdly a-1 is a multiple of 4 if m is a multiple of 4.While LCGs are capable of producing decentpseudorandom numbers, this is extremely sensitive tothe choice of the coefficients c, m, and a.3) Blum Blum Shub:Blum Blum Shub (BBS) is a pseudorandom numbergenerator proposed in 1986 by Lenore Blum, ManuelBlum and Michael Shub (Blum et al., 1986).Blum Blum Shub takes the form:Figure 2. LFSR for X5 + X2 + 1At every clock cycle, 4bits are used as outputs and"shifted". For instance for the LFSR of Figure 2, t beingthe clock period, the register x5 can be expressed asx5(t)= x4(t-1) = x2(t-3)+x5(t-3) = x(t-4)+x4+(t-4). Byconsidering operations every 4t, 4 virtual shiftoperations are done in one clock cycle. This techniquecan be easily coded in <strong>VHDL</strong> and generates almost noextra FPGA logic cell.2) Linear Congruential <strong>Generator</strong>:A Linear Congruential <strong>Generator</strong> (LCG)represents one of the oldest and best-known pseudonumber generator algorithms. The theory behind them iseasy to understand, and they are easily implemented andfast. However, their statistical properties are muchworse than more recent generators, including generatorswith similar simplicity and speed.The generator is defined by the recurrence relation:Where, Xn is the sequence of pseudorandomvalues, andm, 0 < m— The "modulus"a, 0 < a < m The "multiplier"c, 0 ≤ c < m— The "increment" (the specialcase of c = 0 corresponds to Park-Miller RNG)X o , 0 ≤ X o < m The "seed" or "start value" areinteger constants that specify the generator.The period of a general LCG is at most m, and forsome choices of a much less than that. Provided that c isnonzero, the LCG will have a full period for all seedvalues if and only if firstly c and m are relatively prime,Where n=p × q is the product of two large primes p andq. At each step of the algorithm, some output is derivedfrom X n+1 ; the output is commonly the bit parity of X n+1or one or more of the least significant bits of X n+1 . Thetwo primes, p and q, should both be congruent to 3 (mod4) (this guarantees that each quadratic residue has onesquare root which is also a quadratic residue) and gcd(φ(p-1), φ(q-1)) should be small (this makes the cyclelength large).Fig. 3 Block diagram for the program flowII. <strong>VHDL</strong><strong>VHDL</strong> is an acronym for VHSlC HardwareDescription Language (VHSIC is an acronym for VeryHigh Speed Integrated Circuits). It is a hardwaredescription language that can be used to model a digitalsystem at many levels of abstraction ranging from thealgorithmic level to the gate level. The complexity of thedigital system being modelled could vary from that of asimple gate to a complete digital electronic system, oranything in between. The digital system can also bedescribed hierarchically. Timing can also be explicitlymodelled in the same description. The language not onlydefines the syntax but also defines very clear simulationsemantics for each language construct. Therefore,models written in this language can be verified using a<strong>VHDL</strong> simulator. It is a strongly typed language and is128 | P a g e

<strong>Random</strong> <strong>Number</strong> <strong>Generator</strong> <strong>Using</strong> <strong>Various</strong> <strong>Techniques</strong> <strong>through</strong> <strong>VHDL</strong>often verbose to write. It inherits many of its features,especially the sequential language part, from the ADAprogramming language. Because <strong>VHDL</strong> provides anextensive range of modelling capabilities, it is oftendifficult to understand.A. LFSRIII. RESULTThe above diagram shown is simulation diagramfor LFSR which contain three input pins enable, clk&reset and one output pin, cout. When reset pin is at‗high (1)‘, no output is generated accept ‗0‘. As soon asreset pin gets down to ‗ground (0)‘, the randomsequences appear to be generated but when enable andclk input pins are at ‗high (1)‘. Because of the finitestate of shift register, these random sequence has a longrepeated cycle.B. LCGFig.4 Simulation Diagram for LFSRFigure shown below is the test bench waveform forlinear feedback shift register in which clk represents therising clock pulse given to the system; c_out is the portwhere we take our output. In this generator we havemade two processes in which is to provide the delay andother for the the main program.C. BBSFig.5 Simulation Diagram for LCGThe simulation diagram for blum blum shub isshown above. This diagram shows that the bit stream isgenerated which constitute a number. The output bitsequence are in random manner which is produced whenleast significant bit (LSB) is counted for the expressionXi = (Xi-1) 2 mod n for every value of i.Fig.6 Simulation Diagram for BBSIV. CONCLUSIONFinally the result have been displayed above inwhich we have found that linear feedback shift registeris very low memory cost consuming, which has a seedvalue to initiate the random number generation. Linearfeedback shift register have long cycle duration togenerate random as true random number generator. It ismore suitable for cryptography.Blum blum shub generates random numbergenerator more securely for the cryptograph but notmemory cost efficient, it also uses seed value but withconstraints.Linear Congruential <strong>Generator</strong> found to be most inefficient techniques with maximum memory usage.REFERENCES[1] Doughlas L. Perry ―<strong>VHDL</strong> programming by example‖[2] E.R. Berlekamp, "Algebric Coding Theory", McGraw-Hill[3] I.Vattulainen, K. Kankaala, J. Saarinen, and T. Ala- Nissila,A Comparative study of pseudorandom number generators,Computer Phys. Comm. 86 (1995) 209-226[4] Mustapha Abdulai, Inexpensive Parallel <strong>Random</strong>[5] <strong>Number</strong> <strong>Generator</strong> for Configurable Hardware 2003.[6] Paul Graham and Brent Nelson. Genetic algorithms in softwareand in hardware-a performance analysis of workstation andcustom computing machine implementations. In Kenneth L.Pocek and Jeffrey Arnold, editors, Proceedings of the FourthIEEE Symposium of FPGAs for Custom Computing Machines.,Pages 216–225, Napa Valley, California, April 1996. IEEEComputer Society Press.[7] Peter J. Ashenden ―<strong>VHDL</strong> tutorial‖[8] Tsutomu Maruyama, Terunobu Funatsu,[9] Minenobu Seki, Yoshiki Yamaguchi, and Tsutomu Hoshino. AField-Programmable Gate-Array system for EvolutionaryComputation. IPSJ Journal, 40(5), 1999.[10] Wikipedia, Psuedorandom <strong>Number</strong> <strong>Generator</strong>s,[11] wikipedia.com/wiki/Pseudorandom_number_generator[12] Xilinx. Pseudo random number generator.[13] www.xilinx.com/xcell/xl35/xl35_44.pdf, December 2001.129 | P a g e