Exercise 1 - Fault Simulation

Exercise 1 - Fault Simulation

Exercise 1 - Fault Simulation

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

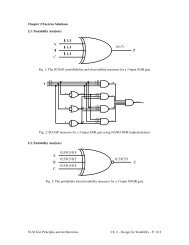

<strong>Exercise</strong> 2 - ATPG2.1 ATPG for s-a faults in combinational circuits• 使 用 軟 體 :SYNTEST tool – “asicgen”• 範 例 電 路 :c17.v – an ISCAS85 benchmark circuit• 練 習 步 驟 :1. 本 次 練 習 開 始 前 請 先 執 行< 指 令 > cp –r ~testta/test_course/ex2 .2. 建 好 將 來 會 用 到 的 子 目 錄< 指 令 > mkdir designs3. 把 c17 的 Verilog 檔 轉 換 成 SYNTEST 的 資 料 格 式< 指 令 1> vlogin c17.v –opath designs本 指 令 可 將 c17.v 轉 成 SYNTEST 資 料 格 式 的 c17.sdb, 並 存 於 -opath 所指 定 的 designs 子 目 錄 下 。< 指 令 2> expin c17把 c17.sdb 經 由 link 與 flatten 後 在 designs 子 目 錄 下 產 生 c17.x.sdb 及c17.c.sdb。4. ATPG:< 指 令 > asicgen c17 –non_scan-non_scan 表 示 電 路 未 加 scan。 程 式 會 依 照 電 路 是 否 含 有 記 憶 元 件 (e.g.,D flip-flop) 來 決 定 是 用 sequential 還 是 combinational ATPG algorithm 來產 生 patterns。 本 練 習 的 c17 電 路 為 combinational 電 路 , 裡 面 沒 有 任 何記 憶 元 件 , 故 用 combinational algorithm。要 看 指 令 相 關 說 明 , 請 打 :asicgen -help< 執 行 結 果 > 產 生 c17.rpt、c17.tp、c17.udt、c17.hdt… 等 檔 案觀 察 c17.rpt 的 內 容 :.....1

This circuit has 6 test patterns and contains 22 faults of which22 (100.00%) faults were Hard detected (HD).0 ( 0.00%) data faults were Potentially testable (PT).0 ( 0.00%) clock/enable faults were Potentially untestable (PU).0 ( 0.00%) Untestable (UT) faults were Ignored (IG) or Tied to VCC/GND.0 ( 0.00%) Untestable (UT) faults were Uncontrollable.0 ( 0.00%) Untestable (UT) faults were Blocked (Unobservable).0 ( 0.00%) Untestable (UT) faults were due to circuit design.0 ( 0.00%) clock/enable faults were Aborted for backtrack count exceeding 10000.0 ( 0.00%) data faults were Aborted for backtrack count exceeding 10000.atpg pessimistic fault coverage = HD/(Total-IG) = 100.0000 %.atpg pessimistic test coverage = HD/(Total-UT) = 100.0000 %.atpg pessimistic test efficiency = (HD+UT)/Total = 100.0000 %.atpg optimistic fault coverage = (HD+PT)/(Total-IG) = 100.0000 %.atpg optimistic test coverage = (HD+PT)/(Total-UT-PU) = 100.0000 %.atpg optimistic test efficiency = (Total-Abort)/Total = 100.0000 %.This circuit has 6 test patterns and contains 50 UNCOLLAPSED faults of which50 (100.00%) faults were Hard detected (HD).0 ( 0.00%) data faults were Potentially testable (PT).0 ( 0.00%) clock/enable faults were Potentially untestable (PU).0 ( 0.00%) Untestable (UT) faults were Ignored (IG) or Tied to VCC/GND.0 ( 0.00%) Untestable (UT) faults were Uncontrollable.0 ( 0.00%) Untestable (UT) faults were Blocked (Unobservable).0 ( 0.00%) Untestable (UT) faults were due to circuit design.0 ( 0.00%) clock/enable faults were Aborted for backtrack count exceeding 10000.0 ( 0.00%) data faults were Aborted for backtrack count exceeding 10000.atpg pessimistic fault coverage = HD/(Total-IG) = 100.0000 %.atpg pessimistic test coverage = HD/(Total-UT) = 100.0000 %.atpg pessimistic test efficiency = (HD+UT)/Total = 100.0000 %.atpg optimistic fault coverage = (HD+PT)/(Total-IG) = 100.0000 %.atpg optimistic test coverage = (HD+PT)/(Total-UT-PU) = 100.0000 %.atpg optimistic test efficiency = (Total-Abort)/Total = 100.0000 %.可 以 發 現 ATPG 產 生 的 6 個 patterns 可 以 使 collapsed 或 uncollapsed 的fault coverage 都 達 到 100%。c17.tp 是 ATPG 所 產 生 的 test patterns, 格 式 類 似 練 習 一 的 .stm 檔 案 , 內容 如 下 :-STEM-outputsinputsxxxxxxx221236723gggggggaaaaaaattttttt1 S LHLLL++2 S HLHHH+-3 S LHHHL--4 S HLLLL--5 S LHLHH++6 S HLHLH++其 中 的 +,– 分 別 代 表 logic 1, 0, 用 於 output ports上 , 為 該 pattern 預 計 會 有 的 輸 出 結 果 。如 :pattern 1 即 表 示 ─(x1gat, x2gat, x3gat, x6gat, x7gat)=(0,1,0,0,0) 時 ,(x22gat, x23gat) 預 計 會 有 (1,1) 的 輸 出5. 產 生 Verilog testfixture file< 指 令 > tpout c17 –vlog-vlog 表 示 會 輸 出 Verilog 格 式 的 檔 案 。 執 行 後 會 產 生 c17.tpout.rpt 及c17.drv.v。c17.tpout.rpt 記 錄 了 輸 出 的 訊 息 ;c17.drv.v 則 為 testfixture file, 會去 讀 取 c17.vector 裡 所 記 錄 的 test patterns。2

如 果 要 用 該 Verilog 測 試 檔 來 驗 証 產 生 的 test patterns 是 否 能 真 正 work, 請 下指 令 :source /usr/cadence/cic_setup/ldv.cshverilog c17.drv.v c17.v如 果 看 到 以 下 畫 面 即 表 示 ATPG 沒 有 問 題 :*** Test vectors simulated : 6*** Number of vector mismatch : 02.2 ATPG for s-a faults in sequential circuits• 使 用 軟 體 :SYNTEST tool – “asicgen”• 範 例 電 路 :s382.v – an ISCAS89 benchmark circuit• 練 習 步 驟 :1. 建 好 將 來 會 用 到 的 子 目 錄< 指 令 > mkdir designs lib2. 把 s382 的 Verilog 檔 轉 換 成 SYNTEST 的 資 料 格 式< 指 令 1> vlogin s382.v –opath designs –lib 35.v lib.v udp.v“-lib 35.v lib.v udp.v” 會 把 35.v 等 檔 案 的 內 容 轉 成 SYNTEST database 格式 並 存 於 lib 子 目 錄 中 。 因 為 s382.v 中 內 含 一 些 gates 為 特 別 的 cells,而 這 些 cells 的 相 關 資 訊 定 義 在 35.v, lib.v, udp.v 中 , 所 以 我 們 才 需 要 加上 這 個 選 項 。< 指 令 2> expin s3823. ATPG:< 指 令 > asicgen s382 –non_scan –max_frame 1024-non_scan 表 示 電 路 未 加 scan。 由 於 s382 為 sequential 電 路 , 所 以 程 式會 以 sequential ATPG algorithm 來 產 生 patterns。-max-frame 1024 則 是 設定 對 於 每 個 fault 所 能 使 用 的 最 大 time frame 數 目 為 1024 個 , 預 設 值 為256。要 看 指 令 相 關 說 明 , 請 打 :asicgen –help3

執 行 結 果 > 產 生 s382.rpt、s382.tp、s382.udt、s382.hdt… 等 檔 案觀 察 s382.rpt 的 內 容 :.....This circuit has 1371 test patterns and contains 422 faults of which.....atpg pessimistic fault coverage = HD/(Total-IG) = 88.3886 %.atpg pessimistic test coverage = HD/(Total-UT) = 90.5340 %.atpg pessimistic test efficiency = (HD+UT)/Total = 90.7583 %.atpg optimistic fault coverage = (HD+PT)/(Total-IG) = 93.8389 %.atpg optimistic test coverage = (HD+PT)/(Total-UT-PU) = 96.1165 %.atpg optimistic test efficiency = (Total-Abort)/Total = 96.2085 %.This circuit has 1371 test patterns and contains 706 UNCOLLAPSED faults of which.....atpg pessimistic fault coverage = HD/(Total-IG) = 92.0680 %.atpg pessimistic test coverage = HD/(Total-UT) = 93.6599 %.atpg pessimistic test efficiency = (HD+UT)/Total = 93.7677 %.atpg optimistic fault coverage = (HD+PT)/(Total-IG) = 95.8923 %.atpg optimistic test coverage = (HD+PT)/(Total-UT-PU) = 97.5504 %.atpg optimistic test efficiency = (Total-Abort)/Total = 97.5921 %.4. 產 生 Verilog testfixture file< 指 令 > tpout s382 –vlog-vlog 表 示 會 輸 出 Verilog 格 式 的 檔 案 ─s382.drv.v要 用 該 Verilog 測 試 檔 來 驗 証 test patterns 之 前 , 請 確 認 電 路 的 timing 資 訊 ( 可用 Synopsys 的 Design Analyzer 萃 取 出 .sdf 檔 , 本 練 習 已 提 供 s382.sdf 檔 案 )已 經 加 入 在 s382.drv.v 之 中 。請 把 前 述 指 令 改 為 :tpout s382 –vlog –sdf s382.sdf如 果 要 用 該 Verilog 測 試 檔 來 驗 証 產 生 的 test patterns 是 否 能 真 正 work, 請 下指 令 ( 註 1):vs35 s382.drv.v s382.v如 果 看 到 以 下 畫 面 即 表 示 ATPG 沒 有 問 題 :*** Test vectors simulated : 1761*** Number of vector mismatch : 0註 1: 由 於 tool 以 及 lib 檔 案 版 本 的 問 題 , 此 步 驟 在 執 行 時 可 能 會 產 生 error,所 以 這 個 步 驟 可 以 跳 過 。4

• 自 我 練 習 :1. 以 tool 產 生 分 別 可 以 測 到 c17 電 路 中 下 列 faults 的 patterns。a. U2/out stuck-at 0b. x16gat stuck-at 1c. x19gat stuck-at fault( 包 括 0 與 1)p.s. 指 令 為 :asicgen c17 –non_scan –flt test.flt請 編 輯 test.flt 檔 案 指 定 特 定 的 faults, 格 式 參 考 練 習 一 裡 的 test.flt。以 c 為 例 ,test.flt 的 內 容 為 :/0 /1 x19gat如 此 即 可-> 請 附 上 各 小 題 之 .flt, .tp 檔2. 以 ISCAS85 c499.v 為 例 做 ATPG, 觀 看 需 多 少 patterns 及 fault coverage 為 多 少 。-> 請 附 上 .rpt 檔 相 關 部 份3. 設 計 一 個 combinational circuit, 這 個 電 路 要 至 少 要 包 含 一 個 undetectable fault. 使用 本 練 習 所 介 紹 的 方 法 對 這 個 電 路 做 ATPG.-> 請 附 上 電 路 檔 (in Verilog format) 及 ATPG 產 生 的 .rpt 檔 相 關 部 份4. 以 ISCAS89 電 路 中 s27 電 路 為 對 象 練 習 ATPG, 查 看 所 需 patterns 數 目 及 <strong>Fault</strong>Coverage 為 多 少 。( 請 下 指 令 :asicgen s27 –non_scan –max_frame 1024 ; 不用 做 Verilog <strong>Simulation</strong>)-> 請 附 上 .rpt 檔 相 關 部 份5