Digital Receiver Handbook: Basics of Software Radio

Digital Receiver Handbook: Basics of Software Radio

Digital Receiver Handbook: Basics of Software Radio

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

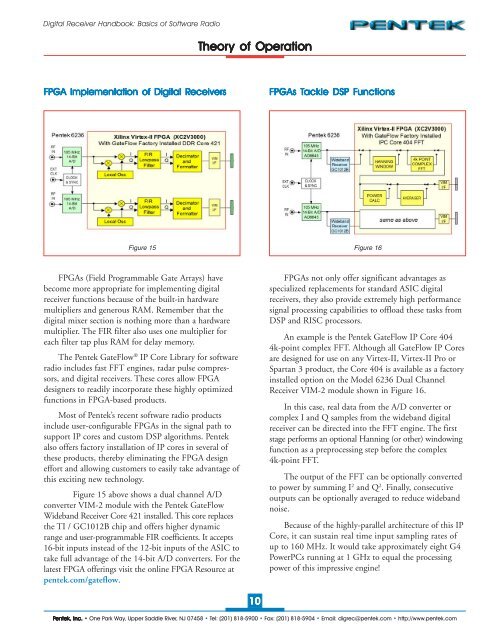

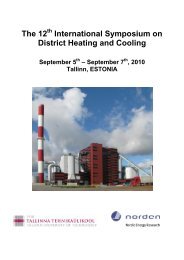

<strong>Digital</strong> <strong>Receiver</strong> <strong>Handbook</strong>: <strong>Basics</strong> <strong>of</strong> S<strong>of</strong>tware <strong>Radio</strong>Theory <strong>of</strong> OperationFPGA Implementation <strong>of</strong> <strong>Digital</strong> <strong>Receiver</strong>sFPGAs Tackle DSP FunctionsFigure 15Figure 16FPGAs (Field Programmable Gate Arrays) havebecome more appropriate for implementing digitalreceiver functions because <strong>of</strong> the built-in hardwaremultipliers and generous RAM. Remember that thedigital mixer section is nothing more than a hardwaremultiplier. The FIR filter also uses one multiplier foreach filter tap plus RAM for delay memory.The Pentek GateFlow ® IP Core Library for s<strong>of</strong>twareradio includes fast FFT engines, radar pulse compressors,and digital receivers. These cores allow FPGAdesigners to readily incorporate these highly optimizedfunctions in FPGA-based products.Most <strong>of</strong> Pentek’s recent s<strong>of</strong>tware radio productsinclude user-configurable FPGAs in the signal path tosupport IP cores and custom DSP algorithms. Pentekalso <strong>of</strong>fers factory installation <strong>of</strong> IP cores in several <strong>of</strong>these products, thereby eliminating the FPGA designeffort and allowing customers to easily take advantage <strong>of</strong>this exciting new technology.Figure 15 above shows a dual channel A/Dconverter VIM-2 module with the Pentek GateFlowWideband <strong>Receiver</strong> Core 421 installed. This core replacesthe TI / GC1012B chip and <strong>of</strong>fers higher dynamicrange and user-programmable FIR coefficients. It accepts16-bit inputs instead <strong>of</strong> the 12-bit inputs <strong>of</strong> the ASIC totake full advantage <strong>of</strong> the 14-bit A/D converters. For thelatest FPGA <strong>of</strong>ferings visit the online FPGA Resource atpentek.com/gateflow.FPGAs not only <strong>of</strong>fer significant advantages asspecialized replacements for standard ASIC digitalreceivers, they also provide extremely high performancesignal processing capabilities to <strong>of</strong>fload these tasks fromDSP and RISC processors.An example is the Pentek GateFlow IP Core 4044k-point complex FFT. Although all GateFlow IP Coresare designed for use on any Virtex-II, Virtex-II Pro orSpartan 3 product, the Core 404 is available as a factoryinstalled option on the Model 6236 Dual Channel<strong>Receiver</strong> VIM-2 module shown in Figure 16.In this case, real data from the A/D converter orcomplex I and Q samples from the wideband digitalreceiver can be directed into the FFT engine. The firststage performs an optional Hanning (or other) windowingfunction as a preprocessing step before the complex4k-point FFT.The output <strong>of</strong> the FFT can be optionally convertedto power by summing I 2 and Q 2 . Finally, consecutiveoutputs can be optionally averaged to reduce widebandnoise.Because <strong>of</strong> the highly-parallel architecture <strong>of</strong> this IPCore, it can sustain real time input sampling rates <strong>of</strong>up to 160 MHz. It would take approximately eight G4PowerPCs running at 1 GHz to equal the processingpower <strong>of</strong> this impressive engine!10Pentek, Inc. • One Park Way, Upper Saddle River, NJ 07458 • Tel: (201) 818-5900 • Fax: (201) 818-5904 • Email: digrec@pentek.com • http://www.pentek.com