Spec-based verification: A new method for functional ... - Cadence

Spec-based verification: A new method for functional ... - Cadence

Spec-based verification: A new method for functional ... - Cadence

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

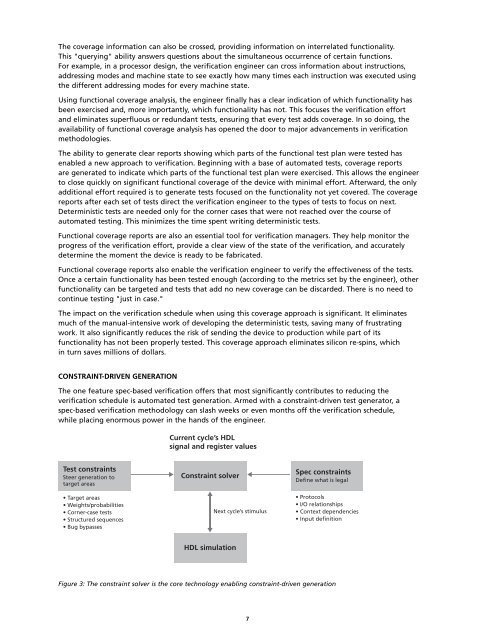

The coverage in<strong>for</strong>mation can also be crossed, providing in<strong>for</strong>mation on interrelated <strong>functional</strong>ity.This "querying" ability answers questions about the simultaneous occurrence of certain functions.For example, in a processor design, the <strong>verification</strong> engineer can cross in<strong>for</strong>mation about instructions,addressing modes and machine state to see exactly how many times each instruction was executed usingthe different addressing modes <strong>for</strong> every machine state.Using <strong>functional</strong> coverage analysis, the engineer finally has a clear indication of which <strong>functional</strong>ity hasbeen exercised and, more importantly, which <strong>functional</strong>ity has not. This focuses the <strong>verification</strong> ef<strong>for</strong>tand eliminates superfluous or redundant tests, ensuring that every test adds coverage. In so doing, theavailability of <strong>functional</strong> coverage analysis has opened the door to major advancements in <strong>verification</strong><strong>method</strong>ologies.The ability to generate clear reports showing which parts of the <strong>functional</strong> test plan were tested hasenabled a <strong>new</strong> approach to <strong>verification</strong>. Beginning with a base of automated tests, coverage reportsare generated to indicate which parts of the <strong>functional</strong> test plan were exercised. This allows the engineerto close quickly on significant <strong>functional</strong> coverage of the device with minimal ef<strong>for</strong>t. Afterward, the onlyadditional ef<strong>for</strong>t required is to generate tests focused on the <strong>functional</strong>ity not yet covered. The coveragereports after each set of tests direct the <strong>verification</strong> engineer to the types of tests to focus on next.Deterministic tests are needed only <strong>for</strong> the corner cases that were not reached over the course ofautomated testing. This minimizes the time spent writing deterministic tests.Functional coverage reports are also an essential tool <strong>for</strong> <strong>verification</strong> managers. They help monitor theprogress of the <strong>verification</strong> ef<strong>for</strong>t, provide a clear view of the state of the <strong>verification</strong>, and accuratelydetermine the moment the device is ready to be fabricated.Functional coverage reports also enable the <strong>verification</strong> engineer to verify the effectiveness of the tests.Once a certain <strong>functional</strong>ity has been tested enough (according to the metrics set by the engineer), other<strong>functional</strong>ity can be targeted and tests that add no <strong>new</strong> coverage can be discarded. There is no need tocontinue testing "just in case."The impact on the <strong>verification</strong> schedule when using this coverage approach is significant. It eliminatesmuch of the manual-intensive work of developing the deterministic tests, saving many of frustratingwork. It also significantly reduces the risk of sending the device to production while part of its<strong>functional</strong>ity has not been properly tested. This coverage approach eliminates silicon re-spins, whichin turn saves millions of dollars.CONSTRAINT-DRIVEN GENERATIONThe one feature spec-<strong>based</strong> <strong>verification</strong> offers that most significantly contributes to reducing the<strong>verification</strong> schedule is automated test generation. Armed with a constraint-driven test generator, aspec-<strong>based</strong> <strong>verification</strong> <strong>method</strong>ology can slash weeks or even months off the <strong>verification</strong> schedule,while placing enormous power in the hands of the engineer.Current cycle’s HDLsignal and register valuesTest constraintsSteer generation totarget areas• Target areas• Weights/probabilities• Corner-case tests• Structured sequences• Bug bypassesConstraint solverNext cycle’s stimulus<strong>Spec</strong> constraintsDefine what is legal• Protocols• I/O relationships• Context dependencies• Input definitionHDL simulationFigure 3: The constraint solver is the core technology enabling constraint-driven generation7