The PowerPC 604 RISC Microprocessor - eisber.net

The PowerPC 604 RISC Microprocessor - eisber.net

The PowerPC 604 RISC Microprocessor - eisber.net

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

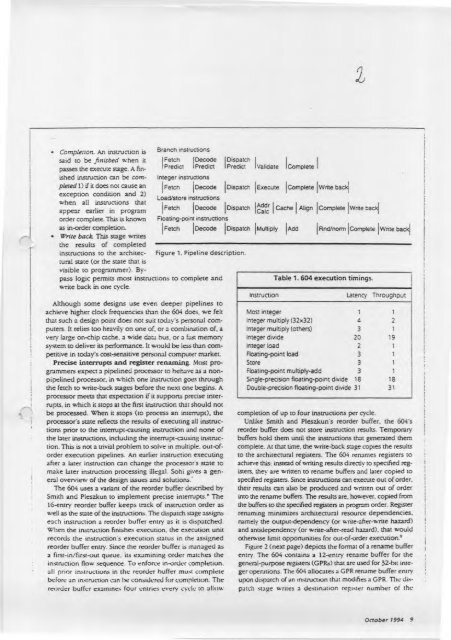

Branch instructionsI FetchPredict'DecodeI PredictInteger instructionsFetchLoad/store instructionsDispatchPredictI Validate I Complete1 l Decode !Dispatch I Execute Complete 'Write backFetch I Decode DispatchFloating-point instructionsFetchDecode IDispatch !Multiply !AddFigure 1. Pipeline description.• Completion. An instruction issaid to be fimshed when itpasses the execute stage. A finishedinstruction can be completed1) if it does not cause anexception condition and 2)when all instructions thatappear earlier in programorder complete. This is knownas in-order completion.• Write back This stage writesthe results of completedinstructions to the architecturalstate (or the state that isvisible to programmer). Bypasslogic permits most instructions to complete andwrite back in one cycle.Although some designs use even deeper pipelines toachieve higher clock frequencies than the <strong>604</strong> does, we feltthat such a design point does not suit today's personal computers.It relies too heavily on one of, or a combination of, avery large on-chip cache, a wide data bus, or a fast memorysystem to deliver its performance. It would be less than competitivein today's cost-sensitive person -al computer market.Precise interrupts and register renaming. Most programmersexpect a pipelines) processor to behave as a nonpipeline('processor, in which one instruction goes throughthe fetch to write-back stages before the next one begins. Aprocessor meets that expectation if it supports precise interrupts,in which it stops at the first instruction that should notbe processed. When it stops (to process an interrupt), theprocessor's state reflects the results of executing all instructionsprior to the interrupt-causing instruction and none ofthe later instructions, including the interrupt-causing instruction.This is not a trivial problem to solve in multiple. out-oforderexecution pipelines. An earlier instruction executingafter a later instruction can change the processor's state tomake Later instruction processing illegal. Sohi gives a generaloverview of the design issues and solutions.<strong>The</strong> <strong>604</strong> uses a variant of the reorder buffer described bySmith and Pleszkun to implement precise interrupts." <strong>The</strong>16-entry reorder buffer keeps track of instruction order aswell as the state of the instructions. <strong>The</strong> dispatch stage assignseach instruction a reorder buffer entry as it is dispatched.When the instruction finishes execution, the execution unitrecords the instructions execution status in the assignedreorder buffer entry. Since the reorder buffer is managed asa first-in/first-out queue. its examining order matches theinstruction flow sequence. To enforce in-order completion.all prior instructions in the reorder buffer must completebefore an instruction can be considered for completion. <strong>The</strong>reorder butler examines four entries every cycle to allowAddr I Cache Align CompleteICalcI I Write back'Rndinorrn CompleteI I Write backInstructionTable 1. <strong>604</strong> execution timings.Latency ThroughputMost integer 1 1integer multiply (32x32) 4 2Integer multiply (others) 1Integer divide 20 19Integer load 2 1Floating-point load 3 1Store 3 1Floating-point multiply-add 3 1Single-precision floating-point divide 18 18Double -precision floating -point divide 31 31completion of up to four instructions per cycle.Unlike Smith and Pleszkun's reorder buffer, the <strong>604</strong>'sreorder buffer does not store instruction results. Temporarybuffers hold them until the instructions that generated themcomplete. At that time, the write-back stage copies the resultsto the architectural registers. <strong>The</strong> <strong>604</strong> renames registers toachieve this: instead of writing results directly to specified registers,they are wntten to rename buffers and later copied tospecified registers. Since instructions can execute out of order,their results can also be produced and written out of orderinto the rename buffers. <strong>The</strong> results are, however. copied fromthe buffers to the specified registers in program order. Registerrenaming minimizes architectural resource dependencies,namely the output-dependency (or write-after-write hazard)and anticlepenciency (or write-after-read hazard), that wouldotherwise limit opportunities for out-of-order execution.'Figure 2 (next page) depicts the format of a rename bufferentry <strong>The</strong> <strong>604</strong> contains a 12-entry rename buffer for thegeneral-purpose registers (GPRs) that are used for 32-bit integeroperations. <strong>The</strong> <strong>604</strong> allocates a GPR rename buffer entryupon dispatch of an instruction that modifies a GPR <strong>The</strong> dispatchstage writes a destination register number of theOctober 1994 9