The PowerPC 604 RISC Microprocessor - eisber.net

The PowerPC 604 RISC Microprocessor - eisber.net

The PowerPC 604 RISC Microprocessor - eisber.net

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

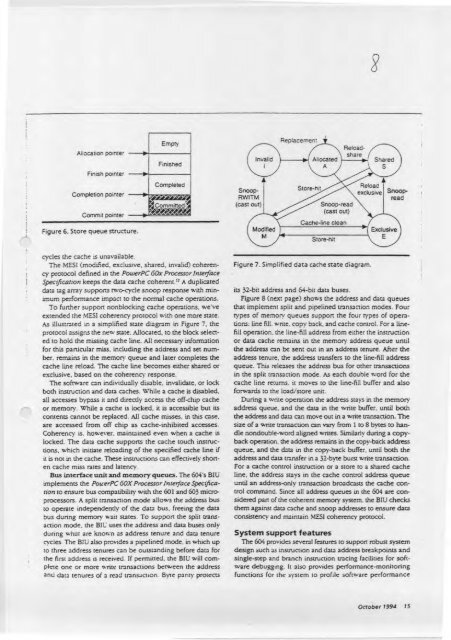

Allocation pointerFinish pointerCompletion pointerCommit pointerFigure 6. Store queue structure.EmptyFinishedCompletedleste,4 Committed..160-40-inWSnoop-RWITM(cast out)InvalidModifiedMReplacementReloadshareAllocated -*-AStore-hitSnoop-read(cast out)Cache-line cleanStore-hitReloadexclusiveSharedSASnoopread(► . Exclusive..cycles the cache is unavailable.<strong>The</strong> MESI (modified, exclusive, shared, invalid) coherencyprotocol defined in the <strong>PowerPC</strong> 60x Processor InterfaceSpecification keeps the data cache coherent.' 2 A duplicateddata tag array supports two-cycle snoop response with minimumperformance impact to the normal cache operations.To further support nonblocking cache operations, we'veextended the MESI coherency protocol with one more state.As illustrated in a simplified state diagram in Figure 7, theprotocol assigns the new state. Allocated, to the block selectedto hold the missing cache line. All necessary informationfor this particular miss. including the address and set number.remains in the memory queue and later completes thecache line reload. <strong>The</strong> cache line becomes either shared orexclusive, based on the coherency response.Tne software can individually disable, invalidate, or lockboth instruction and data caches. While a cache is disabled,all accesses bypass it and directly access the off-chip cacheor memory. While a cache is locked, it is accessible but itscontents cannot be replaced. All cache misses. in this case,are accessed from off chip as cache-inhibited accesses.Coherency is. however_ maintained even when a cache islocked. <strong>The</strong> data cache supports the cache couch instructions,which initiate reloading of the specified cache line ifit is not in the cache. <strong>The</strong>se instructions can effectively shortencache miss races and latencyBus interface unit and memory queues_ <strong>The</strong> <strong>604</strong>'s BIUimplements the <strong>PowerPC</strong> 60X Pnxessor Interface Speczfica-[ion to ensure bus compatibility with the 601 and 603 microprocessors.A split transaction mode allows the address busto operate independently of the data bus, freeing the databus during memory wait states. To support the split transactionmode, the BIL.: uses the address and data buses onlyduring what are known as address tenure and data tenurec-ycies. <strong>The</strong> 81li also provides a pipelined mode, in which upto three address tenures can be outstanding before data forthe first address is received. If permitted. the BIU will completeone or more write transactions berween the addressand data tenures of a read transaction. Byte parity protectsFigure 7. Simplified data cache state diagram.its 32-bit address and 64-bit data buses.Figure 8 (next page) shows the address and data queuesthat implement split and pipelined transaction modes. Fourtypes of memory queues support the four types of operations:line fill. write. copy back. and cache control. For a linefiiloperation. the line-fill address from either the instructionor data cache remains in the memory address queue untilthe address can be sent out in an address tenure. After theaddress tenure, the address transfers to the addressqueue. This releases the address bus for other transactionsin the split transaction mode. As each double word for thecache line retums. it moves to the line-fill buffer and alsoforwards to the load/store unit.During a write operation the address stays in the memoryaddress queue. and the data in the write buffer. until boththe address and data can move out in a write transaction. <strong>The</strong>size of a write transaction can vary from 1 to 8 bytes to handlenondouble-word aligned writes. Similarly during a copybackoperation. the address remains in the copy-back addressqueue, and the data in the copy-back buffer, until both theaddress and data transfer in a 32-byte burst write transaction.For a cache control instruction or a store to a shared cacheline, the address stays in the cache control address queueuntil an address-only transaction broadcasts the cache controlcommand. Since all address queues in the <strong>604</strong> are consideredpart of the coherent memory system. the BIli checksthem against data cache and snoop addresses to ensure dataconsistency and maintain MESI coherency protocol.System support features<strong>The</strong> <strong>604</strong> provides several features to support robust systemdesign such as instruction and data address breakpoints andsingle-step and branch instruction tracing facilities for softwaredebugging. It also provides performance-monitoringfunctions for the system to profile software performanceOctober 1994 15