Tachyon

Data Sheet (.pdf) - Brion Technologies, Inc.

Data Sheet (.pdf) - Brion Technologies, Inc.

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

............................................<br />

brion.com<br />

<strong>Tachyon</strong> <br />

LAD<br />

A COMPREHENSIVE SOLUTION FOR HIGH FIDELITY<br />

LITHOGRAPHY MODELING DURING THE INTEGRATED<br />

CIRCUIT (IC) DESIGN IMPLEMENTATION PHASE<br />

......................................................<br />

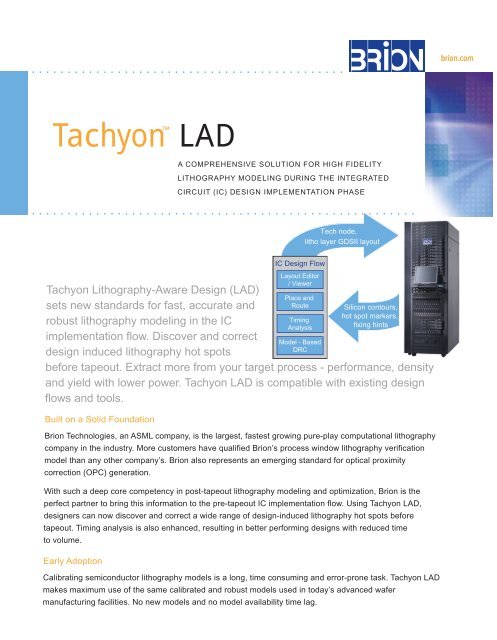

Tech node,<br />

litho layer GDSII layout<br />

<strong>Tachyon</strong> Lithography-Aware Design (LAD)<br />

sets new standards for fast, accurate and<br />

robust lithography modeling in the IC<br />

implementation flow. Discover and correct<br />

design induced lithography hot spots<br />

before tapeout. Extract more from your target process - performance, density<br />

and yield with lower power. <strong>Tachyon</strong> LAD is compatible with existing design<br />

flows and tools.<br />

Built on a Solid Foundation<br />

Brion Technologies, an ASML company, is the largest, fastest growing pure-play computational lithography<br />

company in the industry. More customers have qualified Brion’s process window lithography verification<br />

model than any other company’s. Brion also represents an emerging standard for optical proximity<br />

correction (OPC) generation.<br />

With such a deep core competency in post-tapeout lithography modeling and optimization, Brion is the<br />

perfect partner to bring this information to the pre-tapeout IC implementation flow. Using <strong>Tachyon</strong> LAD,<br />

designers can now discover and correct a wide range of design-induced lithography hot spots before<br />

tapeout. Timing analysis is also enhanced, resulting in better performing designs with reduced time<br />

to volume.<br />

Early Adoption<br />

IC Design Flow<br />

Layout Editor<br />

/ Viewer<br />

Place and<br />

Route<br />

Timing<br />

Analysis<br />

Model - Based<br />

DRC<br />

Calibrating semiconductor lithography models is a long, time consuming and error-prone task. <strong>Tachyon</strong> LAD<br />

makes maximum use of the same calibrated and robust models used in today’s advanced wafer<br />

manufacturing facilities. No new models and no model availability time lag.<br />

Silicon contours,<br />

hot spot markers,<br />

fixing hints

<strong>Tachyon</strong> LAD<br />

LAD Product Features<br />

Accurate Full Process-Window Modeling<br />

■<br />

The same fully calibrated models<br />

are used in OPC generation and<br />

OPC verification<br />

■ Fast modeling for the entire process -<br />

mask, optics, resist and etch<br />

■<br />

■<br />

Mask and wafer process<br />

variability analysis<br />

Dense image-based computation<br />

Inputs to Third Party EDA Tools<br />

■ Cross-process window contours<br />

with and without mask CD errors<br />

■<br />

Lithography manufacturability hot<br />

spot check reports (contours and<br />

hot spot markers)<br />

■ Hot spot resolutions<br />

Speed and Performance<br />

■<br />

■<br />

■<br />

■<br />

■<br />

Fully integrated hardware<br />

accelerated platform for full<br />

chip applications<br />

Fast, predictable turnaround time<br />

Linearly scales with chip area<br />

Linearly scales with leaf node<br />

additions<br />

Insensitive to design hierarchy,<br />

pattern complexity and file size<br />

Applications Include<br />

■<br />

■<br />

■<br />

■<br />

■<br />

Library and memory<br />

cell optimization<br />

Full chip place and<br />

route optimization<br />

Timing analysis<br />

Model based design rule check<br />

(DRC) sign-off<br />

Real-time contour review for<br />

custom layout and RET review<br />

<strong>Tachyon</strong> LAD is architected to interface easily to existing IC<br />

implementation and verification tools. Users will be able to upgrade their<br />

existing flows to support critical manufacturing information. <strong>Tachyon</strong> LAD<br />

communicates this information in a form that is familiar to designers –<br />

GDSII compatible data with hot spot markers. While the analysis engines<br />

inside <strong>Tachyon</strong> LAD contain detailed lithography information, that<br />

complexity is hidden from the user.<br />

No new models to verify, no new tools to adopt, no new technology to<br />

learn, just manufacturable, robust designs.<br />

Unified Models, Simplified Analysis<br />

.......................<br />

Computational Lithography Enabled Design & Manufacturing<br />

Library<br />

Custom<br />

Layout<br />

P&R<br />

Design Intent<br />

Extraction<br />

Power<br />

Timing<br />

Process Information<br />

DRC<br />

LVS<br />

CL<br />

Model<br />

Process window<br />

Process window<br />

RET<br />

OPC<br />

LMC<br />

Mask<br />

Data<br />

Prep<br />

MEEF defects<br />

Hot spots<br />

Statistics<br />

Thru-PW defects<br />

Full chip contour Thru PW defects<br />

Hot spots<br />

Process Information<br />

Mask<br />

Writer<br />

Mask<br />

Inspect<br />

Mask<br />

Metrology<br />

Design Intent<br />

The same process model used<br />

in the entire design to manufacturing flow<br />

Wafer<br />

Scanner<br />

Wafer<br />

Metrology<br />

With <strong>Tachyon</strong> LAD, there is now one accurate and production proven<br />

model used throughout the entire design and manufacturing flow. Clear<br />

manufacturability ownership is established. Lithography process models<br />

and resolution enhancement techniques (RET) are owned by the Fab;<br />

chip performance and robustness are owned by the designer.<br />

<strong>Tachyon</strong> LAD is being integrated with third party EDA tools and design<br />

flows through a well defined client-server interface architecture. Ask your<br />

EDA vendor about <strong>Tachyon</strong> LAD support today.<br />

Brion Technologies, Inc.<br />

Phone: +1 (408) 653-1500<br />

Email: info@brion.com<br />

brion.com<br />

© 2007 Brion Technologies, Inc. All rights reserved.