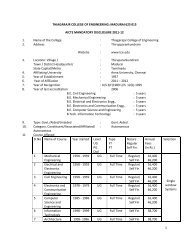

THIAGARAJAR COLLEGE OF ENGINEERING: MADURAI – 625 015 ...

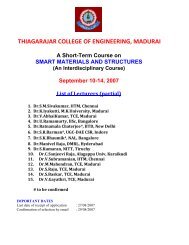

THIAGARAJAR COLLEGE OF ENGINEERING: MADURAI – 625 015 ...

THIAGARAJAR COLLEGE OF ENGINEERING: MADURAI – 625 015 ...

- TAGS

- thiagarajar

- college

- madurai

- tce.edu

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

System <strong>–</strong> Properties of Systems <strong>–</strong> Difference Equations <strong>–</strong> Frequency Response of Linear Discrete Time<br />

System. (10 Periods)<br />

Unit - V: Discrete Fourier Transform (DFT): Introduction <strong>–</strong> Comparison of DFT and Fourier Series <strong>–</strong><br />

Properties of DFT - Derivation of FFT <strong>–</strong> Application of FFT. (10 Periods)<br />

Text Book:<br />

1. Rodger E. Ziemer, William H. Tranter and D. Ronald Fannain “Signals & Systems Continuous<br />

and Discrete”, Pearson Education 2002.<br />

Reference Books:<br />

1. M J Roberts, “Signals and Systems <strong>–</strong> Analysis using Transform Methods and MATLAB”,<br />

TataMcGraw-Hill, 2003.<br />

2. Simon Haykin, Barry Van Veen, “ Signals and Systems”, Wiley, 2 nd Edition, 2002<br />

3. Alan V Oppenheim and Alan S. Willsky, “Signals & Systems”, Second Edition, Prentice Hall<br />

India, 1997.<br />

D36 DIGITAL CIRCUITS AND TECHNIQUES<br />

Unit <strong>–</strong> I: Introduction TO Gates and Combinational Circuits: Basic digital circuits AND-OR-NAND-<br />

NOR-EX-OR <strong>–</strong> EX <strong>–</strong> NOR operations <strong>–</strong> universal building block construction using logic gates <strong>–</strong> Boolean<br />

Algebra <strong>–</strong> Simplification of Boolean functions <strong>–</strong> special forms of Boolean functions <strong>–</strong> min term (SOP)max<br />

term (POS)-completely and incompletely specified switching function -. K Map representation of<br />

Logic functions <strong>–</strong> Simplification of logic functions using K Map <strong>–</strong> Don’t care conditions <strong>–</strong> Five variable K<br />

Maps- Quine McClusky Method - Half and Full Adders <strong>–</strong> Half and Full Subtractors<br />

(10 Periods)<br />

Unit <strong>–</strong> II: Sequential Circuits: Basic one bit memory cell- Flip Flop (RS, JK.D, T & Master slave JK) <strong>–</strong><br />

Excitation Table <strong>–</strong> clocked Flip Flop design <strong>–</strong> Edge triggered flip flops <strong>–</strong> NAND, NOR Gate Latch - Clock<br />

Signals and Clocked Flip-Flops: SRFF, JKFF, DFF - D Latch - Asynchronous Inputs- IEEE/ANSI<br />

Symbols- Flip-Flop Timing Considerations <strong>–</strong> Flip Flop Applications: Synchronization <strong>–</strong> Detecting<br />

Sequence <strong>–</strong> Serial Parallel transfer <strong>–</strong> Frequency Division and Counting <strong>–</strong> Schmitt Trigger <strong>–</strong> One Shot.<br />

(10<br />

Periods)<br />

Unit - III: Analysis of Synchronous Sequential Networks: Counter Design using D, SR and JKFF <strong>–</strong><br />

Structure Operation <strong>–</strong> Excitation and output Expressions <strong>–</strong> Transition Equation <strong>–</strong> Transition Table <strong>–</strong><br />

Excitation Table <strong>–</strong> State Tables and State Diagram <strong>–</strong> Mealy and Moore Model <strong>–</strong> Sequence Recognizer <strong>–</strong><br />

Algorithmic State Machine: ASM Chart for Sequential Recognizer <strong>–</strong> State Assignments <strong>–</strong> ASM Tables <strong>–</strong><br />

ASM Realization using Gates, MUX and PROM. Asynchronous Sequential Networks: Static and Dynamic<br />

Hazards <strong>–</strong> Detection and Elimination <strong>–</strong> Hazard Free Combinational Logic Networks <strong>–</strong> Essential hazards.<br />

(10 Periods)<br />

Unit <strong>–</strong>IV: Registers & Counters: Asynchronous (Ripple) Counters- Counters with MOD Numbers 2 ^N.<br />

IC Asynchronous Counters - Asynchronous Down Counter- Propagation Delay in Ripple Counters-<br />

Synchronous (Parallel) Counters- Synchronous Down and Up/Down Counters. Presettable Counters- The<br />

74LS193 - Decoding a Counter - Decoding Glitches - Cascading BCD Counters- Synchronous Counter<br />

Design.- State Machines.--Integrated-Circuit Registers - Parallel In/Parallel Out, Serial In/Serial Out,<br />

Parallel In/Serial Out and Serial In/Parallel Out Registers<br />

(10 Periods)