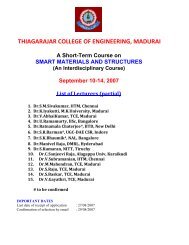

THIAGARAJAR COLLEGE OF ENGINEERING: MADURAI – 625 015 ...

THIAGARAJAR COLLEGE OF ENGINEERING: MADURAI – 625 015 ...

THIAGARAJAR COLLEGE OF ENGINEERING: MADURAI – 625 015 ...

- TAGS

- thiagarajar

- college

- madurai

- tce.edu

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

1. Antoniou, A. “Digital filters - Analysis, Design and Applications”, McGraw-Hill<br />

International Editions, Electrical Engineering series, 2nd. ed., 1993,<br />

2. Sanjit K. Mitra, “Digital Signal Processing <strong>–</strong> A Computer based Approach”, Tata McGraw<br />

Hill, 2001.<br />

3. Vinay K Ingle and John G Proakis, “ Digital Signal Processing using MATLAB”, Brroks<br />

Cole, 1999<br />

4. John G Proakis, “Digital Signal Processing: Principles, Algorithms and Applications”,<br />

Pearson Education, 1995.<br />

5. Brian D O Anderson and John B Moore, “ Optimal Filtering”, Dover Publications, 2005<br />

D46 DIGITAL LOGIC WITH VHDL DESIGN<br />

UNIT I: Design Concepts : Digital Hardware - Standard Chips Programmable Logic Devices <strong>–</strong> Custom <strong>–</strong><br />

Designed Chips <strong>–</strong> Design Process <strong>–</strong> Design of Digital Hardware <strong>–</strong> Basic Design Loop <strong>–</strong> Design of a Digital<br />

hardware Unit <strong>–</strong> Introduction to CAD tools <strong>–</strong> Design - Entry Synthesis <strong>–</strong> Functional Simulation <strong>–</strong><br />

Introduction to VHDL <strong>–</strong> Representation of Digital Signals in VHDL <strong>–</strong> Writing Simple VHDL Code <strong>–</strong> How<br />

Not to Write VHDL Code. (10 Periods)<br />

UNIT II: Optimized Implementation of Logic Functions : Karnaugh Map <strong>–</strong> Strategy for Minimization <strong>–</strong><br />

Minimization of Product <strong>–</strong> of - Sums Forms <strong>–</strong> Incompletely Specified Functions <strong>–</strong> Multiple <strong>–</strong> output<br />

Circuits <strong>–</strong> NAND and NOR Logic Networks <strong>–</strong> Multilevel Synthesis <strong>–</strong> Analysis of Multilevel Circuits <strong>–</strong><br />

Cubical Representation <strong>–</strong> Minimization using Cubical Representation <strong>–</strong> Practical Considerations <strong>–</strong> CAD<br />

Tools. (10 Periods)<br />

UNIT III: Combinational Circuit Building Blocks : Multiplexers <strong>–</strong> Decoders <strong>–</strong> Encoders <strong>–</strong> Code<br />

Converters <strong>–</strong> Arithmetic Comparison Circuits <strong>–</strong> VHDL for Combinational Circuits-Assignment statements-<br />

Selected signal assignment-Conditional signal assignment-Generate statements-Process statement-Case<br />

statement. (10 Periods)<br />

UNIT IV: Flip-Flops, Registers and Counters : Basic Latch <strong>–</strong> Gated SR Latch - Gated SR Latch with<br />

NAND Gates <strong>–</strong> GATED D Latch <strong>–</strong> Master-Slave And Edge <strong>–</strong> Triggered D Flip-Flops <strong>–</strong> T Flip-Flop <strong>–</strong> JK<br />

Flip-Flop <strong>–</strong> Summary Of Terminology- Resisters <strong>–</strong> Counters <strong>–</strong> Using Storage Elements With CAD Tools <strong>–</strong><br />

Using Registers and Counters with CAD Tools <strong>–</strong> Design Examples.<br />

(10 Periods)<br />

UNIT V: Synchronous Sequential Circuits: Basic Design Steps <strong>–</strong> State Assignment Problem <strong>–</strong> Mealy<br />

State Model <strong>–</strong> Design of FSM Using CAD tools VHDL Code for Moore-type FSMs- Synthesis of VHDL<br />

Code <strong>–</strong> Simulating and Testing the Circuit <strong>–</strong> Serial Adder Example <strong>–</strong> State Minimization <strong>–</strong> Counter Design<br />

<strong>–</strong> FSM as an arbiter Circuit <strong>–</strong> ASM Charts. (10 Periods)<br />

Text Book:<br />

1. Stephen Brown and Zvonko Vranesic, “Fundamentals of Digital Logic with VHDL Design” Tata<br />

McGraw Hill edition, 2001.<br />

Reference Books:<br />

1. Navabi, “VHDL Modelling”, McGraw Hill, 1997<br />

2. J.Bhaskar, “VHDL Primer”, Pearson Education, 1999.<br />

D47 ANALOG COMMUNICATION LAB