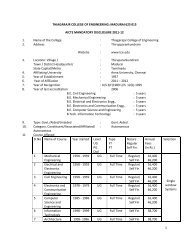

THIAGARAJAR COLLEGE OF ENGINEERING: MADURAI – 625 015 ...

THIAGARAJAR COLLEGE OF ENGINEERING: MADURAI – 625 015 ...

THIAGARAJAR COLLEGE OF ENGINEERING: MADURAI – 625 015 ...

- TAGS

- thiagarajar

- college

- madurai

- tce.edu

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

1. Gred Luthans, “ Organisational Behavior” 5 th Edition<br />

2. Kooniz & O. Dennel, “Principles of Managements” , 8 th edition<br />

3. Chester I.Barnard, “Management (systems view)”<br />

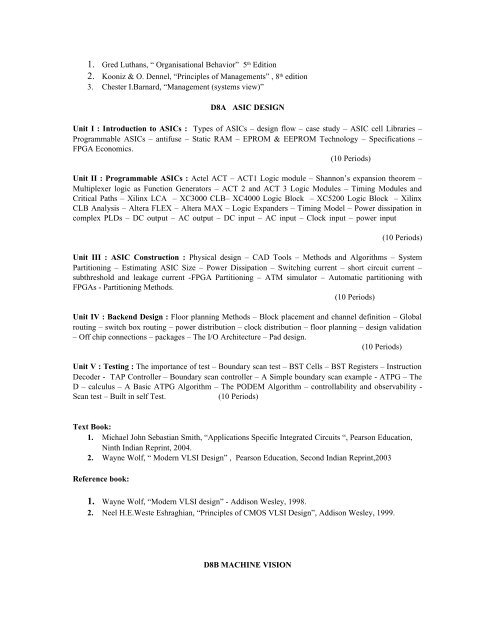

D8A ASIC DESIGN<br />

Unit I : Introduction to ASICs : Types of ASICs <strong>–</strong> design flow <strong>–</strong> case study <strong>–</strong> ASIC cell Libraries <strong>–</strong><br />

Programmable ASICs <strong>–</strong> antifuse <strong>–</strong> Static RAM <strong>–</strong> EPROM & EEPROM Technology <strong>–</strong> Specifications <strong>–</strong><br />

FPGA Economics.<br />

(10 Periods)<br />

Unit II : Programmable ASICs : Actel ACT <strong>–</strong> ACT1 Logic module <strong>–</strong> Shannon’s expansion theorem <strong>–</strong><br />

Multiplexer logic as Function Generators <strong>–</strong> ACT 2 and ACT 3 Logic Modules <strong>–</strong> Timing Modules and<br />

Critical Paths <strong>–</strong> Xilinx LCA <strong>–</strong> XC3000 CLB<strong>–</strong> XC4000 Logic Block <strong>–</strong> XC5200 Logic Block <strong>–</strong> Xilinx<br />

CLB Analysis <strong>–</strong> Altera FLEX <strong>–</strong> Altera MAX <strong>–</strong> Logic Expanders <strong>–</strong> Timing Model <strong>–</strong> Power dissipation in<br />

complex PLDs <strong>–</strong> DC output <strong>–</strong> AC output <strong>–</strong> DC input <strong>–</strong> AC input <strong>–</strong> Clock input <strong>–</strong> power input<br />

(10 Periods)<br />

Unit III : ASIC Construction : Physical design <strong>–</strong> CAD Tools <strong>–</strong> Methods and Algorithms <strong>–</strong> System<br />

Partitioning <strong>–</strong> Estimating ASIC Size <strong>–</strong> Power Dissipation <strong>–</strong> Switching current <strong>–</strong> short circuit current <strong>–</strong><br />

subthreshold and leakage current -FPGA Partitioning <strong>–</strong> ATM simulator <strong>–</strong> Automatic partitioning with<br />

FPGAs - Partitioning Methods.<br />

(10 Periods)<br />

Unit IV : Backend Design : Floor planning Methods <strong>–</strong> Block placement and channel definition <strong>–</strong> Global<br />

routing <strong>–</strong> switch box routing <strong>–</strong> power distribution <strong>–</strong> clock distribution <strong>–</strong> floor planning <strong>–</strong> design validation<br />

<strong>–</strong> Off chip connections <strong>–</strong> packages <strong>–</strong> The I/O Architecture <strong>–</strong> Pad design.<br />

(10 Periods)<br />

Unit V : Testing : The importance of test <strong>–</strong> Boundary scan test <strong>–</strong> BST Cells <strong>–</strong> BST Registers <strong>–</strong> Instruction<br />

Decoder - TAP Controller <strong>–</strong> Boundary scan controller <strong>–</strong> A Simple boundary scan example - ATPG <strong>–</strong> The<br />

D <strong>–</strong> calculus <strong>–</strong> A Basic ATPG Algorithm <strong>–</strong> The PODEM Algorithm <strong>–</strong> controllability and observability -<br />

Scan test <strong>–</strong> Built in self Test. (10 Periods)<br />

Text Book:<br />

1. Michael John Sebastian Smith, “Applications Specific Integrated Circuits “, Pearson Education,<br />

Ninth Indian Reprint, 2004.<br />

2. Wayne Wolf, “ Modern VLSI Design” , Pearson Education, Second Indian Reprint,2003<br />

Reference book:<br />

1. Wayne Wolf, “Modern VLSI design” - Addison Wesley, 1998.<br />

2. Neel H.E.Weste Eshraghian, “Principles of CMOS VLSI Design”, Addison Wesley, 1999.<br />

D8B MACHINE VISION