SPICE Models for SIPMOS Components - Infineon

SPICE Models for SIPMOS Components - Infineon

SPICE Models for SIPMOS Components - Infineon

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

9/97<br />

Power Semiconductor Application Note AN_PSM1e<br />

<strong>SPICE</strong> <strong>Models</strong> <strong>for</strong> <strong>SIPMOS</strong> <strong>Components</strong><br />

Purpose: Clarification of <strong>SIPMOS</strong> - <strong>SPICE</strong> models V1.0<br />

Author: Dr. P. Türkes, Dr. M. März, P. Nance<br />

1) Introduction<br />

Powerful new-generation personal computers with a fast main processor and a math-coprocessor<br />

allow circuit developers to benefit inexpensively from CAD methods, since such computers make it<br />

possible to run easy-to-use network simulation programs.<br />

A problem that arises, especially when simulating power electronics circuits, is that the typical power<br />

electronics components, such as power MOSFETs, diodes and so on, do not figure in the standard<br />

component libraries of simulators. In such cases, the manufacturer of these power components<br />

supplies equivalent circuits (‘subcircuits’) which approach the typical behaviour of the power<br />

components. Inevitably, such a subcircuit is made up of the standard components of the simulators.<br />

So that these models can be used in as many common simulation programs as possible, the<br />

subcircuit must be described in accordance with the original <strong>SPICE</strong> 2G6 version. The reason <strong>for</strong> this<br />

approach is that, whilst compatibility between all available PC <strong>SPICE</strong> versions is only limited,<br />

compatibility with the original version is unrestricted. However, simulations of the operation of the<br />

component in ultimate regions is not possible with this method.<br />

The next section describes the subcircuits which are used <strong>for</strong> the <strong>SIPMOS</strong> power transistors in the<br />

libraries BUZ_L0.LIB and BSS_L0.LIB. The models are suitable to simulate the DC and AC behaviour<br />

in standard circuits and under safe ambient conditions.<br />

A section which describes the model is followed by an overview of the measurement and evaluation<br />

methods <strong>for</strong> establishing the parameters which determine the behaviour of the <strong>SIPMOS</strong> transistor in<br />

the subcircuit.<br />

After this, the output and gate loading characteristics of the component are simulated on the basis of<br />

the measurement circuits used and compared with the actual measurement.<br />

Finally, and by way of example, a user circuit is simulated.<br />

2) Model description<br />

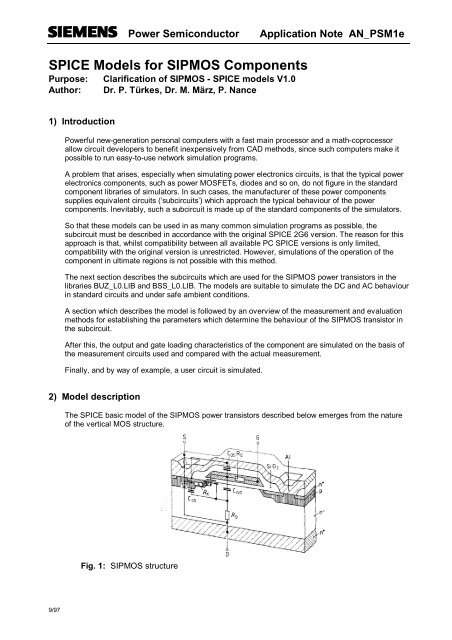

The <strong>SPICE</strong> basic model of the <strong>SIPMOS</strong> power transistors described below emerges from the nature<br />

of the vertical MOS structure.<br />

Fig. 1: <strong>SIPMOS</strong> structure

Power Semiconductor Application Note AN_PSM1e<br />

No detailed description of such a vertical MOS structure is given here; please refer to the relevant<br />

literature.<br />

Network elements that emerge from the technological structure have already been drawn in the crosssection<br />

of the component. For example, the drift distance is designated as resistance Rd.<br />

The <strong>SPICE</strong> subcircuit <strong>for</strong> the <strong>SIPMOS</strong> transistor arising from the component cross-section above is<br />

shown in Fig. 2. The various voltage interdependencies have been taken into account.<br />

n-channel enhancement n-channel depletion<br />

Fig. 2: The <strong>SIPMOS</strong> Level-1 <strong>SPICE</strong> transistor models<br />

(The basic structure of the subcircuit applies both to power and small-signal transistors)<br />

The network consists of equivalent components which describe on the one hand the DC and on the<br />

other the AC and transient behaviour of the transistor. It is important to distinguish between the<br />

following subcomponents:<br />

DC-relevant subcomponents:<br />

a) The inner MOSFET MBUZ describes the characteristic curves of the component and its transfer<br />

characteristic.<br />

b) The source resistance RS is <strong>for</strong> negative feedback to the gate at high currents.<br />

c) The drain resistance, which may be voltage-dependent, is represented as ’depletion mode<br />

MOSFET’ MVRD. The voltage dependence of the drain resistance is caused by modulation of<br />

the conductivity in the drain region as a consequence of a field effect of the drain-source pn<br />

junction. This field effect narrows the current path between the source islands of the MOSFET<br />

when the drain-source voltage is applied; see Figure 1.<br />

The sum of the resistances MBUZ, RS and MVRD gives the ‘on-state resistance’ of the<br />

component.<br />

d) The reverse diode DREV is <strong>for</strong> backward operation of the transistor.<br />

AC-relevant subcomponents<br />

a) The constant gate-source capacitance CGS models the switching time-constants.<br />

b) The voltage-dependent gate-drain capacitance (or Miller capacitance) COX, together with the<br />

diode DGD, describe the modelling of the gate charging process. COX is provided as a con-<br />

2 AN_M1.DOC

Power Semiconductor Application Note AN_PSM1e<br />

stant capacitance to describe the gate-drain capacitance in the off-state and DGD as the<br />

barrier-layer capacitance <strong>for</strong> this in the on-state. Depending on the working point, these two<br />

parts of the gate-drain capacitance are switched to M2 and M3 by the two MOSFETs.<br />

This means that the only purpose of subcomponents M2 and M3 is to act as auxiliary components<br />

to set the working point of the voltage-dependent gate-drain capacitance.<br />

d) The barrier-layer capacitance Cjo and the transfer time-constant TT of the reverse diode DREV<br />

fully model the switching time-constants.<br />

e) The lead inductances LG, LD and LS influence the rates at which the currents rise. In particular,<br />

the source inductance LS causes current feedback to the gate circuit.<br />

f) The auxiliary voltage source VGC sets the capacitance process.<br />

This auxiliary voltage source makes it possible to take account of the influence of technological<br />

steps which reduce the starting voltage of the MOSFET and at the same time shift the<br />

capacitance curves toward higher voltages. This circuit variant is not used in all component<br />

models. Such an auxiliary voltage source is used, <strong>for</strong> instance, in the types known as ’logic<br />

level’ types.<br />

In these, a constant charge, which can be represented according to the displacement law as a<br />

fixed voltage source, is applied to the MOS capacitor.<br />

g) Gate resistance RG<br />

The gate resistance delays the recharging of the MOS capacitor during switching. The timeconstant<br />

resulting from the combination of RG and CGS is the measure <strong>for</strong> the setting of the<br />

resistance RG. The value of RG can only be determined directly with difficulty.<br />

It is there<strong>for</strong>e suggested, as far as use of the model is concerned, that the switching<br />

time-constant should be adapted to the conditions by means of external resistances in<br />

the gate circuit.<br />

The next section explains how to measure and calculate the parameters which describe the<br />

equivalent components.<br />

3) Parameter extraction<br />

a) Parameters from the MOSFET input characteristic I d = I d (U g ) at U ds = const<br />

The input characteristic of the component can be drawn with a characteristic recorder. Data<br />

collection is simplified if a recorder with digital memory and a digital output is used.<br />

The parameters to be extracted depend mainly on the basic model used to describe the<br />

MOSFET current as a function of the applied voltages.<br />

The basic model chosen <strong>for</strong> the inner MOSFET of this <strong>SIPMOS</strong>-<strong>SPICE</strong> description is<br />

introduced in the literature as a ’LEVEL 1’ model and describes the MOSFET transfer function<br />

Id = Id(Ug,Uds) as a function of only two parameters:<br />

i) I d = Kp*((U gs - U t )*U ds - U ds 2 /2) triode region<br />

ii) I d = Kp/2*(U gs - U t ) 2<br />

saturation region<br />

If current negative feedback via a source resistance Rs is to be taken into account, equation ii)<br />

must be modified as follows:<br />

iii) I<br />

d<br />

= Kp/2*(U<br />

g<br />

- U<br />

t<br />

- I<br />

d<br />

*R<br />

s<br />

) 2<br />

Using this equation and a ’least mean square’ fit, the parameters transfer function Kp, starting<br />

voltage Ut of the MOSFET and the value of the source resistance Rs are determined. Taking<br />

the BUZ 12 as an example, this process is represented by comparison of the measurement<br />

curve and the function i) adapted to it (Fig. 3). The corresponding evaluation routine is<br />

programmed with the aid of the mathematical utility program MATHCAD.<br />

3 AN_M1.DOC

√<br />

I d<br />

A<br />

Power Semiconductor Application Note AN_PSM1e<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

3.5 4 4.5 5 5.5 6 6.5 7<br />

Fig. 3: Evaluation of the transfer characteristic<br />

U DS [V]<br />

b) Parameters from the characteristic I d = I d (U g = U cc )<br />

UG = UDS<br />

After evaluation of the transfer characteristic, the parameters Kp, Vt and Rs are known. This<br />

makes it possible to calculate a characteristic Id (Ug,Uds) corresponding to the subcircuit (Fig. 2),<br />

in order to determine the voltage-dependent drain resistance RD. In other words, the voltagedependent<br />

resistance is determined as a current/voltage characteristic from the comparison of the<br />

calculated and the simulated output characteristic.<br />

I d [A]<br />

50<br />

40<br />

30<br />

20<br />

10<br />

0<br />

standard<br />

DMOS model<br />

(<strong>SPICE</strong>)<br />

measured<br />

device<br />

characteristic<br />

UG = const.<br />

0 0.25 0.5 0.75 1 1.25 1.5<br />

U DS [V]<br />

Fig. 4: Comparison of the calculated and the measured output characteristics<br />

at Ug = 20V to determine the drain resistance (Example: BUZ12)<br />

4 AN_M1.DOC

I d [A]<br />

Power Semiconductor Application Note AN_PSM1e<br />

50<br />

40<br />

30<br />

20<br />

10<br />

0<br />

0 0.25 0.5 0.75 1 1.25 1.5<br />

U DS (MVRD) [V]<br />

Fig. 5: Drain resistance characteristic determined from the curves of Fig. 4<br />

Apart from this, voltage dependency of the drain resistance may only be expected with components<br />

having higher blocking voltages. Such behaviour is only weakly present in high-current types. Here<br />

it is sufficient to include a constant resistance in the network instead of the auxiliary transistor<br />

MVRD. This constant drain resistance can be worked out from the known on-state conductivity of<br />

the component, the extracted source resistance and the MOSFET transfer characteristic.<br />

c) Characteristic of the reverse diode<br />

Semi-logarithmic extrapolation of the diode <strong>for</strong>ward current gives the reverse current IS and the<br />

’ideality factor’ N, which characterise the <strong>for</strong>ward characteristic:<br />

iv) I di = IS*(exp(U di /(N*UT)) - 1) where UT is the temperature voltage.<br />

d) Parameters from AC characteristics<br />

Capacitance parameters:<br />

The basis <strong>for</strong> the measurement and thus <strong>for</strong> the evaluation is the subcircuit of the three<br />

capacitances CDS and CGD of the MOS part and CJ of the reverse diode, in a star arrangement.<br />

The measurements are made in configurations familiar from the application notes of the<br />

capacitance bridge manufacturers. The measurement frequency is set to 1 MHz and the drainsource<br />

voltage is varied in the working range at constant gate voltage. The result is a family of<br />

characteristics <strong>for</strong> the voltage-dependent capacitances.<br />

A typical family of measurement curves <strong>for</strong> CGS, CGD and CDS is shown in Figure 6.<br />

5 AN_M1.DOC

Power Semiconductor Application Note AN_PSM1e<br />

10000<br />

C [pF]<br />

1000<br />

100<br />

C DS<br />

C GD<br />

C GS<br />

0 5 10 15 20 25 30<br />

U DS [V]<br />

Fig. 6: Voltage-dependent capacitances CGS, CGD and CDS (BUZ100S)<br />

It is evident even here that CGS is almost independent of the voltage, whereas CDS and<br />

CGD show distinct voltage-dependent behaviour. The value of CGS can be taken directly<br />

from such a measurement.<br />

The two voltage-dependent capacitances CDS and CGD must now be introduced into the<br />

network model as follows:<br />

Taking the <strong>SPICE</strong>-specific description of a barrier layer capacitance in the <strong>SPICE</strong> diode<br />

model as a starting point, it would seem natural to adapt the measured capacitance curves to<br />

the <strong>SPICE</strong> barrier layer model. For the behaviour of CDS, this is easily done by adapting the<br />

function<br />

v) CDS = CDS0 * ( 1 + V<br />

di<br />

/V<br />

j<br />

) m<br />

built into <strong>SPICE</strong> in order to determine the parameters CDS0, Vj, m.<br />

The procedure <strong>for</strong> the gate-drain capacitance is exactly the same. The measured behaviour is<br />

adapted to the function v) and the corresponding parameters are determined.<br />

However, because of the properties of a MOS capacitance, it is essential to ensure that, when<br />

the gate-drain voltage is negative, there is a constant capacitance COX. This is achieved by<br />

the auxiliary circuit with the two MOSFETs M2 and M3, which switch in the barrier-layer<br />

capacitance of the diode DGD when the drain-gate voltage is positive and the constant<br />

capacitance COX when the drain-gate voltage is negative. Initially, the value of the parameter<br />

COX is the gate-drain capacitance at Ugd = 0V. The MOSFET parameters <strong>for</strong> M2 and M3<br />

must be set so that the MOSFETs switch on in the region of 0V and then exhibit a low<br />

resistance. Dynamic parameters are not transfered to these MOSFETs.<br />

e) Parameters from transient measurements, the transit time TT<br />

In reverse operation of the MOSFET, charge carriers are injected into the reverse diode. For<br />

this case, it is necessary to determine the parameter TT of the <strong>SPICE</strong> diode in order to be<br />

able to describe the decay of charge carriers after recommutation of the diode. The<br />

parameter TT is determined by measuring the carrier charge at the reverse diode.<br />

6 AN_M1.DOC

Power Semiconductor Application Note AN_PSM1e<br />

f) The lead inductances LG, LS, LD<br />

Intrinsic component inductances are determined by measuring the lengths and cross-sections<br />

of the leads and then calculating the self-inductance, as derived in text books.<br />

The parameter extraction method outlined here provides a simple way of determining the<br />

parameter values needed <strong>for</strong> modelling the subcircuit.<br />

The next section shows that, with the parameters determined, the <strong>SIPMOS</strong> power transistor model<br />

presented here is capable of correctly simulating both the measurement results of the parameter<br />

extraction circuits and an inverter circuit with inductive load.<br />

4) Limits of the model<br />

The simplified approach to <strong>SPICE</strong> modelling of <strong>SIPMOS</strong> transistors comes up against its limits<br />

when the model is operated in a circuit in a range in which, in reality, the avalanche breakdown of<br />

the reverse diode occurs. None of the phenomena that lie beyond the exponential rise of the<br />

reverse blocking current, such as the activation of the parasitic bipolar transistor (not shown on the<br />

cross-section), are reproduced by the <strong>SPICE</strong> simulation. Moreover, the effect of component<br />

temperature rise is not taken into account. This problem can be tackled by including in the <strong>SPICE</strong><br />

model parameters determined at a higher temperature.<br />

5) Modelling examples<br />

The procedure <strong>for</strong> simulating typical circuits is explained below using a number of examples. First<br />

the DC output characteristics are simulated, then transient characteristics are determined in some<br />

standard circuits. Finally a DC chopper converter circuit is simulated in order to demonstrate how<br />

powerful these models are.<br />

i) Simulation of the output characteristic<br />

Standard setup with drain-source voltage sweep and the gate voltage as a parameter.<br />

The gate and the drain of the model network are connected to separate power supplies. This is the<br />

simplest test circuit.<br />

Fig. 7: Test circuit to simulate the output and transfer characteristics<br />

When simulating the output characteristic and the transfer characteristic, only the DC card is used<br />

<strong>for</strong> simulation control. The output and transfer characteristics are simulated in a range which<br />

corresponds to the range of application of the measurements. With suitably prepared measurement<br />

data, the result of the simulation is comparable to the result obtained by measurement.<br />

7 AN_M1.DOC

Power Semiconductor Application Note AN_PSM1e<br />

Fig. 8: Comparison of simulation and measurement, using the example of the<br />

output characteristic field at different gate voltages of the BUZ41AL<br />

(IS-<strong>SPICE</strong> result)<br />

ii) Gate charge<br />

Simulation of the measurement circuit as shown in the data book<br />

A transient simulation is demonstrated using the gate charge simulation. The essential parts of<br />

the measurement circuit in the simulation correspond to the actual measurement setup. This<br />

permits direct comparison of the simulated and the measured results when the simulation is<br />

complete. The component used in this measurement circuit is the BUZ 12 AL.<br />

Fig. 9: Measurement circuit <strong>for</strong> determining the behaviour of the gate<br />

voltage<br />

<strong>for</strong> operation with constant load current and constant gate control.<br />

The equivalent circuit shown here reveals an essential point <strong>for</strong> the simulation of complex<br />

circuits. The circuit to be simulated is first reduced to its essential elements.<br />

The simulation parameters which determine the accuracy of calculation <strong>for</strong> current, voltage and<br />

charge (abstol = tolerance on calculation of the absolute current, vntol = tolerance on calculation<br />

of absolute voltage and chgtol = tolerance on calculation of absolute charge) are then adapted to<br />

the problem. This step calls <strong>for</strong> a certain amount of caution and experience.<br />

8 AN_M1.DOC

Power Semiconductor Application Note AN_PSM1e<br />

The last step is the definition of the transient control instruction, in which both the final value and<br />

the time control step width are set.<br />

Fig. 10: Result of gate charge simulation (1) on the BUZ12AL and comparison with<br />

the measured gate charge curve (2)<br />

iii) Inverter with inductive load<br />

This case shows how a <strong>SIPMOS</strong>-<strong>SPICE</strong> model is used in a DC chopper converter circuit.<br />

In such a circuit, an inductive load is charged to a particular value of current via the pulse control<br />

factor. During the „off“-phases of the switching transistor the inductive load drives the current<br />

through a second transistor connected as a free-wheeling diode.<br />

BUZ12AL<br />

BUZ12AL<br />

Fig. 11: DC chopper converter circuit with BUZ12AL<br />

One result of simulating the starting of a DC chopper converter circuit is shown in Fig. 12. As<br />

expected, the current (curve 0) rises with time in accordance with the coil values. At the same<br />

time, the drain-source voltage of the switched-on MOSFET increases. The power dissipation<br />

could thus be calculated from the two curves, leading to an estimate of the temperature rise of<br />

the component.<br />

This simulation also requires the simulation parameters <strong>for</strong> current, voltage and charge (abstol,<br />

vntol and chgtol) to be set under the conditions mentioned above.<br />

9 AN_M1.DOC

Appendix:<br />

Power Semiconductor Application Note AN_PSM1e<br />

time in sec<br />

Fig. 12: Coil current (0) and drain-source voltage (2) in a DC chopper converter<br />

circuit as in Fig. 11<br />

Note: The voltage peak in the simulation results from a numerical instability<br />

a) Subcircuit of BUZ12AL (high-current MOSFET)<br />

.SUBCKT BUZ12AL 1 2 3 */ 1:Gate 2: Source 3:Drain /*<br />

LS 5 2 7N<br />

LD 83 3 5N<br />

RG 4 11 5.5M<br />

RS 5 76 40M<br />

D12AL 76 83 DREV<br />

.MODEL DREV D CJO=2.925N RS=20M TT=500N IS=300P BV=50<br />

M12AL 71 11 76 76 MBUZ<br />

.MODEL MBUZ NMOS VTO=2.12 KP=24.66<br />

M2 11 71 8 8 MSW<br />

.MODEL MSW NMOS VTO=0.001 KP=10<br />

M3 71 11 8 8 MSW<br />

COX 11 8 5.194N<br />

DGD 8 71 DCGD<br />

.MODEL DCGD D CJO=5.194N M=0.516 VJ=0.072<br />

CGS 76 11 2.1N<br />

RDR 71 83 10M<br />

LG 4 1 7N<br />

.ENDS<br />

b) Subcircuit of BUZ41A (high-voltage MOSFET)<br />

.SUBCKT BUZ41A 1 2 3 */ 1:Gate 2: Source 3:Drain /*<br />

LS 5 2 7N<br />

LD 87 3 5N<br />

RG 4 11 5.5M<br />

RS 5 76 34M<br />

D41A 76 87 DREV<br />

.MODEL DREV D CJO=420P RS=20M TT=500N IS=300P BV=500<br />

M41A 86 11 76 76 MBUZ<br />

.MODEL MBUZ NMOS VTO=3.313 KP=7.66<br />

M2 11 86 8 8 MSW<br />

.MODEL MSW NMOS VTO=0.001 KP=10<br />

M3 86 11 8 8 MSW<br />

10 AN_M1.DOC

Power Semiconductor Application Note AN_PSM1e<br />

COX 11 8 2.5N<br />

DGD 8 86 DCGD<br />

.MODEL DCGD D CJO=250P M=0.675 VJ=1.301<br />

CGS 76 11 870P<br />

MDR 87 86 86 86 MVRD<br />

.MODEL MVRD NMOS VTO=-13.1 KP=0.068<br />

LG 4 1 7N<br />

.ENDS<br />

c) Subcircuit of BSP149 (n-channel depletion MOSFET)<br />

SUBCKT BSP149 1 2 3 */ 1:Gate 2: Source 3:Drain /*<br />

LG 95 1 7N<br />

LS 5 2 7N<br />

LD 97 3 5N<br />

RG 95 99 5.5M<br />

RS 5 76 578M<br />

D149 76 97 DREV<br />

.MODEL DREV D CJO=0.03N RS=20M TT=35N IS=300P BV=200<br />

M149 98 99 76 76 MBUZ<br />

.MODEL MBUZ NMOS VTO=-1.334 KP=1.022<br />

M2 87 98 8 8 MSW<br />

.MODEL MSW NMOS VTO=0.001 KP=5<br />

M3 98 87 8 8 MSW<br />

COX 87 8 0.08N<br />

DGD 8 98 DCGD<br />

.MODEL DCGD D CJO=59P M=0.542 VJ=0.979<br />

CGS 76 99 225P<br />

VGC 87 99 3<br />

MHELP 98 98 97 98 MVRD<br />

.MODEL MVRD NMOS VTO=-16.18 KP=0.34<br />

.ENDS<br />

d) Control instruction <strong>for</strong> transient simulation of the DC chopper converter<br />

* Width and final value of time step<br />

.TRAN 10U 2M<br />

* Parameters <strong>for</strong> transient analysis and calculation accuracy <strong>for</strong> voltage (vntol), current<br />

(abstol) and charge (chgtol)<br />

.OPTIONS LIMPTS=5000 ITL1=2000 ITL4=1200 ITL5=150000<br />

+ VNTOL=1M ABSTOL=1U CHGTOL=10P<br />

11 AN_M1.DOC