Representación simbólica Diagrama de Sticks Diagrama de Sticks ...

Representación simbólica Diagrama de Sticks Diagrama de Sticks ...

Representación simbólica Diagrama de Sticks Diagrama de Sticks ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

DMI <strong>Representación</strong> <strong>simbólica</strong> – A. Diéguez<br />

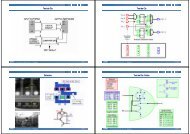

<strong>Representación</strong> <strong>simbólica</strong><br />

A B<br />

Diseño a nivel <strong>de</strong> transistor Diseño a nivel físico<br />

A B<br />

DMI <strong>Representación</strong> <strong>simbólica</strong> – A. Diéguez<br />

<strong>Diagrama</strong> <strong>de</strong> <strong>Sticks</strong><br />

VDD<br />

Y<br />

GND<br />

Pozo n<br />

Difusión n+<br />

Polisilicio<br />

Difusión p+<br />

Metal1<br />

Contacto<br />

VDD<br />

Y<br />

GND<br />

A B<br />

El diagrama <strong>de</strong> sticks refleja la topología <strong>de</strong>l diseño<br />

físico pero abstrae las reglas <strong>de</strong> diseño<br />

VDD<br />

Y<br />

GND<br />

Pozo n<br />

Difusión n+<br />

Polisilicio<br />

Difusión p+<br />

Metal1<br />

Contacto<br />

DIAGRAMA DE STICKS<br />

N-diff<br />

P-diff<br />

poly<br />

metal1<br />

metal2<br />

contact<br />

DMI <strong>Representación</strong> <strong>simbólica</strong> – A. Diéguez<br />

GRAFO DE EULER<br />

C<br />

C D<br />

B<br />

A<br />

VDD<br />

DMI <strong>Representación</strong> <strong>simbólica</strong> – A. Diéguez<br />

I 1<br />

I 2<br />

I3 D A B<br />

Z<br />

<strong>Diagrama</strong> <strong>de</strong> <strong>Sticks</strong><br />

1 2 3<br />

4<br />

Grafos <strong>de</strong> Euler<br />

5<br />

VDD<br />

VDD<br />

IN IN<br />

OUT<br />

OUT<br />

INVERSOR INVERSOR CMOS<br />

CMOS<br />

A<br />

GND<br />

GND<br />

B D C<br />

V dd<br />

out<br />

Gnd

DMI <strong>Representación</strong> <strong>simbólica</strong> – A. Diéguez<br />

Grafos <strong>de</strong> Euler<br />

Reglas prácticas para la disposición <strong>de</strong> transistores (layout compacto)<br />

Transistores en filas ininterrumpidas para po<strong>de</strong>r hacer comunes regiones D/S<br />

Conexiones <strong>de</strong> puerta nMOS y pMOS <strong>de</strong> la misma entrada alineadas verticalmente<br />

Metodología<br />

Construir el gráfico lógico<br />

Vértices correspon<strong>de</strong>n a nodos <strong>de</strong>l circuito<br />

Líneas correspon<strong>de</strong>n a transistores<br />

Líneas rotuladas con el nombre <strong>de</strong> la señal que controla el transistor<br />

Vértices rotulados con la tensión <strong>de</strong>l nodo correspondiente en el circuito<br />

I<strong>de</strong>ntificar los caminos <strong>de</strong> Euler<br />

Caminos que pasan por todos los vértices <strong>de</strong>l gráfico pasando por las<br />

líneas una sola vez<br />

Encontrar caminos <strong>de</strong> Euler iguales en la red pMOS y en la red nMOS<br />

Disponer las entradas (poly) <strong>de</strong> acuerdo al camino establecido<br />

DMI <strong>Representación</strong> <strong>simbólica</strong> – A. Diéguez<br />

DMI <strong>Representación</strong> <strong>simbólica</strong> – A. Diéguez DMI <strong>Representación</strong> <strong>simbólica</strong> – A. Diéguez<br />

Reglas <strong>de</strong> diseño<br />

Layout <strong>de</strong>l Inversor CMOS

Algunas reglas para diseño Full-Custom<br />

DMI <strong>Representación</strong> <strong>simbólica</strong> – A. Diéguez<br />

Algunas reglas para diseño Full-Custom<br />

DMI <strong>Representación</strong> <strong>simbólica</strong> – A. Diéguez<br />

Algunas reglas para diseño Full-Custom<br />

DMI <strong>Representación</strong> <strong>simbólica</strong> – A. Diéguez<br />

Algunas reglas para diseño Full-Custom<br />

DMI <strong>Representación</strong> <strong>simbólica</strong> – A. Diéguez