Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

DMI C ircuitos sec uenciales – A. Diéguez<br />

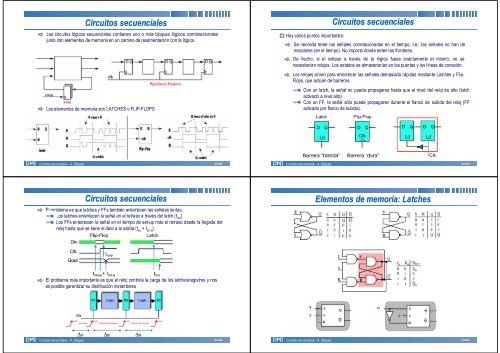

Circuitos secuenciales<br />

Los circuitos lógicos secuenciales contienen uno o más bloques lógicos combinacionales<br />

junto con elementos de memoria en un camino de realimentación con la lógica.<br />

Los elementos de memoria son LATCHES o FLIP-FLOPS<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Circuitos secuenciales<br />

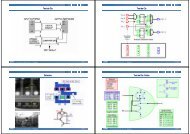

El problema es que latches y FFs también enlentecen las señales lentas.<br />

Los latches enlentecen la señal en el retraso a través del latch (t d-q ).<br />

Los FFs enlentecen la señal en el tiempo de set-up más el retraso desde la llegada del<br />

reloj hasta que se tiene el dato a la salida (t su + t ck-q ).<br />

El problema más importante es que el reloj controla la carga de los latches/registros y nos<br />

es posible garantizar su distribución instantánea<br />

Hay varios puntos importantes:<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Circuitos secuenciales<br />

Se necesita tener las señales correlacionadas en el tiempo, I.e., las señales no han de<br />

mezclarse (en el tiempo). No importa donde esten las fronteras.<br />

De hecho, si el retraso a través de la lógica fuese exáctamente el mismo, no se<br />

necesitarían relojes. Los estados se almacenarían en las puertas y las líneas de conexión.<br />

Los relojes sirven para enlentecer las señales demasiado rápidas mediante <strong>Latches</strong> y Flip-<br />

Flops, que actúan de barreras.<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Con un latch, la señal no puede propagarse hasta que el nivel del reloj es alto (latch<br />

activado a nivel alto)<br />

Con un FF, la señal sólo puede propagarse durante el flanco de subida del reloj (FF<br />

activado por flanco de subida).<br />

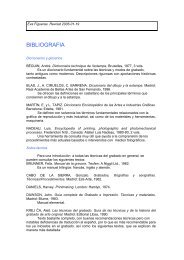

Elementos de memoria: <strong>Latches</strong>

DMI C ircuitos sec uenciales – A. Diéguez<br />

Elementos de memoria: <strong>Latches</strong><br />

Los elementos de memoria en sistemas VLSI son LATCHES o FLIP-FLOPS tipo D<br />

D LATCH/FF significa Delay: Un FF D retrasa la señal (dato) un cliclo de reloj<br />

El latch más simple tipo D:<br />

Almacena un 1 o un 0 en una capacidad<br />

Interruptor cerrado: la capacidad se carga a la señal de entrada<br />

Interruptor abierto: la capacidad mantiene el valor<br />

Posible implementación:<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Elementos de memoria: <strong>Latches</strong><br />

El inversor C2MOS (Clocked-inverter):<br />

El inversor C2MOS es un híbrido entre una TG y un INV<br />

E flota cuando el reloj φ está bajo<br />

E invierte la entrada E cuando el reloj φ está alto<br />

El latch C2MOS (Clocked-inverter):<br />

14 transistores<br />

φ=‘1’: G1 está ‘on’, el latch es transparente. La señal D viaja DXq<br />

φ =‘0’: G2 está ‘on’. El latch almacena XqX formando un bucle no inversor<br />

Layout más simple<br />

No hay puerta de paso a la entrada<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Elementos de memoria: <strong>Latches</strong><br />

El latch estático tipo D:<br />

Utiliza realimentación para almacenar, no una capacidad<br />

Puede recordar mientras se mantenga la alimentación<br />

La capacidad sólo es necesaria para recordar el valor durante la conmutación<br />

CLOCK=‘1’: La señal de entrada pasa a la salida Q (el latch es transparente)<br />

CLOCK=‘0’: La última entrada determina Q<br />

Posible implementación:<br />

12 transistores<br />

Hay una degradación del<br />

t setup debido a la puerta de<br />

transmisión<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Elementos de memoria: <strong>Latches</strong><br />

El MUX D-LATCH<br />

Es simplemente un multiplexor<br />

CLOCK=‘1’: D pasa a Q<br />

CLOCK=‘0’: Q se mantiene a través del camino de realimentación<br />

Implementado con puertas tiene 12 transistores + 2 del buffer de salida<br />

Si C y !C tienen retrasos diferentes se produce un glitch<br />

La entrada es buffered: tiempo de setup aislada de la impedancia de salida de la etapa<br />

anterior

DMI C ircuitos sec uenciales – A. Diéguez<br />

Elementos de memoria: <strong>Latches</strong><br />

El MUX D-LATCH: implementación alternativa<br />

Timming:<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Elementos de memoria: Flip-Flops<br />

Flip Flops<br />

Mayoritariamente basados en estructuras Master-Slave (tipo D en sistemas VLSI)<br />

Implementación: 2 latches D en serie, uno con CLK y el otro con CLK<br />

Operación:<br />

MASTER transparente, SLAVE en hold<br />

MASTER en hold, SLAVE transparente<br />

Como siempre hay un latch en modo hold, el FF nunca es transparente.<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Elementos de memoria: <strong>Latches</strong><br />

Alternativas dinámicas:<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Elementos de memoria: Flip-Flops<br />

Flip Flops<br />

Efectivamente, es edge-triggered (activado por flanco)<br />

El dato que entra en D justo antes de la caida del clock, llega a Q tras el flanco de bajada del reloj<br />

Todos los FF D master-slave son activados por flanco, pero no todos los FF D activados por<br />

flanco son master-slave<br />

Símbolo D-FF:

DMI C ircuitos sec uenciales – A. Diéguez<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Elementos de memoria: Flip-Flops<br />

Flip Flops<br />

Elementos de memoria: Flip-Flops<br />

Flip Flops<br />

El Enabled D Flip-Flop<br />

A menudo se necesita mantener un dato varios ciclos de reloj<br />

En ocasiones se necesita eliminar datos indeseados de las entradas<br />

¿Por qué no desactivar el reloj estas ocasiones?<br />

Poner puertas para inhabilitar el reloj provoca Clock Skew:<br />

Otras razones para no inhabilitar el reloj con puertas (gating the clock)<br />

Puede causar falsos flancos de reloj si SIT cambia cuando CLK=1<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Elementos de memoria: Flip-Flops<br />

Flip Flops<br />

Elementos de memoria: Flip-Flops<br />

Flip Flops<br />

El Enabled D Flip-Flop<br />

Es una forma simple de eliminar el problema de inhabilitar el reloj con puertas<br />

Conmuta la entrada D del flip-flop entre la antigua Q y la nueva entrada<br />

Operación:<br />

ENABLE=1: la entrada introducida en el flip-flop<br />

ENABLE=0: Q se recarga en la entrada desde la salida<br />

Aplicación:<br />

El enable permite al flip-flop mantener el dato estable tanto tiempo como se desea sin<br />

poner puertas en la entrada del reloj

DMI C ircuitos sec uenciales – A. Diéguez<br />

Propiedades temporales de los FFs<br />

Tiempos de setup y de hold<br />

Los FFs tienen regisones restringidas cerca del flanco activo del reloj<br />

Si D cambia en estas regiones, Q es indefinido<br />

Q puede: ser el último valor de D; el nuevo D, tomar un nivel medio (~VDD/2)<br />

Los FFs actuales tienen un hold time nulo o negativo.<br />

El dato puede cambiar antes del flanco y ser capturado<br />

El diseño (del sistema) se simplifica<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Propiedades temporales de los FFs<br />

Tiempo de propagación, tc-q Es el retraso de un cambio de Q respecto al flanco de reloj activo<br />

Los diseñadores han de hacer t c-q > t hold<br />

La señal de salida de un FF es siempre síncrona<br />

si t c-q > t hold (incluso si D no lo es ya que Q sólo cambia por acción del reloj)<br />

t c-q desplaza los cambios deQ fuera de la región restringida para el siguiente FF<br />

(si algo produce un retraso despues del FF no tiene porque cumplirse)<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Propiedades temporales de los FFs<br />

Señales síncronas y asíncronas<br />

Síncrona: si no cambia en la región restringida<br />

Asíncrona: puede cambiar en cualquier sitio<br />

Las señales asíncronas pueden generarse cuando:<br />

Vienen de fuera del CI<br />

Vienen de un circuito controlado por otro reloj<br />

Señales generadas usando el reloj con algo más<br />

que latches o flip-flops. Ej: clock gating<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Propiedades temporales de los FFs<br />

Tiempo de ciclo (periodo)<br />

En un circuito secuencial generalmente hay lógica entre FFs<br />

Existe un periodo mínimo del reloj (o un tiempo máximo de propagación en la lógica)<br />

Esta es la principal restricción temporal en circuitos digitales.<br />

Si no se cumple se denomina violación de tiempo de setup

Tiempo de hold<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Propiedades temporales de los FFs<br />

Existe un tiempo m ínimo para la propagación de la lógica: Ocurre si t c-q < t hold<br />

Considerad 2 FFs con el mismo reloj. Para un tiempo grande de hold el FF1 puede<br />

cambiar de estado y enviar su nueva salida al FF2 de forma que ambos conmuten en el<br />

mismo flanco.<br />

Para evitar dobles conmutaciones:<br />

Dicho de otra forma, el mínimo tiempo de propagación en la logica es:<br />

Si no se cumple se denomina violación de tiempo de hold. Máximo peligro en shift Regs.<br />

Clock skew<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Clock skew<br />

Cuando el flanco del reloj no alcanza a todos los FFs al mismo tiempo<br />

Skew positivo<br />

Los datos y el reloj se retrasan en la misma dirección.<br />

Skew negativo<br />

Los datos y el reloj se retrasan en direcciones opuestas<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Propiedades temporales de los FFs<br />

Tiempo de hold, visión alternativa<br />

El mínimo retraso aparece cuando t c-q < t hold<br />

En este caso D1 puede provocar Q1 en el FF1 y viajar a través de la lógica y alcanzar el<br />

FF2 dentro de su tiempo de hold. El FF2 puede, por tanto, cambiar en el mismo flanco.<br />

Los prolemas de hold pueden solucionarse insertando un par de inversores en la lógica<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Incertidumbre en el reloj<br />

4 Power Supply<br />

3 Interconnect<br />

2<br />

Devices<br />

1 Clock Generation<br />

5 Temperature<br />

6 Capacitive Load<br />

7 Coupling to Adjacent Lines<br />

Retar do en una conex ión del reloj

DMI C ircuitos sec uenciales – A. Diéguez<br />

Clock skew<br />

Efecto del skew en el máximo tiempo de propagación<br />

El skew positivo incrementa el periodo efectivo del reloj (hay más tiempo para alcanzar FF2)<br />

El skew positivo incrementa t PD(MAX) en el skew<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Clock skew<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Clock skew<br />

Efecto del skew en el mínimo tiempo de propagación<br />

El skew positivo equivale a aumentar el tiempo de hold del FF2<br />

El mínimo retraso de la lógica, t PD(MIN) , necesario para evitar la región restringida aumenta<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Clock skew

CLK<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

DEC Alpha 21164<br />

300 MHz<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Distribución del reloj<br />

Distribución de arbol en H<br />

Ejemplos de redes de distribución<br />

EV6 (Alpha 21264)<br />

600 MHz – 0.35 micron CMOS<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

DMI C ircuitos sec uenciales – A. Diéguez<br />

Distribución del reloj<br />

Esquema de buffers distribuidos en áreas locales<br />

Esquema del reloj en un sistema de dos fases<br />

Con dos fases no solapadas, flancos distintos guardan los datos y modifican la salida<br />

Generación:<br />

Clk<br />

Phase 1<br />

Phase 2<br />

100